# CA-IF428x Home Bus System (HBS) Compatible Transceiver

#### 1. Features

- Configurability Enables Flexible Design

- 9.6kbps to 200kbps Data Rate

- Adjustable Receiver Thresholds and Internal Threshold Configuration Option

- Large Receiver Hysteresis

- Adjustable Slew Rate on Transmit Signals

- Dynamic Cable Termination Improves Signal Quality for High-Speed Communication

- Support Bus Polarity Detection (CA-IF4289 only)

- Integrated Protection for Robust Communication

- IEC 61000-4-2 ±8kV Contact and ±15kV Air-Gap ESD Protection

- IEC 61000-4-5 ±1kV Surge Protection with Selected External Components

- Compact 4mm\*4mm QFN Package

- Operation temperature range from -40°C to +105°C

#### 2. Applications

- HVAC

- Data over Power Applications (PoD)

- Digital Signage

- Industrial PLC

- Remote Monitoring and Sensing

#### 3. General Description

The CA-IF428x family of devices complies with the home bus standard requirements while improving communication in harsh environments and minimizing the need for external components. The home bus standard was designed to ease communication between multiple different devices connected to a single bus, where data and power are passed on one single pair of wires, to allow a mutual exchange of information at any time from any room in a home or building among various appliances, equipment, or security devices.

The CA-IF428x family is configurable to operate up to 200kbps with adjustable receiver thresholds and dynamic cable termination for improved communication with high data rates. This family of devices is rated for operation up to  $\pm 8$ kV contact discharge and  $\pm 15$ kV air gap ESD protection, and survives up to  $\pm 1$ kV surge events with selected external components. Additional features include adjustable receiver hysteresis and driver slew rate. Also, the CA-IF4289 features bus polarity detection, help to prevent incorrect bus connections. The CA-IF428x devices have been designed for operation in home bus systems but they are not only limited to those networks, can be used to transmit data over any compatible system.

All devices are specified over the -40°C to +105°C operating temperature range and are available in a compact 24-pin 4mm\*4mm QFN package.

#### **DEVICE INFORMATION**

| Part Number | Package | Package Size |

|-------------|---------|--------------|

| CA-IF4288   | QFN24   | 4mm*4mm      |

| CA-IF4289   | QFN24   | 4mm*4mm      |

#### 4. Ordering Information

#### Table 4-1. Ordering Information

| Part Number | Temperature Range | Package       |

|-------------|-------------------|---------------|

| CA-IF4288   | -40°C to +105°C   | QFN24 4mm*4mm |

| CA-IF4289   | -40°C to +105°C   | QFN24 4mm*4mm |

# Contents

| 1. |      | Featu  | es                                   | 1  |

|----|------|--------|--------------------------------------|----|

| 2. |      | Applic | ations                               | 1  |

| 3. |      | Gener  | al Description                       | 1  |

| 4. |      | Order  | ing Information                      | 2  |

| 5. |      | Simpli | fied Block Diagram                   | 4  |

|    | 5.1. |        | F4288 simplified Block Diagram       |    |

|    | 5.2. |        | F4288 simplified Block Diagram       |    |

| 6. |      | Pin Co | nfiguration                          | 6  |

| 7. |      |        | ications                             |    |

|    | 7.1. | Abso   | olute Maximum Ratings <sup>1</sup>   | 8  |

|    | 7.2. | ESD    | Rating                               | 8  |

|    | 7.3. | Reco   | ommended Operating Conditions        | 8  |

|    | 7.4. | The    | mal Information                      | 8  |

|    | 7.5. | Elec   | trical Characteristics               | 9  |

|    |      | 7.5.1. | DC characteristics(V <sub>CC</sub> ) |    |

|    |      | 7.5.2. | DC characteristics /Transmit Channel |    |

|    |      | 7.5.3. | DC characteristics /Receive Channel  |    |

|    |      | 7.5.4. | DC characteristics/Digital I/O       |    |

|    |      | 7.5.5. | AC characteristics/Transmit channel  |    |

|    |      | 7.5.6. | AC characteristics/Receive channel   |    |

|    |      | 7.5.7. | Bus polarity detection <sup>1</sup>  | 10 |

|     | 7.6. | Турі   | cal Characteristics and Waveforms. | 11  |

|-----|------|--------|------------------------------------|-----|

| 8.  |      | Param  | neter Measurement Informatior      | າ12 |

| 9.  |      | Detail | ed Description                     | 13  |

|     | 9.1. | Tran   | sceiver Operation                  | 14  |

|     | 9.2. | Tran   | smitter Control and Configuration. | 15  |

|     |      | 9.2.1. | Dynamic Cable Termination          | 15  |

|     |      | 9.2.2. | Transmit Slew Rate Adjustment      | 16  |

|     |      | 9.2.3. | RST (Reset) Control                | 16  |

|     |      | 9.2.4. | Data Input Timeout Detection       | 16  |

|     | 9.3. | Rece   | eiver Control and Configuration    | 16  |

|     |      | 9.3.1. | Receiver Threshold Adjustment      | 16  |

|     |      | 9.3.2. | High-Pass Filter                   | 17  |

|     | 9.4. | Bus    | Polarity Detection                 | 17  |

| 10. |      | Applic | cation and Implementation          | 17  |

|     | 10.1 | . Surg | ge Protection                      | 17  |

|     | 10.1 | . PCB  | Layout Recommendations             | 17  |

| 11. |      | Packa  | ge Information                     | 20  |

| 12. |      | Solde  | ring Temperature (reflow) Profil   | e21 |

| 13. |      | Tape a | and Reel Information               | 22  |

| 14. |      | IMPO   | RTANT NOTICE                       | 23  |

#### **Revision History**

| <b>Revision Number</b> | Description                                                                                                                                                                                 | Page Changed                  | Revision Date |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------|

| Version 1.00           | N/A                                                                                                                                                                                         | N/A                           | 2022/01/19    |

| Version 1.01           | Changed CA-IF4288 pin 20 definition, HPEN to NC.                                                                                                                                            | 4, 6, 7, 14, 16               | 2022/04/19    |

| Version 1.02           | <ol> <li>Added Soldering Temperature Profile and Tape and Reel<br/>Information section.</li> <li>Changed HBM ESD rating from ±4kV to ±6kV.</li> <li>Changed package name to QFN.</li> </ol> | 19, 20, 6<br>1, 2, 18, 19, 20 | 2022/11/29    |

| Version 1.03           | 4. Updata the test condition of $V_{LEAD}$ and $V_{TRAIL}$                                                                                                                                  | 7                             | 2024/03/27    |

### CA-IF4288, CA-IF4289 Version 1.03

Shanghai Chipanalog Microelectronics Co., Ltd.

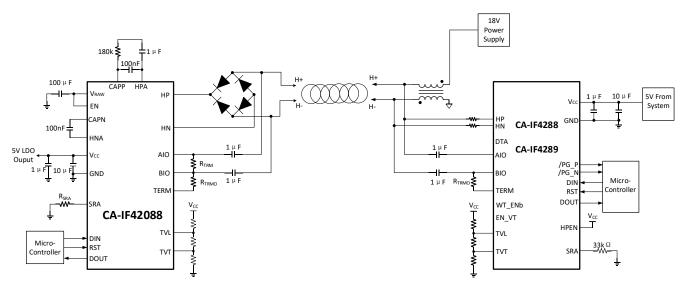

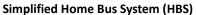

5. Simplified Block Diagram

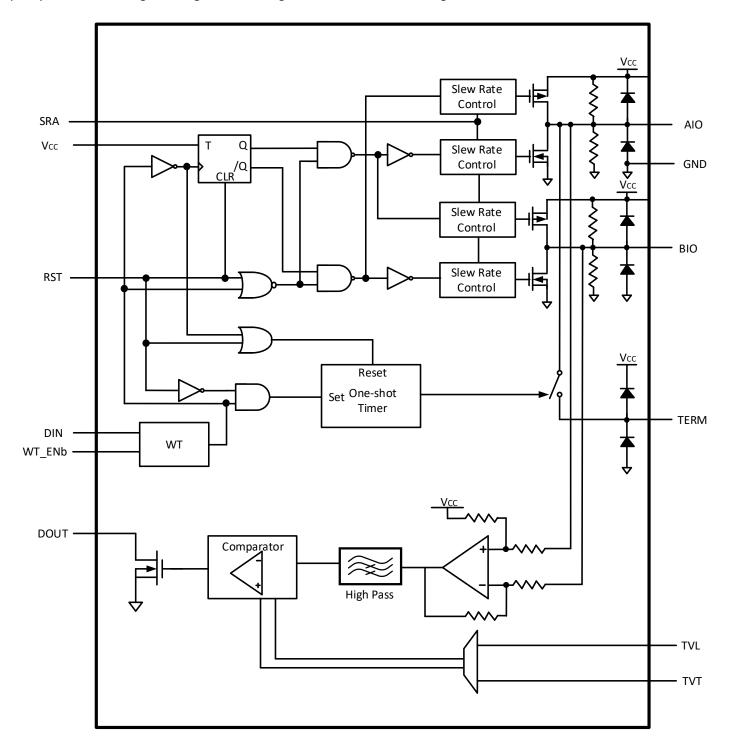

#### 5.1. CA-IF4288 simplified Block Diagram

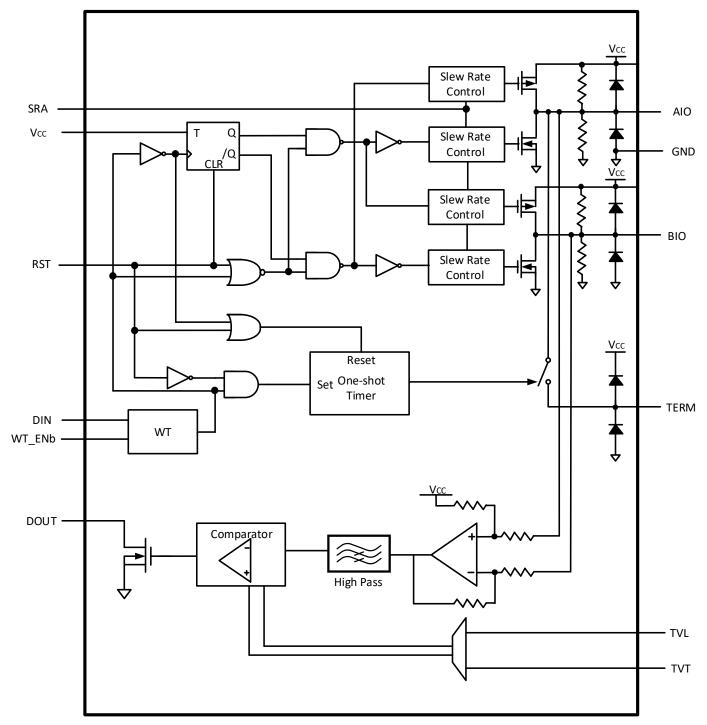

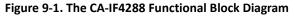

# 5.2. CA-IF4288 simplified Block Diagram

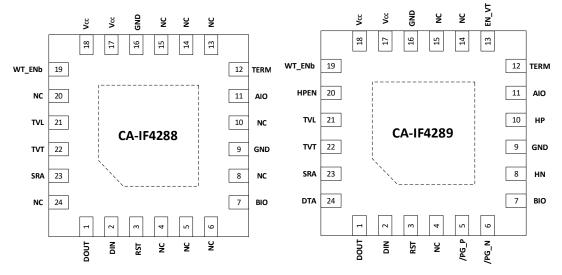

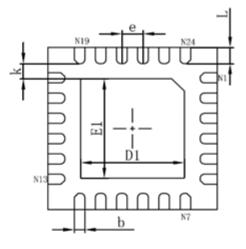

### 6. Pin Configuration

Figure 6-1. CA-IF4288 / 4289 Pin Configuration

|       | PIN NUMBER                |           | TVDE        | DECONDENSION                                                                                                                                                                                         |

|-------|---------------------------|-----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | CA-IF4288                 | CA-IF4289 | ΤΥΡΕ        | DESCRIPTION                                                                                                                                                                                          |

| DOUT  | 1                         | 1         | LOGIC I/O   | Data output, open-drain output. Connect an external pull-up resistor to the logic voltage supply.                                                                                                    |

| DIN   | 2                         | 2         | logic I/o   | Data input.                                                                                                                                                                                          |

| RST   | 3                         | 3         | LOGIC I/O   | Bus reset control input.                                                                                                                                                                             |

| N.C.  | 4,5,6,8,10,13,14,15,20,24 | 4,14,15   | -           | Not connected.                                                                                                                                                                                       |

| /PG_P | -                         | 5         | logic I/O   | Open-drain output, active low when bus polarity is positive ( $V_{HP}$ - $V_{HN}$ > 3V).                                                                                                             |

| /PG_N | -                         | 6         | logic I/O   | Open-drain output, active low when bus polarity is negative $(V_{HN}-V_{HP} > 3V)$ .                                                                                                                 |

| BIO   | 7                         | 7         | HOME<br>BUS | Home bus data input and output. Connect BIO to home bus through a $1\mu$ F capacitor in series with a $4.7\Omega$ resistor for 57.6kbps operation.                                                   |

| HN    | -                         | 8         | HOME<br>BUS | Home bus interface. Connect a 200 $\Omega$ resistor between HN and home bus for surge protection.                                                                                                    |

| GND   | 9, 16                     | 9, 16     | GND         | Ground.                                                                                                                                                                                              |

| HP    | -                         | 10        | HOME<br>BUS | Home bus interface. Connect a 200 $\Omega$ resistor between HN and home bus for surge protection.                                                                                                    |

| AIO   | 11                        | 11        | HOME<br>BUS | Home bus data input and output. Connect BIO to home bus through an external $1\mu F$ capacitor in series with a $4.7\Omega$ resistor for 57.6kbps operation.                                         |

| TERM  | 12                        | 12        | HOME<br>BUS | Switched bus termination. Connect a resistor between TERM and BIO to adjust home bus cable termination for better signal quality.                                                                    |

| EN_VT | -                         | 13        | logic I/o   | Enable control for internal threshold configuration, active high. Connect EN_VT to GND through an $1M\Omega$ pull-down resistor. Leave the pin floating to disable internal threshold configuration. |

| Vcc   | 17, 18                    | 17, 18    | POWER       | Power supply input. Connect +5V to $V_{CC}$ , and bypass $V_{CC}$ to GND with at least 1µF ceramic capacitor as close to the device as possible.                                                     |

#### Table 6-1. CA-IF4288/ 4289 Pin Description

| NAME   | PIN NUMBER |           | ТҮРЕ        | DESCRIPTION                                                                                                                                                                                                                                                                                                          |

|--------|------------|-----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | CA-IF4288  | CA-IF4289 | ITPE        | DESCRIPTION                                                                                                                                                                                                                                                                                                          |

| WT_ENb | 19         | 19        | logic I/O   | Enable control for data input timeout protection, active low. Connect WT_ENb to GND through an $180k\Omega$ pull-down resistor. Leave the pin floating to disable timeout detection.                                                                                                                                 |

| HPEN   | -          | 20        | LOGIC       | High pass filter enable input. Connect HPEN to $V_{CC}$ to enable the internal high pass filter on the receiver input. Connect HPEN to GND to disable the internal high pass filter. Do not leave HPEN open.                                                                                                         |

| TVL    | 21         | 21        | HOME<br>BUS | Leading edge data threshold, see the Receiver Threshold Adjustment section for more information.                                                                                                                                                                                                                     |

| TVT    | 22         | 22        | HOME<br>BUS | Trailing edge data threshold, see the Receiver Threshold Adjustment section for more information.                                                                                                                                                                                                                    |

| SRA    | 23         | 23        | LOGIC       | Slew rate control input. Connect SRA to GND through a resistor to adjust the slew rate of AIO and BIO data output edges.                                                                                                                                                                                             |

| DTA    | -          | 24        | LOGIC       | Dynamic termination time adjustment. For the CA-IF4289,<br>Connect DTA to GND through a $10k\Omega$ to $500k\Omega$ resistor to<br>adjust the dynamic termination turn on time; Leave DTA<br>floating, the dynamic termination time is default of 34µs. For<br>the CA-IF4288, the termination time is fixed at 34µs. |

| EP     | -          | -         | -           | Exposed pad, connect to Ground.                                                                                                                                                                                                                                                                                      |

7. Specifications

#### 7.1. Absolute Maximum Ratings<sup>1</sup>

| PARAMETERS                                                       | MIN  | MAX     | UNITS |

|------------------------------------------------------------------|------|---------|-------|

| VCC to GND                                                       | -0.3 | 6.0     | V     |

| AIO, BIO, TERM, SRA to GND                                       | -0.3 | Vcc+0.3 | V     |

| HP, HN to GND                                                    | -0.3 | +28     | V     |

| HP to HN and HN to HP                                            | -28  | +28     |       |

| Continuous current into pins of V <sub>CC</sub> , AIO, BIO, TERM | -100 | +100    | mA    |

| Continuous current into all other pins                           | -50  | +50     | mA    |

| Operating Temperature Range                                      | -40  | +105    | °C    |

| Junction Temperature                                             |      | +150    | °C    |

| Storage Temperature Range                                        | -40  | +150    | °C    |

| Soldering Temperature (reflow)                                   |      | +260    | °C    |

Note:

1. The stresses listed under "Absolute Maximum Ratings" are stress ratings only, not for functional operation condition. Exposure to absolute maximum rating conditions for extended periods may cause permanent damage to the device.

#### 7.2. ESD Rating

|                                |                                                                      |                                                                            | VALUE | UNITS |

|--------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------|-------|-------|

|                                | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, AIO, BIO to GND. | ±30                                                                        | kV    |       |

|                                | Flootrostatio                                                        | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all other pins.        | ±6    | kV    |

| V <sub>ESD</sub> Electrostatic | IEC 61000-4-2 air discharge, AIO,BIO,TERM to GND                     | ±15                                                                        | kV    |       |

|                                | discharge                                                            | IEC 61000-4-2 contact discharge, Electrostatic discharge                   | ±8    | kV    |

|                                |                                                                      | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins. | ±2    | kV    |

#### 7.3. Recommended Operating Conditions

|                | PARAMETERS           | MIN | ТҮР | MAX | UNITS |

|----------------|----------------------|-----|-----|-----|-------|

| Vcc            |                      | 4.5 |     | 5.5 | V     |

| Vtvt           |                      |     | 1.5 |     | V     |

| Vtvl           |                      |     | 2.5 |     | V     |

| Rsra           |                      |     | 33k |     | Ohm   |

| T <sub>A</sub> | Ambient temperature  | -40 | 25  | 105 | °C    |

| Tj             | Junction temperature |     |     | 150 | °C    |

#### 7.4. Thermal Information

| PARAMETERS                                                 |  | QFN | UNITS |

|------------------------------------------------------------|--|-----|-------|

| R <sub>0JA</sub> IC Junction-to-Ambient Thermal Resistance |  | 52  | °C/W  |

Over recommended operating conditions,  $T_A = -40^{\circ}$ C to 105°C (unless otherwise noted).

# 7.5.1. DC characteristics(V<sub>cc</sub>)

| Symbol          | Parameter                                       | Test Conditions                        | MIN | ТҮР | MAX | Units |

|-----------------|-------------------------------------------------|----------------------------------------|-----|-----|-----|-------|

| V <sub>CC</sub> | Power supply voltage                            |                                        | 4.5 | 5.0 | 5.5 | V     |

| Icc             | Supply current                                  | Vcc=5.0V, no loading, 57.6kbps, CL=0pF |     | 1.7 | 2.5 | mA    |

| Vuv             | V <sub>cc</sub> undervoltage lockout            | V <sub>CC</sub> voltage falling        | 4.0 | 4.2 | 4.4 | V     |

| VUV_hys         | V <sub>CC</sub> undervoltage lockout hysteresis |                                        |     | 100 |     | mV    |

#### 7.5.2. DC characteristics /Transmit Channel

| Symbol            | Parameter                         | Test Conditions                                                           | MIN     | ТҮР | MAX | UNITS |

|-------------------|-----------------------------------|---------------------------------------------------------------------------|---------|-----|-----|-------|

| V <sub>TOH</sub>  | Output voltage high               | AIO, BIO to GND, Iload=45mA to GND                                        | Vcc-0.6 |     |     | V     |

| V <sub>TOL</sub>  | Output voltage low                | AIO, BIO to GND, $I_{load}$ =45mA to $V_{CC}$                             |         |     | 0.6 | V     |

| R <sub>TERM</sub> | Termination switch on resistance  | TERM to AIO                                                               | 2.5     | 5   | 10  | Ohm   |

| R <sub>IN</sub>   | AIO,BIO transmit input resistance | Input resistance of AIO and BIO when they are unconnected, $DIN{=}V_{CC}$ | 7       | 10  | 13  | ΚΩ    |

| VAIO/ VBIO        | Bias voltage ratio matching       | AIO, BIO unconnected                                                      | -1      |     | +1  | %     |

#### 7.5.3. DC characteristics /Receive Channel

| Symbol              | Parameter                                   | Conditions                                                    | MIN  | ТҮР | MAX  | UNITS |

|---------------------|---------------------------------------------|---------------------------------------------------------------|------|-----|------|-------|

| V <sub>LEAD</sub>   | Receive threshold leading edge              | V <sub>TVL</sub> = 1.0V, /HPEN = V <sub>CC</sub> , EN_VT= low | 0.85 | 1   | 1.15 | V     |

| V <sub>TRAIL</sub>  | Receive threshold trailing edge             | V <sub>TVT</sub> = 0.5V, /HPEN = V <sub>CC</sub> , EN_VT= low | 0.35 | 0.5 | 0.65 | V     |

| V <sub>TVL</sub>    | Internal high-level threshold configuration | EN_VT= high                                                   | 1.8  | 2   | 2.2  | V     |

| V <sub>TVT</sub>    | Internal low-level threshold configuration  | EN_VT= high                                                   | 1.3  | 1.5 | 1.7  | V     |

| I <sub>THLEAK</sub> | TVL, TVT input leakage current              | $V_{TVL} = V_{TVT} = 2.5V$                                    | -1   |     | +1   | μΑ    |

### 7.5.4. DC characteristics/Digital I/O

#### (DIN, DOUT, RST, /PG\_P, /PG\_N, EN\_VT, WT\_ENb, HPEN)

| Symbol            | Parameter             | Conditions                                 | MIN | TYP MAX | UNITS |

|-------------------|-----------------------|--------------------------------------------|-----|---------|-------|

| VIH               | Input logic-high      |                                            | 1.4 |         | V     |

| VIL               | Input logic-low       |                                            |     | 0.4     | V     |

| I <sub>LEAK</sub> | Input leakage current |                                            | -1  | +1      | μA    |

| V <sub>OL</sub>   | Open-drain logic-low  | I <sub>SINK</sub> =2mA                     |     | 0.3     | V     |

| V <sub>ODL</sub>  | Open-drain leakage    | V <sub>OUT</sub> = 5V, output not asserted |     | 1       | μA    |

# CA-IF4288, CA-IF4289

#### Version 1.03

#### Shanghai Chipanalog Microelectronics Co., Ltd.

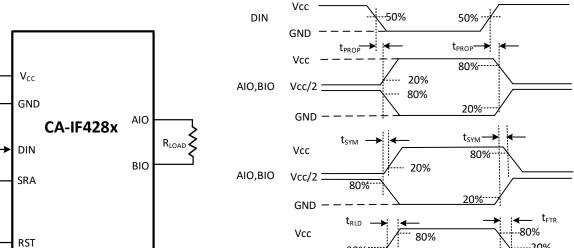

### 7.5.5. AC characteristics/Transmit channel

| Symbol                         | Parameter                                                     | Conditions                                                                                                                | MIN  | ТҮР | MAX  | UNITS |

|--------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------|-----|------|-------|

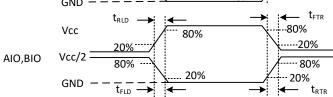

| t <sub>RLD</sub>               | Output rise time leading edge                                 | $R_{SRA}$ = 62k $\Omega$ , $R_{LOAD}$ =200 $\Omega$ , see Figure8- 1                                                      |      | 1.4 |      | μs    |

| t <sub>FLD</sub>               | Output fall time leading edge                                 | $R_{SRA}$ = 62k $\Omega$ , $R_{LOAD}$ =200 $\Omega$ , see Figure8- 1                                                      |      | 1.4 |      | μs    |

| t <sub>RTR</sub>               | Output rise time trailing edge                                | $R_{SRA}$ = 62k $\Omega$ , $R_{LOAD}$ =200 $\Omega$ , see Figure8- 1                                                      |      | 1.4 |      | μs    |

| t <sub>FTR</sub>               | Output fall time trailing edge                                | $R_{SRA}$ = 62k $\Omega$ , $R_{LOAD}$ =200 $\Omega$ , see Figure8- 1                                                      |      | 1.4 |      | μs    |

| t <sub>TPROP</sub>             | Transmit propagation delay                                    | $R_{SRA}$ = 62k $\Omega$ , $R_{LOAD}$ =200 $\Omega$ , see Figure8- 1                                                      |      | 1.2 |      | μs    |

| t <sub>sym</sub>               | Transmission output symmetry                                  | $R_{SRA}$ = 62k $\Omega$ , $R_{LOAD}$ =200 $\Omega$ , see Figure8- 1                                                      | -0.4 | 0   | +0.4 | μs    |

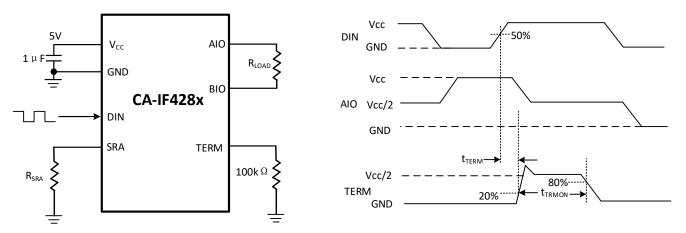

| t <sub>term</sub>              | Termination switching delay                                   | $R_{SRA}$ = 62k $\Omega$ , $R_{LOAD}$ =200 $\Omega$ , see Figure8- 2                                                      |      | 0.5 |      | μs    |

| t <sub>TRMON</sub>             | Termination on-time (default)                                 | R <sub>SRA</sub> = 62kΩ, R <sub>LOAD</sub> =200Ω, DTA is floating,<br>see Figure8- 2                                      | 19   | 34  | 63   | μs    |

| $t_{\text{TRMON}\_\text{min}}$ | Minimum value of termination on-time<br>(external adjustment) | $R_{SRA}$ = 62k $\Omega$ , $R_{LOAD}$ =200 $\Omega$ , connect DTA to GND through an 10k $\Omega$ resistor, see Figure8- 2 | 8    | 10  | 12   | μs    |

| $t_{\text{TRMON}\_\text{max}}$ | Maximum value of termination on-time<br>(External adjustment) | $R_{SRA}$ = 62k $\Omega$ , $R_{LOAD}$ =200 $\Omega$ , connect DTA to GND through a 500k resistor, see Figure8- 2          | 400  | 500 | 600  | μs    |

#### 7.5.6. AC characteristics/Receive channel

| Symbol             | Parameter                                  | Conditions                              | MIN | ТҮР | MAX | Units |

|--------------------|--------------------------------------------|-----------------------------------------|-----|-----|-----|-------|

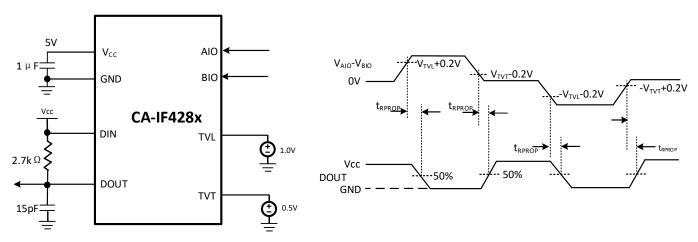

| t <sub>RPROP</sub> | Receive propagation delay                  | HPEN = V <sub>CC</sub> , see Figure8- 3 |     |     | 1   | μs    |

| t <sub>HP</sub>    | Receiver high pass filter time<br>constant | HPEN = V <sub>CC</sub> , see Figure8- 3 |     | 500 |     | μs    |

#### 7.5.7. Bus polarity detection<sup>1</sup>

| Symbol                                                 | Parameter                          | Conditions                    | MIN | ТҮР | MAX | Units |  |  |  |

|--------------------------------------------------------|------------------------------------|-------------------------------|-----|-----|-----|-------|--|--|--|

| V <sub>HIGH</sub>                                      | Bus polarity detection: logic high | $V_{HP}-V_{HN}$ , /PG_P = low | 2.5 | 3   | 3.5 | V     |  |  |  |

| V <sub>LOW</sub>                                       | Bus polarity detection: logic low  | $V_{HN}V_{HP}$ , /PG_N = low  | 2.5 | 3   | 3.5 | V     |  |  |  |

| Note:                                                  | Note:                              |                               |     |     |     |       |  |  |  |

| 1. The CA-IF4289 features bus polarity detection only. |                                    |                               |     |     |     |       |  |  |  |

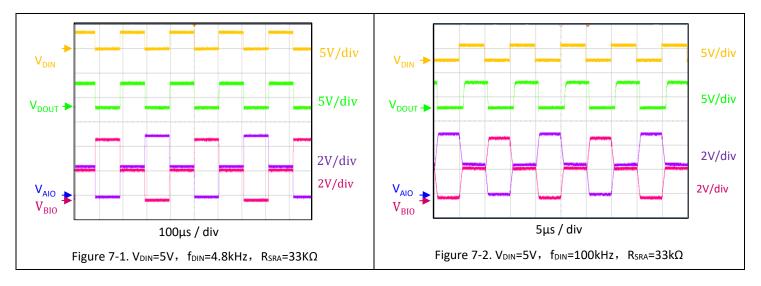

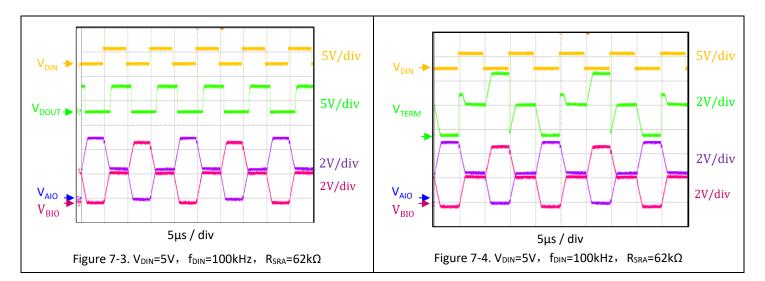

#### 7.6. Typical Characteristics and Waveforms

# CA-IF4288, CA-IF4289 Version 1.03

8. Parameter Measurement Information

Figure8- 1. Transmit Channel Timing Diagram

Figure8- 2. Transmission Switch Delay and Termination On-Time

#### 9. Detailed Description

The CA-IF428x home bus transceiver complies with the home bus standard, where power and data are carried on a single pair of wires. All devices can operate with data rates up to 200kbps for bus-powered applications and feature dynamic cable termination, programmable receiver hysteresis and thresholds, and transmit driver slew rate adjustment for better signal quality and flexible design. See Figure 9-1 and Figure 9-2 functional block diagram for the CA-IF4288 and the CA-IF4289.

CA-IF4288, CA-IF4289 Version 1.03

Shanghai Chipanalog Microelectronics Co., Ltd.

Figure 9-2. The CA-IF4289 Functional Block Diagram

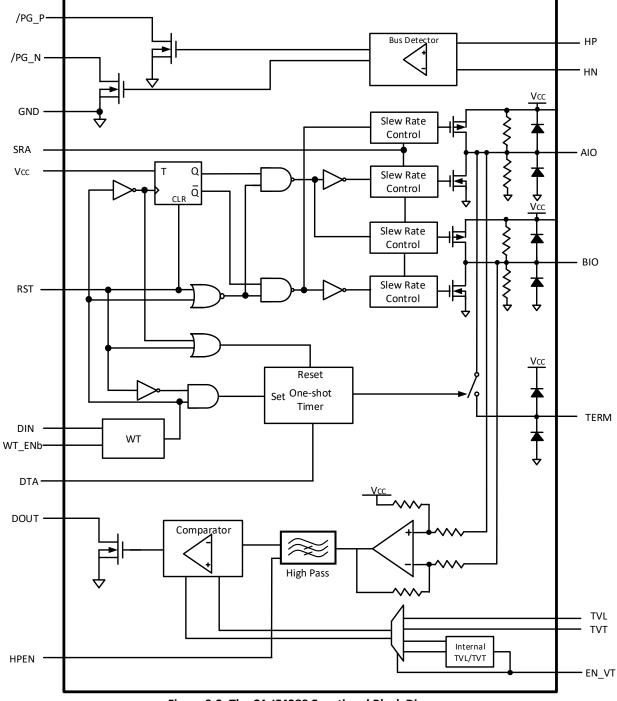

#### 9.1. Transceiver Operation

On the logic side, the CA-IF428x home bus transceivers have logic data input (DIN) and logic data output (DOUT); The reset control RST is used to enable or disable the bus transmitter: drive RST low to enable data transmission on AIO and BIO; drive RST high to disable the bus transmitter. The CA-IF428x home bus receiver is always active. In the typical applications, DIN, DOUT and RST logic pins are the interface with external micro-controller. Also, these devices feature an internal watchdog timer to avoid the bus being blocked by a long-zero. The timer is enabled by setting the logic input WT\_ENb to low. The internal watchdog timer monitors the logic input DIN and if any long-zero input persists for more than the watchdog timeout and blocks the bus, sets the AIO and BIO outputs to high-impedance states. Any transition resets the watchdog timer.

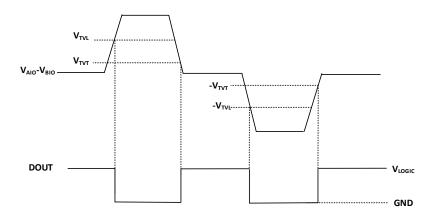

On the bus side, AIO, BIO, and TERM connected to the home bus network. When DIN goes from high to low, the polarities of AIO and BIO invert; When DIN goes from low to high, put AIO and BIO pins to high-impedance. DOUT asserts low when the leading edge of  $V_{AIO} - V_{BIO}$  crosses  $V_{TVL}$  or  $-V_{TVL}$ ; DOUT is high-impedance when the trailing edge of  $V_{AIO} - V_{BIO}$  crosses  $V_{TVL}$  or  $-V_{TVL}$ ; DOUT is high-impedance when the trailing edge of  $V_{AIO} - V_{BIO}$  crosses  $V_{TVL}$  or  $-V_{TVL}$ . See more details from Figure 9-3.

Figure 9-3. Transceiver Operation

#### 9.2. Transmitter Control and Configuration

#### 9.2.1. Dynamic Cable Termination

The CA-IF428x supports home bus signals at data rates up to 200kbps. When operating at high data rates, the mismatch between the home bus cable impedance and cable termination resistor can affect the signal transmission quality negatively. We recommend to connect a 200 $\Omega$  to 1k $\Omega$  cable termination resistor(R<sub>TRM</sub> in the typical application circuit) between AIO and BIO, and connect a resistor (100 $\Omega$ , typ) between TERM and BIO (R<sub>TRMO</sub> in the typical application circuit), to absorb reflections on the bus. The CA-IF428x features dynamic cable termination to improve the signal quality for long distance transmission. When the driver transitions to high-impedance, an internal switch connects AIO to TERM and the external termination resistor(R<sub>TRMO</sub>) at TERM is connected between AIO and BIO in parallel with the cable termination resistor(R<sub>TRM</sub>). When DOUT asserts low, or when RST is driven high, the internal switch opens after 34 $\mu$ s (typ) fixed time for the CA-IF4288; For the CA-IF4289, the internal termination switch opens after 34 $\mu$ s with DTA pin floating, or opens after 10 $\mu$ s to 500 $\mu$ s with 10 $k\Omega$  to 500 $k\Omega$  of R<sub>DTA</sub>, the external resistor connected between DTA and GND. Termination on-time calculation is as below equation:

#### $t_{DTA} = R_{DTA} / 1 k \Omega$

Where  $R_{DTA}$  is in  $k\Omega$ ,  $t_{DTA}$  is in  $\mu$ s. When operating at lower data rate, we recommend to select larger  $R_{DTA}$ , for example, 120k $\Omega$  to 200k $\Omega$   $R_{DTA}$  at 9.6kbps data rate. Also, select a larger termination resistor between AIO and BIO,  $R_{TRM}$  and increase the receiver threshold hysteresis when operating at low-speed transmission to reduce power consumption and improve system reliability. The optimized value of the dynamic termination resistor depends on the application. For typical applications, the value of the dynamic termination resistor is between 50 $\Omega$  and 240 $\Omega$ .

# CA-IF4288, CA-IF4289 Version 1.03

# 9.2.2. Transmit Slew Rate Adjustment

Connect resistor  $R_{SRA}$  between SRA and GND to control the slew rate of the transmit signals (AIO and BIO). The transmit rise ( $t_{RLD}$ ,  $t_{RTR}$ )/fall time ( $t_{FLD}$ ,  $t_{FTR}$ ) is proportional to  $R_{SRA}$  and is calculated using the following equation:

$$t_{rise/fall} = 17(pF) \times R_{SRA}(\Omega)$$

For most applications, it is recommended to use  $R_{SRA} = 33k\Omega$  resulting in 0.56µs (typ) output rise/fall time. Ensure that  $R_{SRA}$  is in the range from  $20k\Omega$  to  $120k\Omega$ .

#### 9.2.3. RST (Reset) Control

The CA-IF428x family devices feature a bus reset control input. Drive RST low to enable the bus transmitter. Drive RST high to disable the bus transmitter. RST also controls the internal switch used for dynamic cable termination. Ensure that RST remains low for at least  $34\mu$ s (typ) after the internal switch is closed when the driver transitions to high-impedance. The internal switch opens when put RST high.

#### 9.2.4. Data Input Timeout Detection

The CA-IF428x devices feature logic data input timeout detection that prevents erroneous controllers from clamping the bus to a low level by maintaining a continuous low input signal. Connect WT\_ENb pin to low to enable timeout detection. In this case, when data input DIN remains in the low for greater than 21ms(typ), the transmitter is disabled that places the driver outputs (AIO/BIO) in a high-impedance state. To disable timeout detection, connect WT\_ENb to logic high.

#### 9.3. Receiver Control and Configuration

#### 9.3.1. Receiver Threshold Adjustment

The threshold levels of receiving signals are set by the voltages at TVL and TVT. The voltage at TVL sets the threshold for the pulse leading edge of receiving signals from the home bus( $V_{AIO} - V_{BIO}$ ). The voltage at TVT sets the threshold for the pulse trailing edge of receiving signals from home bus. Ensure that  $V_{TVL} > V_{TVT}$ . DOUT asserts low when  $V_{AIO} - V_{BIO}$  crosses  $V_{TVL}$  or  $-V_{TVL}$ . DOUT is high impedance when  $V_{AIO} - V_{BIO}$  crosses  $V_{TVT}$  or  $-V_{TVT}$ , see Figure 9-4. Receiver Thresholds. Connect a pull-up resistor between DOUT and the logic supply.

The CA-IF4289 provides internal threshold voltage configuration. Connect EN\_VT to logic high, the threshold levels for the receiving signals are set internally, the default threshold voltage is  $V_{TVL}=2V$  and  $V_{TVT}=1.5V$ . Connect EN\_VT to logic low, the threshold levels are set externally (see the typical application circuit), dependent on the voltage at pin TVL and TVT.

Figure 9-4. Receiver Thresholds

#### 9.3.2. High-Pass Filter

The CA-IF428x home bus transceivers have an internal high-pass filter on the receiver input to filter out the low frequency noise at AIO and BIO. The CA-IF4289 features high-pass filter enable control HPEN, connect HPEN to V<sub>CC</sub> to enable the internal high-pass filter on the receiver input; Connect HPEN to GND to disable the internal high pass filter. In any cases, don't leave the pin HPEN open. The CA-IF4288 doesn't have enable control HPEN, it's internal high-pass filter is always enabled.

#### 9.4. Bus Polarity Detection

The CA-IF4289 device offers bus polarity detection that prevents wrong cable connection on the bus. When  $V_{HP}$ - $V_{HN}$  is greater than 3V (typ), /PG\_P asserts to low level, indicates the bus polarity is positive; When  $V_{HN}$ - $V_{HP}$  is greater than 3V (typ), /PG\_N asserts to low level, indicates that the bus polarity is negative. When the bus is not powered, both /PG\_P and /PG\_N assert to logic high via external pull-up resistors. Connect a 200 $\Omega$  resistor between home bus and HP/HN pins for surge protection.

#### 10. Application and Implementation

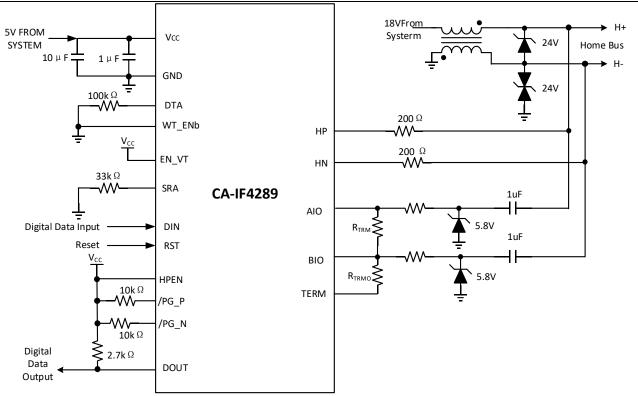

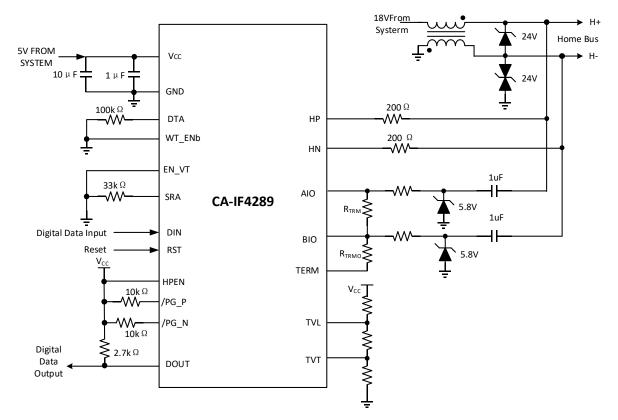

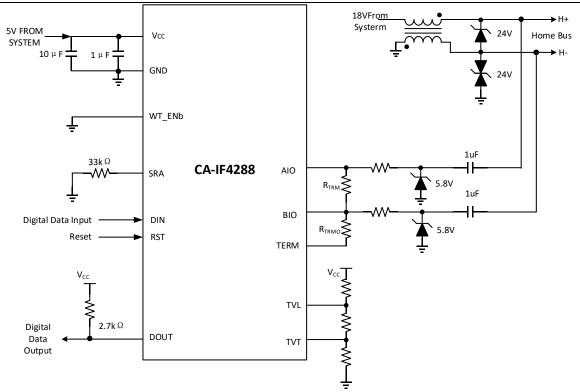

In the home bus standard, power and data are carried on a single pair of wires. The CA-IF428x family is powered by +5V system supply voltage at V<sub>CC</sub>. An external AC-blocking inductor is required to superimpose the data on the home bus cable or to separate data from home bus cable, see Figure 10-1 to Figure 10-3 typical application circuits for the CA-IF4289 and the CA-IF4288.

#### **10.1.** Surge Protection

External components are required to protect the CA-IF428x home bus pins (HP, HN, AIO, BIO and TERM) from high voltage transient events (see Figure 10-1 to Figure 10-3). AIO, BIO and TERM must be protected with external TVS diodes and resistors from surge transients. Connect TVS diodes with a 5.8V maximum voltage rating from AIO to GND and BIO to GND, respectively. Connect a 4.7 $\Omega$  serial resistor between each TVS diode and AIO/BIO to limit the surge current. Depending on the surge transients polarities, the residual current after the 4.7 $\Omega$  resistor flows from AIO/BIO through the internal ESD clamping diodes to V<sub>CC</sub> or GND.

Connect a 200 $\Omega$  resistor between the bus and HP, HN pins respectively for surge protection. Connect at least 1µF ceramic bypass capacitor as close to V<sub>CC</sub> pin as possible, and a minimum 10µF bulk capacitor between V<sub>CC</sub> and GND to limit the voltage overshoot on V<sub>CC</sub> pin.

#### 10.1. PCB Layout Recommendations

Although impedance matching is not required on H+ and H- lines, route them together as much as possible. To reduce the parasitic capacitance on signal lines, do not route H+ and H- lines, or the connected components over the ground planes. To ensure proper protection, connect the ground return of the protection diodes directly to the ground plane. Use a star configuration to connect all grounds together as close to the GND as possible. Place the external protection components, TVS diodes and the diode bridge, as close to the home bus connector as possible.

Figure 10-1. The CA-IF4289 Typical Application Circuit with Internal Threshold Setup (connect EN\_VT to Vcc)

Figure 10-3. The CA-IF4288 Typical Application Circuit

CA-IF4288, CA-IF4289 Version 1.03

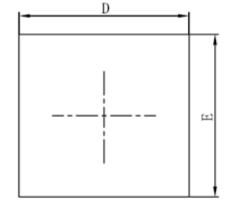

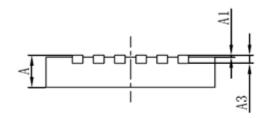

11. Package Information

QFN package outline

# SIDE VIEW

| Symbol | Dimensions I | n Millimeters | Dimensions In Inches |       |  |  |

|--------|--------------|---------------|----------------------|-------|--|--|

| Symbol | Min.         | Max.          | Min.                 | Max.  |  |  |

| A      | 0.700        | 0.800         | 0.028                | 0.031 |  |  |

| A1     | 0.000        | 0.050         | 0.000                | 0.002 |  |  |

| A3     | 0.203        | REF.          | 0.008REF.            |       |  |  |

| D      | 3.950        | 4.050         | 0.156                | 0.159 |  |  |

| E      | 3.950        | 4.050         | 0.156                | 0.159 |  |  |

| E1     | 2.400        | 2.500         | 0.094                | 0.098 |  |  |

| D1     | 2.400        | 2.500         | 0.094                | 0.098 |  |  |

| k      | 0.20         | OMIN          | 0.008MIN             |       |  |  |

| b      | 0.200        | 0.300         | 0.008                | 0.012 |  |  |

| е      | 0.500        | TYP.          | 0.020TYP.            |       |  |  |

| L      | 0.350        | 0.450         | 0.014                | 0.018 |  |  |

# Note:

1. All dimensions are in millimeters, angles are in degrees.

Figure 11-1. QFN packaging Information

BOTTOM VIEW

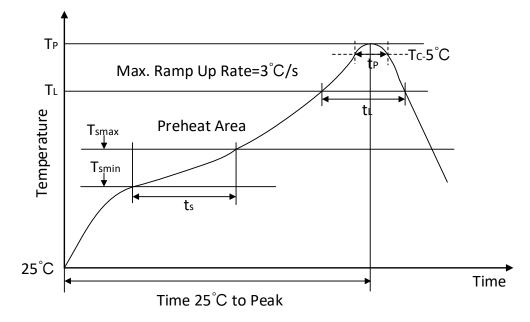

# 12. Soldering Temperature (reflow) Profile

Figure 12-1. Soldering Temperature (reflow) Profile

| Profile Feature                                                                | Pb-Free Assembly   |  |

|--------------------------------------------------------------------------------|--------------------|--|

| Average ramp-up rate(217 $^\circ \!\! \mathbb{C}$ to Peak)                     | 3°C/second max     |  |

| Time of Preheat temp(from 150 $^\circ\!\mathrm{C}$ to 200 $^\circ\!\mathrm{C}$ | 60-120 second      |  |

| Time to be maintained above 217 $^\circ\!\mathrm{C}$                           | 60-150 second      |  |

| Peak temperature                                                               | <b>260 +5/-0</b> ℃ |  |

| Time within 5 $^{\circ}\!\mathrm{C}$ of actual peak temp                       | 30 second          |  |

| Ramp-down rate                                                                 | 6 ℃/second max.    |  |

| Time from $25^{\circ}$ C to peak temp                                          | 8 minutes max      |  |

# CA-IF4288, CA-IF4289 Version 1.03

13. Tape and Reel Information

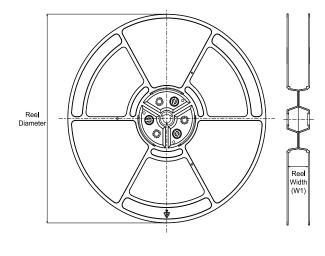

# REEL DIMENSIONS

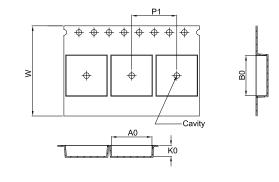

TAPE DIMENSIONS

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| К0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

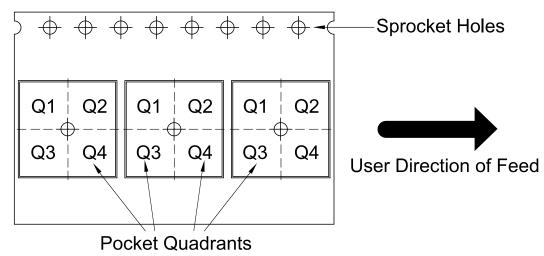

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

|           |                 |                    |      | A    | il dimensions (          | are nominal              |            |            |            |            |           |                  |

|-----------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device    | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | КО<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| CA-IF4288 | QFN             | F                  | 24   | 3000 | 330                      | 12.4                     | 4.3        | 4.3        | 1.1        | 8.0        | 12.0      | Q1               |

| CA-IF4289 | QFN             | F                  | 24   | 3000 | 330                      | 12.4                     | 4.3        | 4.3        | 1.1        | 8.0        | 12.0      | Q1               |

| *All dimensions are noming | nal |

|----------------------------|-----|

|----------------------------|-----|

#### **14. IMPORTANT NOTICE**

The above information is for reference only and is used to assist Chipanalog customers in design and development. Chipanalog reserves the right to change the above information due to technological innovation without prior notice.

Chipanalog products are all factory tested. The customers shall be responsible for self-assessment and determine whether it is applicable for their specific application. Chipanalog's authorization to use the resources is limited to the development of related applications that the Chipanalog products involved in. In addition, the resources shall not be copied or displayed. And Chipanalog shall not be liable for any claim, cost, and loss arising from the use of the resources.

#### **Trademark Information**

Chipanalog Inc.<sup>®</sup>, Chipanalog<sup>®</sup> are trademarks or registered trademarks of Chipanalog.

http://www.chipanalog.com