# CA-IF1042-Q1 ±70V Fault Protected CAN Transceiver with CAN FD

### 1. Features

- Meets the ISO 11898-2:2016 and ISO 11898-5:2007 physical layer standards

- 'Turbo' CAN:

- Support classic CAN and 5 Mbps CAN FD (flexible data rate)

- Short and symmetrical propagation delay time and fast loop time for enhanced timing margin

- Higher data rate in loaded CAN networks

- Ideal passive behavior when unpowered

- Bus and logic terminals are high impedance (no load)

- Power up/down with glitch free operation on bus and RXD output

- Integrated protection increases robustness

- ±70V fault-tolerant CANH and CANL

- ±30V extended common-mode input range (CMR)

- Undervoltage protection on V<sub>cc</sub> and V<sub>io</sub> supply terminals

- Transmitter dominant timeout prevents lockup, data rates down to 4 kbps

- Thermal shutdown

- Typical loop delay: 160ns

- 3.0V to 5.5V Logic-Supply (V<sub>IO</sub>) Range (CA-IF1042VS-Q1 only)

- –55°C to 150°C Junction Temperatures Range

- Available in SOIC8 Packages

- AEC Q-100 qualified for automotive applications (CA-IF1042S-Q1, CA-IF1042VS-Q1)

- 2. Applications

- Body electronics and lighting

- Automotive gateway

- Advanced driver assistance systems (ADAS)

- Infotainment and cluster

- Hybrid, electric & powertrain systems

- Personal transport vehicles Electric bike

- Industrial control

## 3. General Description

The CA-IF1042x devices are control area network (CAN) transceivers with integrated protection for industrial and automotive applications. These devices are designed for using in CAN FD networks up to 5 Mbps and feature ±70V extended fault protection on the CAN bus for equipment where overvoltage protection is required. This family of CAN transceivers also incorporate an input common-mode range(CMR) of ±30V, exceeding the ISO 11898 specification of -2V to +7V, well suited for applications where ground planes from different systems are shifting relative to each other.

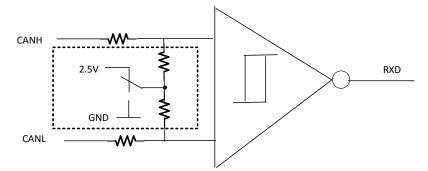

The CA-IF1042x series devices include a dominant timeout to prevent bus lockup caused by controller error or by a fault on the TXD input. When the TXD remains in the dominant state (low) for longer than  $t_{DOM}$ , the driver is switched to the recessive state, releasing the bus and allowing other nodes to communicate. The transceivers feature a STB pin for two modes of operation: normal high-speed mode and standby mode for low current consumption. Also, the CA-IF1042VS-Q1 family of devices provides low level translation to simplify the interface with low voltage CAN controllers.

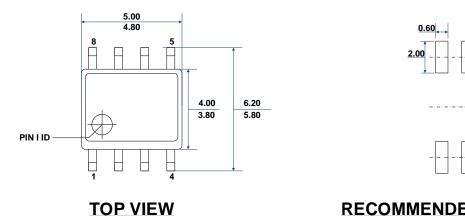

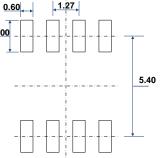

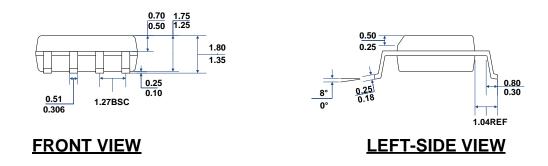

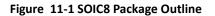

The CA-IF1042x family of devices is available in a standard 8-pin narrow-body SOIC package, operates over the -55°C to +150°C junction temperature range.

#### **Device Information**

| Part number    | Package | Package size(NOM) |  |

|----------------|---------|-------------------|--|

| CA-IF1042S-Q1  | SOLCA   | 4.9mm x 3.9mm     |  |

| CA-IF1042VS-Q1 | SOIC8   | 4.9mm x 3.9mm     |  |

# 4. Ordering Information

#### Table 4-1 Ordering Information

| Part Number    | Features                                                                | Package |

|----------------|-------------------------------------------------------------------------|---------|

| CA-IF1042S-Q1  | Automotive qualified part, Pin 5 = NC                                   | SOIC8   |

| CA-IF1042VS-Q1 | Automotive qualified part; with low level translation, Pin 5 = $V_{10}$ | SOIC8   |

# Contents

| 1. | Featu                                                                                                        | res1                                                                                                                                                                                            |

|----|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2. | Appli                                                                                                        | cations1                                                                                                                                                                                        |

| 3. | Gene                                                                                                         | ral Description1                                                                                                                                                                                |

| 4. | Orde                                                                                                         | ring Information2                                                                                                                                                                               |

| 5. | Revis                                                                                                        | ion History3                                                                                                                                                                                    |

| 6. | Pin C                                                                                                        | onfiguration and Functions4                                                                                                                                                                     |

| 7. | Speci                                                                                                        | fications5                                                                                                                                                                                      |

|    | <ol> <li>7.1.</li> <li>7.2.</li> <li>7.3.</li> <li>7.4.</li> <li>7.5.</li> <li>7.6.</li> <li>7.7.</li> </ol> | Absolute Maximum Ratings5ESD Ratings5Recommended Operating Conditions5Thermal Information5Electrical Characteristics6Switching Characteristics8Typical Operating Characteristics and Waveforms9 |

| 8. | Paran                                                                                                        | neter Measurement Information12                                                                                                                                                                 |

| 9. | Detai                                                                                                        | led Description16                                                                                                                                                                               |

|     | 9.1. | CAN      | Bus Status                   | 16 |

|-----|------|----------|------------------------------|----|

|     | 9.2. | Rece     | iver                         | 17 |

|     | 9.3. | Trans    | smitter                      | 17 |

|     | 9.4. | Prote    | ection Functions             | 18 |

|     | 9    | .4.1.    | Undervoltage Lockout         | 18 |

|     | 9    | .4.2.    | Fault Protection             | 19 |

|     | 9    | .4.3.    | Thermal Shutdown             | 19 |

|     | 9    | .4.4.    | Current-Limit                | 19 |

|     | 9    | .4.5.    | Transmitter-Dominant Timeout | 19 |

|     | 9.5. | Unpo     | owered Device                | 20 |

|     | 9.6. | Float    | ing Terminals                | 20 |

|     | 9.7. | Oper     | ating Mode                   | 20 |

|     | 9    | .7.1.    | Normal Mode                  | 20 |

|     | 9    | .7.2.    | Standby Mode                 | 20 |

| 10. | Арр  | lication | Information                  | 21 |

| 11. | Pack | age Inf  | ormation                     | 23 |

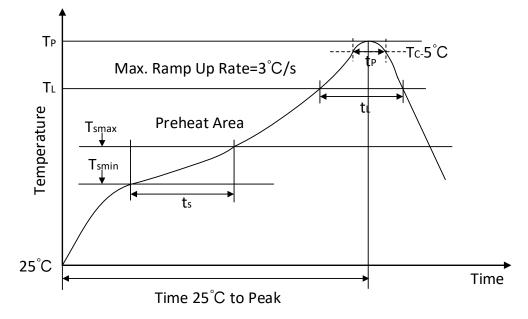

| 12. | Sold | ering T  | emperature (reflow) Profile  | 24 |

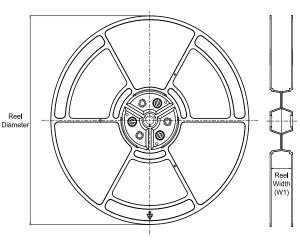

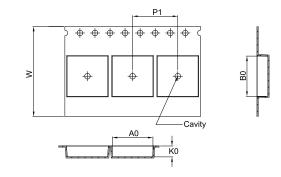

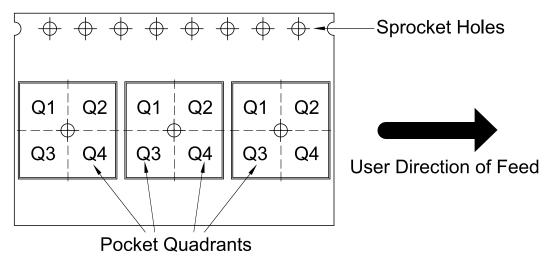

| 13. | Таре | e and R  | eel Information              | 25 |

| 14. | Арр  | endix    |                              | 26 |

| 15. | Imp  | ortant   | Statement                    | 28 |

# 5. Revision History

| Revision Number | Description                                                      | Page Changed |

|-----------------|------------------------------------------------------------------|--------------|

| Version 1.01    | N/A                                                              | N/A          |

| Version 1.02    | Add VDIFF_D VDIFF_R VDIFF_D(STB) VDIFF_R(STB)                    | 7            |

| Version 1.02    | Change CLD to CL , add CRXD                                      | 8            |

| Version 1.03    | Update 5V Supply Current Icc                                     | 6            |

| Version 1.04    | Update the title description                                     | 1            |

| Version 1.05    | Update Tape and Reel Information                                 | 29           |

| Version 1.06    | Optimize VCC and VIO UVLO descriptions                           | 6,18         |

| Version 1.07    | Update the Description of Logical Interfaces VIH/VIL and VOH/VOL | 6            |

| Version 1.08    | Delete DNF8 packaging part number                                | 1,2,24       |

CHIPANALOG

#### Shanghai Chipanalog Microelectronics Co., Ltd.

# 6. Pin Configuration and Functions

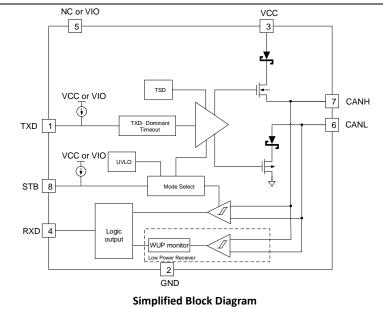

Figure 6-1 CA-IF1042x Pin Configuration

| Pi            | n #            | Pin             | Turne       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|----------------|-----------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CA-IF1042S-Q1 | CA-IF1042VS-Q1 | Name            | туре        | Digital I/OTXD low to set the driver in the dominant state. TXD is a CMOS/TTL compatil<br>input from a CAN controller with an internal pull-up to V <sub>CC</sub> or V <sub>IO</sub> .GNDGround.Power+5V Supply Voltage. Bypass V <sub>CC</sub> to GND with an at least 0.1µF capacitor.Receive Data Output, RXD is LOW for dominant bus state and HIGH for recess<br>bus state. RXD is a CMOS/TTL compatible output from the physical bus lin<br>CANH and CANL.NCNo connect.PowerLogic Supply Input. V <sub>IO</sub> is the logic supply voltage for the input/output betwee<br>the CAN transceiver and controller. V <sub>IO</sub> allows full compatibility from +3.0V<br>+5.5V logic on all digital lines. Bypass to GND with a 0.1µF capacitor. Connect<br>to V <sub>CC</sub> for 5V logic compatibility.Bus I/OCAN bus line low.Bus I/OCAN bus line high. |

|               |                |                 |             | Transmit Data Input, Drive TXD high to set the driver in the recessive state. Drive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1             | 1              | TXD             | Digital I/O | TXD low to set the driver in the dominant state. TXD is a CMOS/TTL compatible                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|               |                |                 |             | input from a CAN controller with an internal pull-up to $V_{\text{CC}}$ or $V_{\text{IO}}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2             | 2              | GND             | GND         | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3             | 3              | V <sub>CC</sub> | Power       | +5V Supply Voltage. Bypass $V_{CC}$ to GND with an at least 0.1µF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|               |                |                 |             | Receive Data Output, RXD is LOW for dominant bus state and HIGH for recessive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4             | 4              | RXD             | Digital I/O | bus state. RXD is a CMOS/TTL compatible output from the physical bus lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|               |                |                 |             | CANH and CANL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5             | -              | NC              | NC          | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|               |                |                 |             | Logic Supply Input. $V_{10}$ is the logic supply voltage for the input/output between                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|               | 5              | VIO             | Power       | the CAN transceiver and controller. $V_{10}$ allows full compatibility from +3.0V to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| -             | J              | <b>V</b> 10     | Fower       | +5.5V logic on all digital lines. Bypass to GND with a $0.1\mu F$ capacitor. Connect $V_{10}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|               |                |                 |             | to V <sub>cc</sub> for 5V logic compatibility.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6             | 6              | CANL            | Bus I/O     | CAN bus line low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7             | 7              | CANH            | Bus I/O     | CAN bus line high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|               |                |                 |             | Standby Mode. A logic-high on STB pin or leave it open to select the standby                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8             | 8              | STB             | Digital 1/0 | mode. In standby mode, the transceiver is not able to transmit data and the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ŏ             | õ              | 218             | Digital I/O | receiver is in low-power mode. A logic-low on STB pin puts the transceiver in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|               |                |                 |             | normal operating mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### Table 6-1 CA-IF1042x Pin Configuration and Description

#### 7. Specifications

#### **Absolute Maximum Ratings** 7.1.

|                             | PARAMETER                                      | MIN  | MAX                          | UNIT |

|-----------------------------|------------------------------------------------|------|------------------------------|------|

| V <sub>CC</sub>             | 5V Bus Supply Voltage Range                    | -0.3 | 7                            | V    |

| V <sub>IO</sub>             | Logic Supply Voltage Range                     | -0.3 | 7                            | V    |

| V <sub>BUS</sub>            | CAN Bus I/O voltage range (CANH,CANL)          | -70  | 70                           | V    |

| V <sub>(DIFF)</sub>         | Max differential voltage between CANH and CANL | -70  | 70                           | V    |

| V <sub>(Logic_Input)</sub>  | Logic input terminal voltage range (TXD, S)    | -0.3 | V <sub>IO</sub> +0.3 and <+7 | V    |

| V <sub>(Logic_Output)</sub> | Logic output terminal voltage range (RXD)      | -0.3 | V <sub>IO</sub> +0.3 and <+7 | V    |

| I <sub>O(RXD)</sub>         | RXD (receiver) terminal output current         | -8   | 8                            | mA   |

| Tj                          | Virtual junction temperature range             | -55  | 150                          | °C   |

| T <sub>STG</sub>            | Storage temperature range                      | -65  | 150                          | °C   |

| Note:                       |                                                |      |                              |      |

The stresses listed under "Absolute Maximum Ratings" are stress ratings only, not for functional operation condition. Exposure to absolute 1. maximum rating conditions for extended periods may cause permanent damage to the device.

#### **ESD** Ratings 7.2.

| Parameters                                                                     | TEST CONDITIONS                              |                                             | VALUE              | UNIT |

|--------------------------------------------------------------------------------|----------------------------------------------|---------------------------------------------|--------------------|------|

| HBM <sup>1</sup> ESD                                                           | CAN bus terminals (CANH, CANL) to GND        |                                             | ±16000             | V    |

|                                                                                | Other pins                                   |                                             | ±8000              | v    |

| CDM ESD                                                                        | All pins                                     |                                             | ±2000              | V    |

| System Level ESD                                                               | CAN bus terminals (CANH, CANL) to GND        | IEC 61000-4-2: unpowered contact discharge. | ±6000 <sup>2</sup> | v    |

| Note:<br>1. Per JEDEC document JEP155, 50<br>2. Testing on System Board Level. | OV HBM allows safe manufacturing of standard | d ESD control process.                      |                    | 1    |

#### 7.3. **Recommended Operating Conditions**

|                      | PARAMETER                              | MIN | TYP MAX | UNIT |

|----------------------|----------------------------------------|-----|---------|------|

| V <sub>cc</sub>      | Supply Voltage Range                   | 4.5 | 5.5     | V    |

| V <sub>IO</sub>      | Logic Supply Voltage Range             | 3.0 | 5.5     | V    |

| I <sub>OH(RXD)</sub> | RXD terminal high level output current | -2  |         | mA   |

| I <sub>OL(RXD)</sub> | RXD terminal low level output current  |     | 2       | mA   |

#### **Thermal Information** 7.4.

| Thermal Metric           ØJA         Junction to Ambient |                        | SOIC8 | UNIT |

|----------------------------------------------------------|------------------------|-------|------|

| R <sub>θJA</sub>                                         | Junction to Ambient    | 170   | °C/W |

| R <sub>θJC(top)</sub>                                    | Junction to Case (top) | 40    | °C/W |

# 7.5. Electrical Characteristics

|                                         | PARAMETER                                          | TEST CONDITIONS                                                            | MIN                 | ТҮР | MAX                 | UNIT     |

|-----------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------|---------------------|-----|---------------------|----------|

| POWER                                   |                                                    |                                                                            |                     |     |                     |          |

|                                         |                                                    | TXD=0V, $R_L = 60 \Omega$ (dominant), $C_L=open$ ,                         |                     |     |                     |          |

|                                         |                                                    | Rсм=open, STB=OV, see Figure 8-1                                           |                     | 45  | 80                  | mA       |

|                                         |                                                    | TXD=0V, STB=0V, CANH=-12V, RL=open,                                        |                     |     |                     |          |

|                                         |                                                    | СL=open, Rcм=open, see Figure 8-1                                          |                     |     | 110                 | mA       |

|                                         |                                                    | TXD=V <sub>CC</sub> or V <sub>IO</sub> , RL=50 Ohm, Rсм =open,             |                     |     |                     |          |

|                                         |                                                    | CL=open ,                                                                  |                     | 1.3 | 2.5                 | mA       |

| I <sub>cc</sub>                         | 5V Supply Current                                  | STB=0V, see Figure 8-1                                                     |                     |     |                     |          |

|                                         |                                                    | TXD = STB = V <sub>IO</sub> (standby, CA-IF1042VS-                         |                     |     |                     | μA       |

|                                         |                                                    | Q1), RL = 50 Ohm, CL=open, RcM=open,                                       |                     | 0.5 | 5                   |          |

|                                         |                                                    | see Figure 8-1                                                             |                     |     |                     |          |

|                                         |                                                    | TXD = STB = $V_{cc}$ (standby, CA-IF1042S-Q1),                             |                     |     |                     | μΑ       |

|                                         |                                                    | RL = 50 Ohm, see Figure 8-1                                                |                     | 14  | 22                  |          |

|                                         |                                                    | TXD = 0V, STB = 0V, RXD open                                               |                     | 70  | 300                 | μA       |

| I <sub>IO</sub>                         | I/O Supply Current                                 | TXD= V <sub>IO</sub> , STB= V <sub>IO</sub> , RXD open                     |                     | 11  | 17                  | μΑ       |

| V <sub>uv_vcc</sub>                     | V <sub>cc</sub> UVLO Threshold                     | Rising                                                                     |                     | 4.1 | 4.45                | V        |

| V <sub>uv_vcc</sub>                     | V <sub>cc</sub> UVLO Threshold                     | Falling                                                                    | 3.55                | 3.9 | 4.35                | V        |

| Vuv_vcc_hys                             | V <sub>cc</sub> UVLO Threshold                     | Hysteresis                                                                 |                     | 200 |                     | mV       |

| V <sub>UV_IO/</sub>                     | V <sub>IO</sub> UVLO threshold (CA-IF1042VS-Q1)    |                                                                            |                     |     |                     |          |

| V <sub>uv_vcc_sd</sub>                  | $/V_{CC sd}$ UVLO threshold (CA-IF1042S-Q1)        | Rising                                                                     | 1.3                 |     | 2.8                 | V        |

| V <sub>UV_IO_hys/</sub>                 | V <sub>IO</sub> UVLO threshold (CA-IF1042VS-Q1)    |                                                                            |                     |     |                     |          |

| Vuv_vcc_sd_hys                          | /V <sub>CC_sd</sub> UVLO threshold (CA-IF1042S-Q1) | Hysteresis                                                                 |                     | 80  |                     | mV       |

|                                         | FACE (Mode select input, STB)                      |                                                                            |                     |     |                     |          |

| VIH                                     | High-level input voltage                           |                                                                            | 0.7xV <sub>I0</sub> |     |                     | V        |

| V <sub>IL</sub>                         | Low-level input voltage                            |                                                                            | 0                   |     | 0.3xV <sub>Io</sub> | V        |

| I <sub>IH</sub>                         | High-level input leakage current                   | $STB = V_{CC} = V_{IO} = 5.5V$                                             | -2                  |     | 2                   | μA       |

|                                         | Low-level input leakage current                    | $STB = 0V, V_{CC} = V_{IO} = 5.5V$                                         | -20                 |     | -2                  | μΑ       |

| I <sub>lek(off)</sub>                   | Unpowered leakage current                          | STB=5.5V, $V_{CC} = V_{IO} = 0V$                                           | -1                  |     | 1                   | μΑ       |

|                                         | FACE (CAN transmit data input, TXD)                | 515-515 4, 400 - 54                                                        | -                   |     | -                   | μη       |

|                                         |                                                    | CA-IF1042VS-Q1                                                             | 0.7xV <sub>lo</sub> |     |                     | V        |

| V <sub>IH</sub>                         | High-level input voltage                           | CA-IF10425-Q1                                                              | 0.7xV <sub>10</sub> |     |                     | V        |

|                                         |                                                    | CA-IF10425-Q1                                                              | 0.7.000             |     | 0.3xV <sub>lo</sub> | V        |

| VIL                                     | Low-level input voltage                            | CA-IF1042V3-Q1                                                             |                     |     | 0.3xV <sub>lo</sub> | V        |

| 1                                       | High-level input leakage current                   | $TXD = V_{CC} = V_{IO} = 5.5V$                                             | -2.5                | 0   | 1                   | -        |

|                                         |                                                    |                                                                            |                     | -50 | -7                  | μΑ       |

|                                         | Low-level input leakage current                    | TXD = 0V, $V_{CC} = V_{IO} = 5.5V$<br>TXD = 5.5V, $V_{CC} = V_{IO} = 0V$   | -100                |     |                     | μΑ       |

| I <sub>lek(off)</sub><br>C <sub>i</sub> | Unpowered leakage current<br>Input capacitance     | $V_{IN} = 0.4^* \sin(4E6^*\pi^*t) + 2.5V$                                  | -1                  | 0   | 1                   | μA       |

|                                         |                                                    | $v_{\rm IN} = 0.4^{\circ} \sin(420^{\circ} \pi^{\circ} t) + 2.5^{\circ} v$ |                     | 5   |                     | pF       |

| LOGIC INTER                             | FACE (CAN receive data output, RXD)                |                                                                            | 0.0.1/              |     |                     |          |

| V <sub>OH</sub>                         | High-level output voltage                          | CA-IF1042VS-Q1: lo = $-2mA$ , see Figure 8-2                               | 0.8xV <sub>lo</sub> |     |                     | V        |

|                                         |                                                    | CA-IF1042S-Q1: Io = -2mA, see Figure 8-2                                   | 0.8xV <sub>CC</sub> |     |                     | V        |

|                                         |                                                    | CA-IF1042VS-Q1: Io = +2mA, see Figure 8-                                   |                     |     | 0.2xV <sub>Io</sub> | v        |

| V <sub>OL</sub>                         | Low-level output voltage                           | 2                                                                          |                     |     |                     | <u> </u> |

|                                         |                                                    | CA-IF1042S-Q1: Io = +2mA, see Figure 8-2                                   |                     |     | 0.2xV <sub>CC</sub> | V        |

| l <sub>lek(off)</sub>                   | Unpowered leakage current                          | $STB = 5.5V, V_{CC} = 0V, V_{IO} = 0V$                                     | -1                  | 0   | 1                   | μA       |

| Devices                                 | 1                                                  |                                                                            | 1                   |     |                     | 1        |

| T <sub>TSD</sub>                        | Thermal shutdown temperature                       |                                                                            |                     | 185 |                     | °C       |

| -                                       | Thermal shutdown temperature                       |                                                                            |                     | 4-  |                     |          |

| T <sub>TSD_HYS</sub>                    | threshold hysteresis                               |                                                                            |                     | 15  |                     | °C       |

|                                         |                                                    |                                                                            | L                   |     |                     | 1        |

# **Electrical Characteristics (continued)**

|                      | PARAMETER                         | T <sub>A</sub> = -40°C to 125°C (unless otherwise noted).                                       | MIN     | ТҮР                   | MAX   | UNIT  |

|----------------------|-----------------------------------|-------------------------------------------------------------------------------------------------|---------|-----------------------|-------|-------|

|                      |                                   |                                                                                                 |         |                       | WIAX  |       |

| CAN BUS D            | PRIVER                            |                                                                                                 | 1       |                       |       | 1     |

|                      |                                   | TXD = low, STB = 0V, $R_L$ =50 -65 $\Omega$ , $C_L$ =open,                                      | 2.75    |                       | 4.5   | V     |

| V <sub>O(DOM)</sub>  | Bus output voltage (dominant)     | Rсм=open, CANH, see Figure 8-1                                                                  | 2.75    |                       | 1.5   | •     |

| VO(DOM)              | Bus output voltage (dominant)     | TXD = low, STB = 0V, $R_L$ = 50 -65 $\Omega$ , $C_L$ =open,                                     | 0.5     |                       | 2.25  | v     |

|                      |                                   | Rсм=open, CANL, see Figure 8-1                                                                  | 0.5     |                       | 2.25  | V     |

|                      |                                   | TXD = low, STB=0V, RL=45-50 Ohm, Rсм open, see                                                  |         |                       |       |       |

|                      |                                   | Figure 8-1                                                                                      | 1.4     |                       | 3     | V     |

|                      | Bus output differential voltage   | 5                                                                                               |         |                       |       |       |

| V OD(DOM)            | Bus output differential voltage   | TXD = low, STB=0V, RL=50-65 Ohm, RCM open, see                                                  | 1.5     |                       | 3.0   | V     |

|                      | (dominant)                        | Figure 8-1                                                                                      |         |                       |       |       |

|                      |                                   | TXD = low, STB = 0V, RL=2240 Ohm, Rсм open, see                                                 | 1.5     |                       | 5.0   | V     |

|                      |                                   | Figure 8-1                                                                                      |         |                       |       |       |

|                      |                                   | TXD=V <sub>CC</sub> or V <sub>IO</sub> , $V_{CC} = V_{IO}$ , STB=0V, RL=open,                   | 2       | 0.5)/                 | 2     | v     |

| V <sub>O(REC)</sub>  | Bus output voltage (recessive)    | Rcм=open, CANH,CANL, see Figure 8-1                                                             | 2       | 0.5 x V <sub>CC</sub> | 3     | V     |

|                      |                                   | TXD = high, STB=0V, $R_L$ =60 $\Omega$ , $C_L$ =open, $R_{CM}$ =open,                           |         |                       |       |       |

|                      | Bus output differential voltage   | see Figure 8-1                                                                                  | -120    |                       | 12    | mV    |

| V <sub>OD(REC)</sub> | (recessive)                       | TXD = high, STB=0V, no load, CL=open, Rcm=open,                                                 | · · · · |                       |       |       |

|                      | (Tecessive)                       |                                                                                                 | -50     |                       | 50    | mV    |

|                      |                                   | see Figure 8-1                                                                                  |         |                       |       |       |

|                      |                                   | STB=V <sub>IO</sub> , RL open, Rсм open, CANH                                                   | -0.1    |                       | 0.1   | V     |

| V <sub>O(STB)</sub>  | Bus output at standby mode        | STB= V <sub>IO</sub> , RL open, Rсм open, CANL                                                  | -0.1    |                       | 0.1   | V     |

|                      |                                   | STB= V <sub>IO</sub> , RL open, Rсм open, CANH-CANL                                             | -0.2    |                       | 0.2   | V     |

|                      |                                   | TXD = low, STB=0V, CANL open, V <sub>CANH</sub> = -5V to 40V,                                   |         |                       |       |       |

|                      |                                   | see Figure 8-7                                                                                  | -100    |                       |       |       |

| OS(SS_DOM)           | Short-circuit current (dominant)  | TXD = low, STB=0V, CANH open, $V_{CANL}$ = -5V to 40V,                                          |         |                       |       | mA    |

|                      |                                   |                                                                                                 |         |                       | 100   |       |

|                      |                                   | see Figure 8-7                                                                                  |         |                       |       |       |

| IOS(SS_rec)          | Short-circuit current (recessive) | TXD = high, STB=0V , $V_{BSU}$ = CANH = CANL = -27V to                                          | -5      |                       | 5     | mA    |

| .03(33_160)          |                                   | 32V, see Figure 8-7                                                                             |         |                       |       |       |

|                      | Transient symmetry (dominant      | R <sub>L</sub> = 60 Ω, STB=0V, R <sub>CM</sub> open, C <sub>split</sub> =4.7nF, R <sub>CM</sub> |         |                       |       |       |

| V <sub>SYM</sub>     |                                   | open , TXD = 250kHz, 1MHz, 2.5M Hz, see Figure                                                  | 0.9     |                       | 1.1   | V/V   |

|                      | or recessive)                     | 8-1                                                                                             |         |                       |       |       |

|                      | DC Output symmetry (dominant      |                                                                                                 |         |                       | ·     |       |

| V <sub>SYM_DC</sub>  | or recessive)                     | RL =60 $\Omega$ , STB = 0, R <sub>CM</sub> open, see Figure 8-1                                 | -0.4    |                       | 0.4   | V     |

| CAN RECEI            |                                   |                                                                                                 |         |                       |       |       |

| CAN RECEI            | VER                               |                                                                                                 | r       |                       |       | r –   |

| V <sub>CM</sub>      | Common-mode input range           | CANH or CANL to GND, RXD output valid, see Figure                                               | -30     |                       | +30   | v     |

|                      |                                   | 8-2                                                                                             |         |                       |       | -     |

| v                    | Input differential threshold      | STB = 0V, $V_{CM}$ from -20V to 20V, see Figure 8-2                                             | 0.5     |                       | 0.9   | V     |

| V <sub>IT</sub>      | voltage at normal mode            | STB=0V, V <sub>CM</sub> from -30V to 30V, see Figure 8-2                                        | 0.4     |                       | 1.0   | V     |

|                      | Input differential threshold      | -                                                                                               |         |                       |       |       |

| V <sub>IT(HYS)</sub> | hysteresis                        | STB = 0                                                                                         |         | 120                   |       | mV    |

|                      | Input differential threshold at   |                                                                                                 |         |                       |       |       |

| V <sub>IT(STB)</sub> | standby mode for the CA-          | STB = high, $V_{CM}$ = -20V to 20V, (3≤ $V_{IO}$ ≤5.5V), see                                    | 0.4     |                       | 1.15  | v     |

| ▼11(S1B)             | -                                 | Figure 8-2                                                                                      | 0.4     |                       | 1.15  | v     |

|                      | IF1042VS-Q1                       |                                                                                                 |         |                       |       |       |

|                      | Input differential threshold at   |                                                                                                 |         |                       | 4 4 5 |       |

| V <sub>IT(STB)</sub> | standby mode for the CA-          | STB = high, $V_{CM}$ = -20V to 20V, see Figure 8-2                                              | 0.4     |                       | 1.15  | V     |

|                      | IF1042S-Q1 devices                |                                                                                                 |         |                       |       |       |

|                      | Receiver dominant state           |                                                                                                 |         |                       |       |       |

| V <sub>DIFF_D</sub>  | differential input voltage range  | STB = 0V, $V_{CM}$ from -20V to 20V, see Figure 8-2                                             | 0.9     |                       | 9     | v     |

|                      | in normal mode (bus biasing       | ,                                                                                               |         |                       | -     | .<br> |

|                      | active)                           |                                                                                                 |         |                       |       |       |

|                      | Receiver recessive state          |                                                                                                 |         |                       |       |       |

|                      | differential input voltage range  | STB=0V, V <sub>CM</sub> from -30V to 30V, see Figure 8-2                                        | -4      |                       | 0.5   | v     |

| /DIFF_R              |                                   |                                                                                                 |         |                       |       | - V   |

| V <sub>DIFF_R</sub>  | in normal mode (bus biasing       | 51B-00, VCM 110111-500 to 500, see Figure 8-2                                                   | -4      |                       | 0.5   | ·     |

#### Shanghai Chipanalog Microelectronics Co., Ltd.

| V <sub>DIFF_D(STB)</sub> | Receiver dominant state<br>differential input voltage range<br>in standby mode (bus biasing<br>inactive)  | STB = high, $V_{CM}$ = -20V to 20V, (3 $\leq$ V <sub>10</sub> $\leq$ 5.5V), see Figure 8-2 | 1.15 |    | 9   | v  |

|--------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------|----|-----|----|

| Vdiff_r(stb)             | Receiver recessive state<br>differential input voltage range<br>in standby mode (bus biasing<br>inactive) | STB = high, $V_{CM}$ = -20V to 20V, (3 $\leq V_{10} \leq 5.5V$ ), see Figure 8-2           | -4   |    | 0.4 | v  |

| R <sub>IN</sub>          | CANH/CANL input resistance                                                                                | TXD = high, STB = 0, $V_{CM}$ = -30V to 30V                                                | 10   |    | 40  | kΩ |

| R <sub>DIFF</sub>        | Differential input resistance                                                                             | TXD = high, STB = 0, $V_{CM}$ = -30V to 30V                                                | 20   |    | 80  | kΩ |

| R <sub>DIFF</sub> (M)    | Input resistance matching                                                                                 | V <sub>CANH</sub> = V <sub>CANL</sub> =5V                                                  | -3   |    | 3   | %  |

| I <sub>LKG</sub>         | Input Leakage Current                                                                                     | $V_{IO} = V_{CC} = 0V$ , $V_{CANH} = V_{CANL} = 5V$                                        |      |    | 5   | μΑ |

| CIN                      | Input capacitance                                                                                         | CANH or CANL to GND, TXD= $V_{CC}$ , $V_{IO} = V_{CC}$ , STB = 0                           |      | 24 |     | рF |

| C <sub>IN_DIFF</sub>     | Differential input capacitance                                                                            | CANH to CANL, TXD = High                                                                   |      | 12 |     | рF |

#### 7.6. Switching Characteristics

|                           | PARAMETER                            | TEST CONDITIONS                                             | MIN | ТҮР | MAX | UNIT |

|---------------------------|--------------------------------------|-------------------------------------------------------------|-----|-----|-----|------|

| DRIVER                    |                                      |                                                             |     |     |     |      |

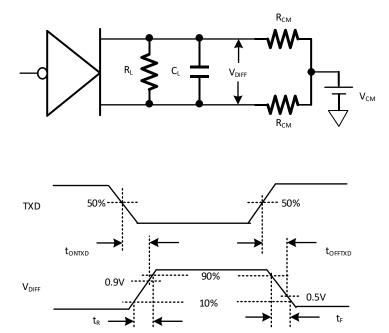

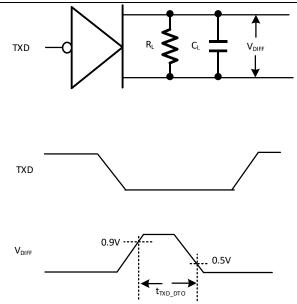

| t <sub>ontxd</sub>        | TXD propagation delay                | STB = 0, RL=60 Ω, CL=100pF, see Figure 8-1                  |     | 55  |     | nc   |

|                           | (recessive to dominant)              | STB = 0, RL=00 12, CL=100pr, see Figure 8-1                 |     | 55  |     | ns   |

| t <sub>offtxd</sub>       | TXD propagation delay                | STB = 0, RL=60 Ω, CL=100pF, see Figure 8-1                  |     | 75  |     | ns   |

|                           | (dominant to recessive)              | 51B - 0, RE-00 32, CE-100pr, see Figure 8-1                 |     | 75  |     | 113  |

| t <sub>DOM</sub>          | TXD-dominant Timeout                 | RL=60 Ω, CL open, see Figure 8-5                            | 2.5 | 6.8 | 10  | ms   |

| RECEIVER                  |                                      |                                                             |     |     |     |      |

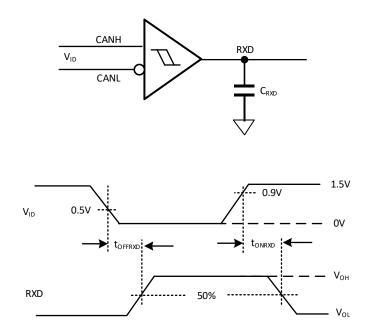

| tonrxd                    | RXD propagation delay                | STB = 0, Crxd=15pF, see Figure 8-2                          |     | 90  |     | ns   |

|                           | (recessive to dominant)              | 51B = 0, 000 - 1501, 500 Figure 0 2                         |     | 50  |     | 115  |

| t <sub>offrxd</sub>       | RXD Propagation delay                | STB = 0, Crxd=15pF, see Figure 8-2                          |     | 100 |     | ns   |

|                           | (dominant to recessive)              |                                                             |     | 100 |     | 113  |

| DEVICE                    | 1                                    |                                                             |     |     |     | - I  |

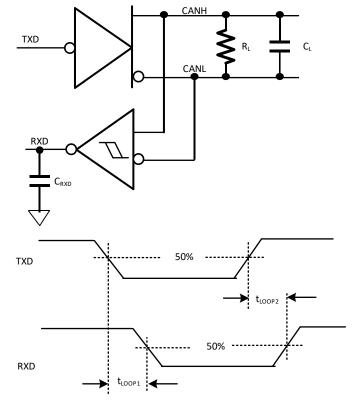

|                           | Total loop delay, driver input       |                                                             |     |     |     |      |

| t <sub>loop1</sub>        | (TXD) to receiver output (RXD),      | RL=60 $\Omega$ , CRXD=15pF, CL=100pF, see Figure 8-3        |     | 125 | 255 | ns   |

|                           | recessive to dominant                |                                                             |     |     | -   |      |

|                           | Total loop delay, driver input       |                                                             |     |     |     |      |

| t <sub>loop2</sub>        | (TXD) to receiver output (RXD),      | RL=60 $\Omega$ , CRXD=15pF, CL=100pF, see Figure 8-3        |     | 155 | 255 | ns   |

|                           | dominant to recessive                |                                                             |     |     |     |      |

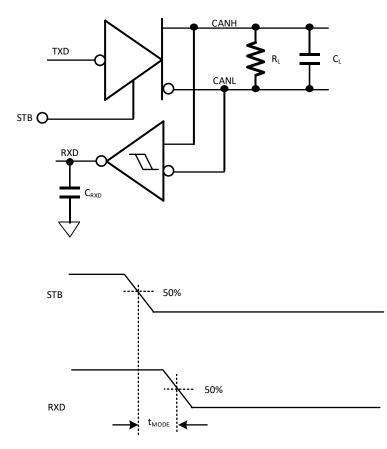

| t <sub>MODE</sub>         | Mode change time, from normal        | see Figure 8 -4                                             |     | 12  | 45  | μs   |

| WIDDE                     | to silent or from silent to normal   |                                                             |     |     | .0  | μo   |

| Ŧ                         | Filter time for a valid wake-up      |                                                             | 0.5 |     | 4.0 |      |

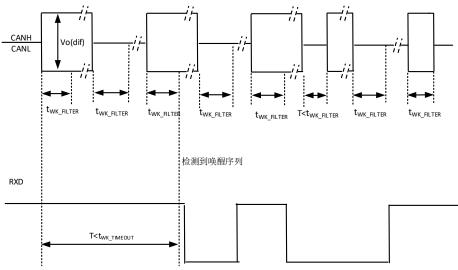

| Twk_FILTER                | pattern                              | See Figure 9-4.                                             | 0.5 |     | 1.8 | μs   |

| T <sub>WK_FILTEROUT</sub> | Bus wake-up timeout                  | See Figure 9-4.                                             | 0.8 |     | 10  | ms   |

| FD TIMING                 |                                      | -                                                           |     |     |     |      |

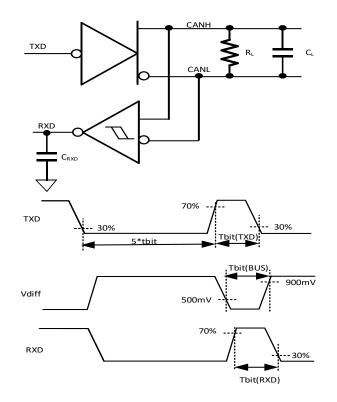

|                           | Bit time on CAN bus output pins      | STB = 0, RL = 60 $\Omega$ , CL=100pF, CRXD=15pF, see Figure |     |     | ·   |      |

| t <sub>bit(bus)</sub>     | with $t_{BIT(TXD)} = 500 \text{ ns}$ | 8-6                                                         | 435 |     | 530 | ns   |

|                           | Bit time on CAN bus output pins      | STB = 0, RL = 60 Ω, CL=100pF, CRXD =15pF, see               |     |     |     |      |

| t <sub>bit(bus)</sub>     | with $t_{BIT(TXD)} = 200 \text{ ns}$ | Figure 8-6                                                  | 155 |     | 210 | ns   |

|                           | Bit time on RXD output pins with     | STB = 0, RL = 60 Ω, CL=100pF, CRXD =15pF, see               | 463 |     |     |      |

| t <sub>bit(rxd)</sub>     | t <sub>BIT(TXD)</sub> = 500 ns       | Figure 8-6                                                  | 400 |     | 550 | ns   |

|                           | Bit time on RXD output pins with     | STB = 0, RL = 60 Ω, CL=100pF, CRXD =15pF, see               | 420 |     | 220 |      |

| t <sub>bit(rxd)</sub>     | t <sub>BIT(TXD)</sub> = 200 ns       | Figure 8-6                                                  | 120 |     | 220 | ns   |

| +                         | Receiver timing symmetry with        | STB = 0, RL = 60 Ω, CL=100pF, CRXD =15pF, see               | 65  |     | 40  |      |

| t <sub>rec</sub>          | t <sub>BIT(TXD)</sub> = 500ns        | Figure 8-6                                                  | -65 |     | 40  | ns   |

| +                         | Receiver timing symmetry with        | STB = 0, RL = 60 Ω, CL=100pF, CRXD =15pF, see               | 45  |     | 15  | nc   |

| t <sub>rec</sub>          | t <sub>BIT(TXD)</sub> = 200ns        | Figure 8-6                                                  | -45 |     | 15  | ns   |

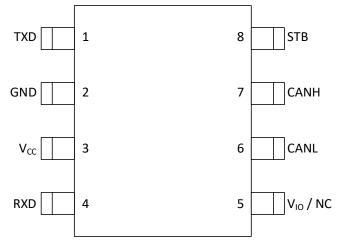

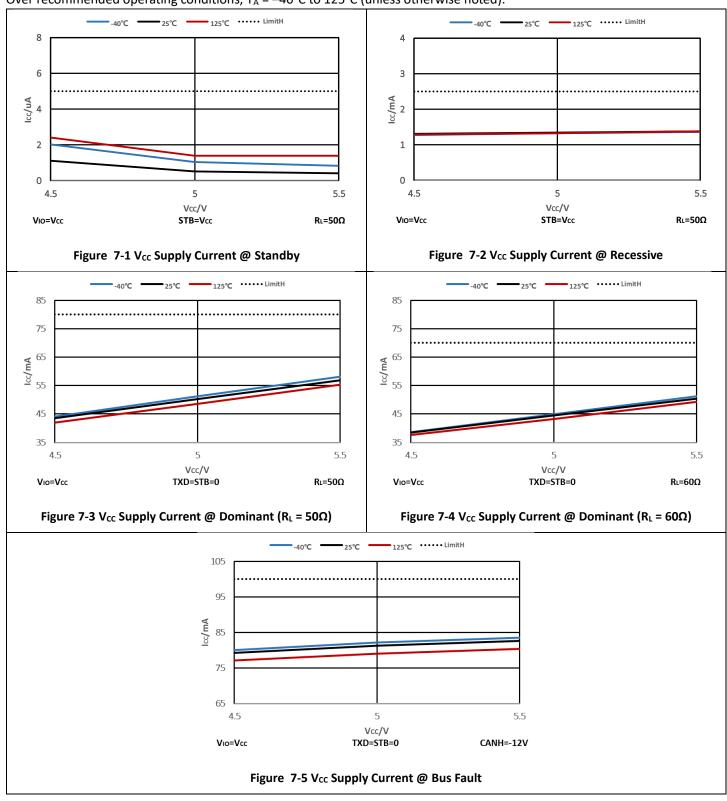

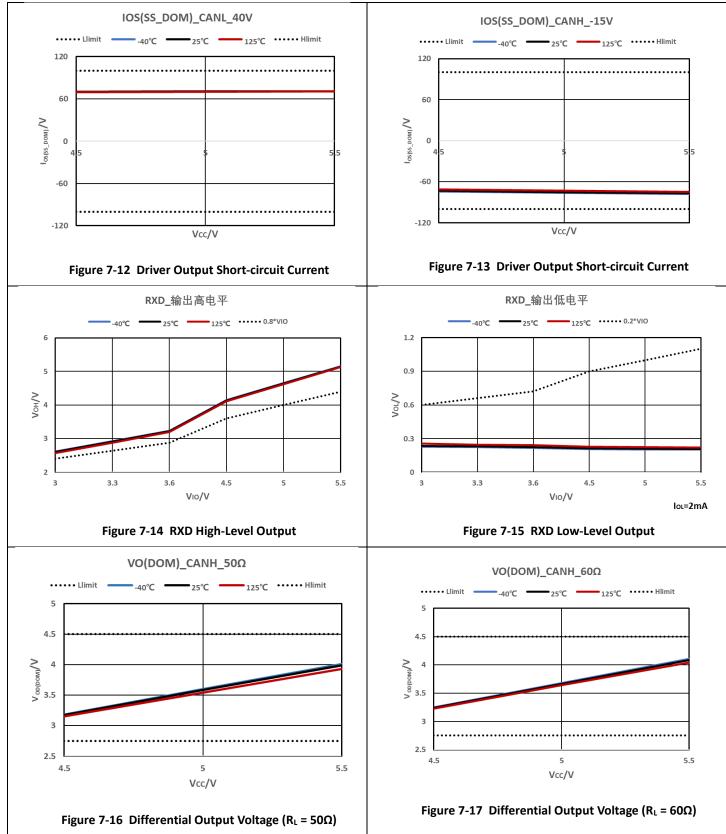

## 7.7. Typical Operating Characteristics and Waveforms

#### Shanghai Chipanalog Microelectronics Co., Ltd.

#### Typical Operating Characteristics and Waveforms (continued)

### Typical Operating Characteristics and Waveforms (continued)

Shanghai Chipanalog Microelectronics Co., Ltd.

## 8. Parameter Measurement Information

Figure 8-1 Transmitter Test Circuit and Timing Diagram

Figure 8-2 Receiver Test Circuit and Measurement

Figure 8-3 TXD to RXD Loop Delay

Figure 8-5 Transmitting Dominant Timeout Timing Diagram

Figure 8-7 Driver Short Circuit Current Test Circuit and Measurement

#### Shanghai Chipanalog Microelectronics Co., Ltd.

#### 9. Detailed Description

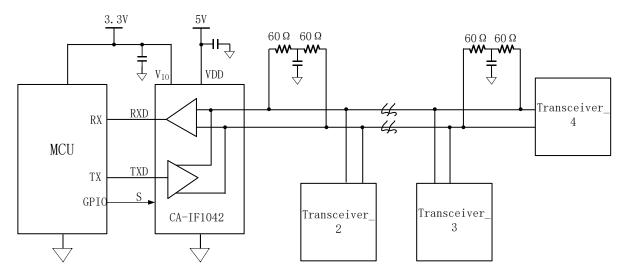

The CA-IF1042x family of devices is fault-protected Controller Area Network (CAN) transceiver, meets the ISO11898-2 (2016) high speed CAN physical layer standard. These devices are designed for harsh industrial and automotive applications with a number of integrated robust protection features set that improve the reliability of end equipment. All devices are fault protected up to ±70V for the bus pins, making them ideal for applications where overvoltage protection is required. A common-mode voltage range of ±30V enables communication in noisy environments where there are ground plane differences between different systems. Dominant timeout prevents the bus from being blocked by a hung-up microcontroller, and the outputs CANH and CANL are short-circuit current-limited and protected against excessive power dissipation by thermal shutdown circuitry that places the driver outputs in a high-impedance state.

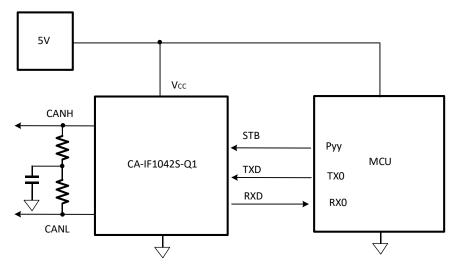

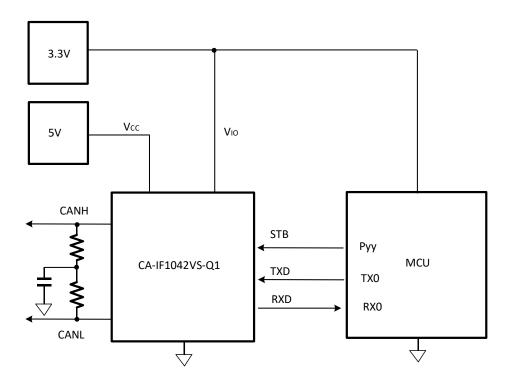

A separate input  $V_{IO}$  allows the CA-IF1042VS-Q1 devices to communicate with logic systems down to 3.0V while operating up to a +5.5V bus supply. This provides a reduced input voltage threshold to the TXD and STB inputs, and provides a logic-high output at RXD compatible with the microcontroller's supply rail. The logic compatibility eliminates external logic level translator and longer propagation delay due to level shifting. Connect  $V_{IO}$  to  $V_{CC}$  to operate with +5V logic systems.

The CA-IF1042x devices can operate up to 5Mbps data rate and support CAN FD. However, the maximum data rate is limited by the bus loading, number of nodes, cable length etc. factors, for CAN network design, margin must be given for signal loss across the system and cabling, parasitic loadings, timing, network imbalances, ground offsets and signal integrity thus a practical maximum data rate, number of nodes often lower than the theoretical value.

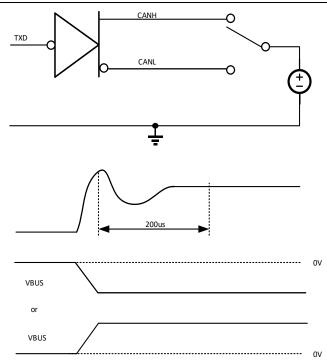

#### 9.1. CAN Bus Status

The CAN bus has two states: dominant and recessive. In the dominant state (a zero bit, used to determine message priority), CANH-CANL are defined to be logic '0' when the voltage across them is between +1.5V and +3V (higher than 0.9V). In the recessive state (a 1-bit and the state of the idle bus), the driver is defined to be logic '1' when differential voltage is between - 120mV and +12mV, or when it is near zero(lower than 0.5V), see Figure 9-1. for the bus logic state voltage definition.

When STB is set high, the chip will enter low-power standby mode, and at this time, the bus will be biased to ground by internal resistance, as shown in Figure 9-1.

Figure. 9-1 Bus status diagram

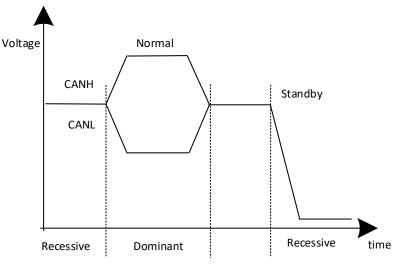

#### 9.2. Receiver

The receiver of CA-IF1042x family of devices includes a main receiver to support normal bi-directional communication and a low-power receive channel to monitor the bus line and detect the wakeup event on the bus line during standby mode. In normal operation (STB = low), the main receiver reads the differential input from the bus line (CANH and CANL) and transfers this data as a single-ended output RXD to the CAN controller. The internal comparator senses the difference voltage  $V_{DIFF} = (V_{CANH}-V_{CANL})$ , with respect to an internal threshold of 0.7V. If  $V_{DIFF} > 0.9V$ , a logic-low is present on RXD; If  $V_{DIFF} < 0.5V$ , a logic-high is present. The CANH and CANL common-mode range is ±30V in normal mode. See *Figure 9-2* for the receiver input bias circuit.

Drive the STB pin high or leave it open for standby mode, in this case, the main receiver is disabled and the low-power receive channel is enabled. This switches the receiver to a low current and low-speed state. The bus line is monitored by a low-power differential comparator to detect and recognize a wakeup event on the bus line. RXD is logic High until a valid wake-up is received. Once a valid remote wake-up event occurred, RXD transition to logic Low.

RXD is a logic-high when CANH and CANL are shorted or terminated and un-driven in both normal mode and standby mode, see *Table 9-1* for more details about the receiver truth table.

| DEVICE MODE         | $V_{ID} = V_{CANH} - V_{CANL}$ | BUS STATE     | RXD                                                         |

|---------------------|--------------------------------|---------------|-------------------------------------------------------------|

|                     | V <sub>ID</sub> ≥0.9V          | Dominant      | Low                                                         |

| Normal<br>STB = Low | 0.5V < V <sub>ID</sub> <0.9V   | Indeterminate | Indeterminate                                               |

| 510 - Low           | $V_{ID} \le 0.5V$              | Recessive     | High                                                        |

| Standby             | V <sub>ID</sub> > 1.15V        | Dominant      | Low if a remote wake event occurred, otherwise output High. |

| STB = High or open  |                                |               | Indeterminate                                               |

|                     | $V_{ID} \leq 0.4V$             | Recessive     | High                                                        |

| Any                 | Open (V <sub>ID</sub> ≈ 0V)    | Open          | High                                                        |

#### Table 9-1 Receiver Truth Table

Figure. 9-2 Receiver Input/Transmitter Output Bias Circuit

#### 9.3. Transmitter

In normal operation (STB = Low), the transmitter converts a single-ended input signal (TXD) from the local CAN controller to differential outputs for the bus lines CANH and CANL. The truth table for the transmitter is provided in *Table 9-2*. The CA-IF1042x family of devices protects the transmitter output stage against a short-circuit to a positive or negative voltage by limiting the driver current. Thermal shutdown further protects the devices from excessive temperatures that may result from a short circuit. The transmitter returns to normal operation once the short is removed and the junction temperature drops at least the thermal shutdown hysteresis temperature below the thermal shutdown temperature of the device.

#### Shanghai Chipanalog Microelectronics Co., Ltd.

Drive the STB pin high for standby mode, the transmitter is disabled and put the bus in high-impedance with internal weak pull-down to ground, see *Figure 9-2*.

| 1            | INPUT TXD LOW TIME |                    | OUTF               | τυν                | BUS STATE             |

|--------------|--------------------|--------------------|--------------------|--------------------|-----------------------|

| STB          | TXD                |                    | CANH               | CANL               | BUSSIAIE              |

|              | Low                | < t <sub>DOM</sub> | High               | Low                | Dominant              |

| Low          | Low                | > t <sub>DOM</sub> | V <sub>cc</sub> /2 | V <sub>cc</sub> /2 | Recessive             |

|              | High or Open       | X1                 | V <sub>cc</sub> /2 | V <sub>cc</sub> /2 | Recessive             |

| High or Open | X1                 | X1                 | High-Z             | High-Z             | Weak pull-down to GND |

#### Table 9-2 Transmitter Truth Table (When Not Connected to the Bus)

X = Don't care

#### 9.4. Protection Functions

#### 9.4.1. Undervoltage Lockout

Both the CA-IF1042S-Q1 and the CA-IF1042VS-Q1 family of devices have undervoltage detection on  $V_{CC}$  supply terminal, the CA-IF1042VS-Q1 devices also feature undervoltage detection on  $V_{IO}$  supply terminal, that place the device in protected mode during an undervoltage event on  $V_{CC}$  or/and  $V_{IO}$ , see *Table 9-3* and Table 9-4.

For the CA-IF1042S-Q1, if the supply voltage  $V_{CC}$  is less than  $V_{UN_vCC}$ , will put the device into protected state and leave the bus in high-impedance as shown in *Table 9-3*. Once an undervoltage condition is cleared on  $V_{CC}$  and the supply voltage has returned to a valid level, the devices transition to normal mode after the  $t_{ONTXD}$  time has expired. The host controller should not attempt to send or receive messages until the  $t_{ONTXD}$  time has expired.

| V <sub>cc</sub>                                       | DEVICE STATE                            | BUS OUTPUT            | RXD                                  |  |  |  |  |  |  |  |  |

|-------------------------------------------------------|-----------------------------------------|-----------------------|--------------------------------------|--|--|--|--|--|--|--|--|

| S M                                                   | STB=V <sub>CC</sub> , Standby           | Weak pull-down to GND | High until valid wake-up is received |  |  |  |  |  |  |  |  |

| > V <sub>uv_vcc</sub>                                 | STB=V <sub>CC</sub> ,Normal             | Per TXD               | Mirrors Bus                          |  |  |  |  |  |  |  |  |

|                                                       | STB=V <sub>CC</sub> , Standby           | Weak pull-down to GND | High until valid wake-up is received |  |  |  |  |  |  |  |  |

| <v<sub>uv_vcc &amp; &gt;V<sub>uv_vcc_sd</sub></v<sub> | STB=V <sub>CC</sub> , Protected mode    | Weak pull-down to GND | Recessive                            |  |  |  |  |  |  |  |  |

| < V <sub>uv_vcc_sd</sub>                              | < V <sub>uv_vcc_sd</sub> Protected mode |                       | High Impedance                       |  |  |  |  |  |  |  |  |

Table 9-3 CA-IF1042S-Q1 Undervoltage Lockout

For the CA-IF1042VS-Q1 devices, see *Table 9-4* for the undervoltage lockout status. Once the undervoltage condition is cleared and the supply voltage has returned to a valid level, the devices transition to normal mode after the  $t_{MODE}$  time has expired. The host controller should not attempt to send or receive messages until the  $t_{MODE}$  time has expired.

#### Table 9-4 CA-IF1042VS-Q

#### Undervoltage Lockout

| V <sub>cc</sub>       | V <sub>IO</sub>      | DEVICE STATE               | BUS OUTPUT            | RXD                                  |

|-----------------------|----------------------|----------------------------|-----------------------|--------------------------------------|

| > V <sub>UV_VCC</sub> | > V <sub>UV_10</sub> | Standby (STB = high)       | Weak pull-down to GND | High until valid wake-up is received |