## 3.0V to 5.5V RS485/RS422 Transceivers with ±20kV ESD Protection

#### 1. Features

- High-Performance and Compliant with RS-485 EIA/ TIA-485 Standard

- Low EMI 500kbps Data Rate (CS48505Ax) and up to 20Mbps (CS48520Ax) High-Speed Data Rate

- 1/8 Unit Load Enables up to 256 Nodes on the Same Bus

- Integrated Protection for Robust Communication

- -7V to +12V Common-Mode Voltage Range

- ±20kV Human Body Model ESD Protection and ±6kV Contact Discharge IEC 61000-4-2 ESD Protection on A/B pins

- Short-Circuit Protection

- Thermal Shutdown

- True Fail-Safe Guarantees Known Receiver Output State

- Glitch-free during Power on/Power off

- Output Level is Compatible with Profibus Standard

- |V<sub>OD</sub>| > 2.1V @ 5V Supply Voltage

- Low Power

- Low Supply Current (0.9mA, typ.)

- Shutdown Current < 5µA

- 3V to 5.5V Supply Voltage Range

- Wide Operating Temperature Range: -40°C to 125°C

- 8 pin SOIC, 8 pin MSOP and 8 pin DFN Packages

#### 2. Applications

- Factory Automation & Control

- Grid Infrastructure

- Home and Building Automation

- Video Surveillance

- Smart Meters

- Process Control

- Telecommunication Equipment

#### 3. General Description

The CS485xxA family of devices are low-power half-duplex transceivers for RS-485/RS-422 communications in harsh environments. All devices feature ±20kV electro-static discharge (ESD) protection for the bus pins (A and B), eliminating the need for additional system level protection components.

The CS485xxA family of devices contain one driver( $T_X$ ) and one receiver( $R_X$ ), operates over the +3V to +5.5V supply range, making these devices convenient for designers to use one part with either +3.3V or +5V supply systems. The CS48520Ax devices can transmit and receive at data rate up to 20Mbps, while the CS48505Ax devices are specified for data rate up to 500kbps. These devices also include fail-safe circuitry, guaranteeing a logic-high receiver output when the receiver inputs are shorted or open.

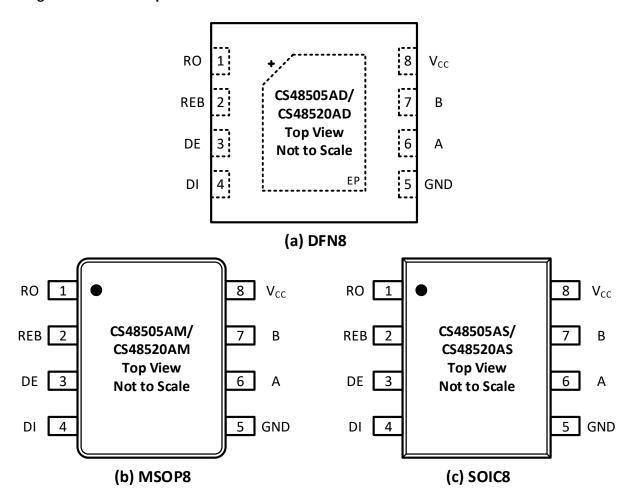

All devices are specified over the -40°C to +125°C wide operating temperature range and are available in small 8-pin MSOP, 8-pin DFN packages for space constrained applications and 8-pin SOIC for drop-in compatibility design.

#### **Device Information**

| Part number | Package | Package size<br>(NOM) |  |  |

|-------------|---------|-----------------------|--|--|

| CS48505AS   | SOIC8   | 3.9mm*4.9mm           |  |  |

| CS48520AS   | 30108   | 3.311111 4.3111111    |  |  |

| CS48505AM   | MSOP8   | 3mm*3mm               |  |  |

| CS48520AM   | IVISOPO | 5111111 5111111       |  |  |

| CS48505AD   | DFN8    | 3mm*3mm               |  |  |

| CS48520AD   | DEINO   | 3111111 3111111       |  |  |

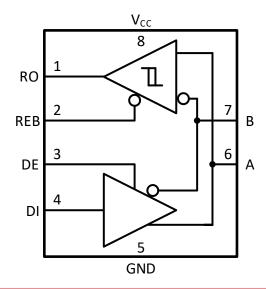

#### Simplified Block Diagram

## 4. Ordering Information

**Table 4-1. Ordering Information**

| Part #    | Full/Half-Duplex | Data Rate(Mbps) | Number of Nodes<br>on Bus | Package  |

|-----------|------------------|-----------------|---------------------------|----------|

| CS48505AS | Half-Duplex      | 0.5             | 256                       | SOIC8(S) |

| CS48520AS | Half-Duplex      | 20              | 256                       | SOIC8(S) |

| CS48505AM | Half-Duplex      | 0.5             | 256                       | MSOP8(M) |

| CS48520AM | Half-Duplex      | 20              | 256                       | MSOP8(M) |

| CS48505AD | Half-Duplex      | 0.5             | 256                       | DFN8(D)  |

| CS48520AD | Half-Duplex      | 20              | 256                       | DFN8(D)  |

# **Table of Contents**

| 1. | Features               |                                       |   |  |  |

|----|------------------------|---------------------------------------|---|--|--|

| 2. | Appl                   | lications                             | 1 |  |  |

| 3. | Gen                    | eral Description                      | 1 |  |  |

| 4. | . Ordering Information |                                       | 2 |  |  |

| 5. | Revi                   | sion History                          | 3 |  |  |

| 6. | Pin (                  | Configuration and Descriptions        | 4 |  |  |

| 7. | Spec                   | cification                            | 5 |  |  |

|    | 7.1.                   | Absolute Maximum Ratings <sup>1</sup> | 5 |  |  |

|    | 7.2.                   | ESD Ratings                           | 5 |  |  |

|    | 7.3.                   | Recommended Operating Conditions      | 5 |  |  |

|    | 7.4.                   | Thermal Information                   | 5 |  |  |

|    | 7.5.                   | Electrical Characteristics            | 6 |  |  |

|    | 7.6.                   | CS48505Ax Switching Characteristics   | 7 |  |  |

|    | 7.7.                   | CS48520Ax Switching Characteristics   | 7 |  |  |

|    | 7 2                    | Typical Characteristics               | Q |  |  |

| 8.  | Para   | mete   | er Measurement Information     | 11 |

|-----|--------|--------|--------------------------------|----|

| 9.  | Deta   | iled I | Description                    | 14 |

|     | 9.1.   | Ove    | rview                          | 14 |

|     | 9.2.   | Dev    | ice Functional Modes           | 14 |

|     | 9.     | 2.1.   | Driver                         | 14 |

|     | 9.     | 2.2.   | Fail-Safe Receiver             | 14 |

| 10  | . App  | licati | on Information                 | 15 |

| 11. | Pack   | kage   | Information                    | 16 |

|     | 11.1.  | SOI    | C8 Package Outline             | 16 |

|     | 11.2.  | MSC    | DP8 Package Outline            | 17 |

|     | 11.3.  | DFN    | 8 Package Outline              | 18 |

| 12  | . Sold | ering  | g Temperature (reflow) Profile | 19 |

| 13. | . Таре | and    | Reel Information               | 20 |

| 14. | . Impo | ortan  | t statement                    | 21 |

## 5. Revision History

| Revision Number | Description                                                                                 | Page Changed |

|-----------------|---------------------------------------------------------------------------------------------|--------------|

| Version 1.00    | N/A                                                                                         | N/A          |

|                 | Update EFT items                                                                            | P5           |

| Version 1.01    | Increase the absolute maximum rated value of the differential voltage between buses A and B | P5           |

|                 | Remarks on adding test conditions for RI bus input impedance                                | P6           |

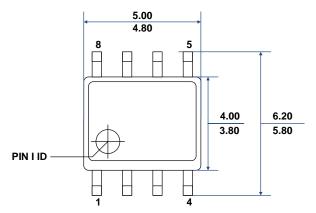

## 6. Pin Configuration and Descriptions

Figure 6-1. CS485xxA pin configuration

Table 6-1 CS485xxA pin description

| Pin Name        | Pin Number | Description                                                                                                           |

|-----------------|------------|-----------------------------------------------------------------------------------------------------------------------|

| RO              | 1          | Receiver data output. With REB low, RO is high when $(V_A - V_B) > V_{TH+}$ and is low when $(V_A - V_B) < V_{TH-}$ . |

| KO              | 1          | RO is high impedance when REB is high.                                                                                |

|                 |            | Receiver output enable. Drive REB low or connect to GND to enable receiver. Drive REB high or leave                   |

| REB             | 2          | open to disable the receiver and put RO in high impedance. Drive REB high and DE low to force the IC                  |

|                 |            | into low-power shutdown mode.                                                                                         |

| DE              | 3          | Driver output enable. Drive DE high to enable the driver. Drive DE low or leave open to disable the                   |

| DL              | 3          | driver. Drive REB high and DE low to force the IC into low-power shutdown mode.                                       |

|                 |            | Driver data input. With DE high, a logic low on DI forces the noninverting output (A) low and the                     |

| DI              | 4          | inverting output (B) high; a logic high on DI forces the noninverting output high and the inverting                   |

|                 |            | output low.                                                                                                           |

| GND             | 5          | Ground.                                                                                                               |

| Α               | 6          | Noninverting RS-485/RS-422 driver output/receiver input.                                                              |

| В               | 7          | Inverting RS-485/RS-422 driver output/receiver input.                                                                 |

| V <sub>CC</sub> | 8          | Power supply input. Bypass $V_{CC}$ to GND with at least $0.1\mu F$ capacitor as close to the device as possible.     |

| EP              |            | Exposed Pad (DFN8 package Only). Connect EP to GND.                                                                   |

## 7. Specification

## 7.1. Absolute Maximum Ratings<sup>1</sup>

|                              | Parameters                           | Minimum value | Maximum<br>value | Unit |

|------------------------------|--------------------------------------|---------------|------------------|------|

| V <sub>CC</sub> <sup>2</sup> | Power supply voltage                 | -0.5          | 7.0              | V    |

| A, B <sup>2</sup>            | Voltage on the bus                   | -8            | 13               | V    |

| A-B                          | Differential voltage between A and B | -8            | 13               | V    |

| DE, DI, REB                  | Logic control voltage                | -0.3          | $V_{CC} + 0.3^3$ | V    |

| RO                           | Logic voltage at RO                  | -0.3          | $V_{CC} + 0.3^3$ | V    |

| Tj                           | Junction temperature                 |               | 150              | °C   |

| T <sub>STG</sub>             | Storage temperature range            | -65           | 150              | °C   |

#### Notes:

- 1. The stresses listed under "Absolute Maximum Ratings" are stress ratings only, not for functional operation condition. Exposure to absolute maximum rating conditions for extended periods may cause permanent damage to the device.

- 2. All voltage values are with respect to the ground terminal (GND) and are peak voltage values unless otherwise specified.

- 3. Maximum voltage must not be exceed 7V.

## 7.2. ESD Ratings

|                  |                          | Parameters                                                                              | Value | Unit |

|------------------|--------------------------|-----------------------------------------------------------------------------------------|-------|------|

|                  |                          | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, bus pins (A, B) to GND <sup>1</sup> | ±20   |      |

| V <sub>ESD</sub> | Electrostatic discharge  | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all other pins <sup>1</sup>         | ±8    |      |

| • E3D            | Electrostatic discriatge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>2</sup>  | ±2    | kV   |

|                  |                          | Contact Discharge, per IEC 61000-4-2, bus pins (A, B) to GND                            | ±6    |      |

| V <sub>EFT</sub> |                          | per IEC 61000-4-4, bus pins (A, B) to GND                                               | ±4    |      |

#### Notes:

- 1. Per JEDEC document JEP155, 500V HBM allows safe manufacturing of standard ESD control process.

- 2. Per JEDEC document JEP157, 250V CDM allows safe manufacturing of standard ESD control process.

## 7.3. Recommended Operating Conditions

|                   | Parameters                        | Minimum<br>value | Typical<br>value | Maximum<br>value | Unit |

|-------------------|-----------------------------------|------------------|------------------|------------------|------|

| V <sub>cc</sub>   | Power supply                      | 3.0              | 5.0              | 5.5              | V    |

| V <sub>IN</sub>   | Input voltage at any bus terminal | -7               |                  | 12               | V    |

| V <sub>IL</sub>   | Low-level input voltage           | 0                |                  | 0.8              | V    |

| V <sub>IH</sub>   | High-level input voltage          | 2.0              |                  | V <sub>cc</sub>  | V    |

| R <sub>L</sub>    | Differential load resistance      | 54               |                  |                  | Ohm  |

| 1/t <sub>UI</sub> | Signaling rate: CS48505Ax         |                  |                  | 500              | kbps |

| 1/t <sub>UI</sub> | Signaling rate: CS48520Ax         |                  |                  | 20               | Mbps |

| T <sub>A</sub>    | Operating ambient temperature     | -40              |                  | 125              | °C   |

| Tı                | Junction temperature              | -40              |                  | 150              | °C   |

## 7.4. Thermal Information

| THERMAL METRIC  |                                        | SOIC8 | MSOP8 | DFN8 | Unit |

|-----------------|----------------------------------------|-------|-------|------|------|

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance | 120   | 160   | 45   | °C/W |

## 7.5. Electrical Characteristics

All typical specs are at  $V_{CC} = 5V$ ,  $T_A = 25$ °C, Min/Max specs are over recommended operating conditions unless otherwise specified.

| Driver   V <sub>OD</sub>      |                                                                 |                                                                                  |                                     |                       |                       |      |    |

|-------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------|-----------------------|-----------------------|------|----|

| V <sub>OD</sub>               |                                                                 |                                                                                  |                                     |                       |                       |      |    |

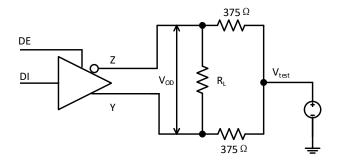

| V <sub>OD</sub>               |                                                                 | $R_L = 60 \Omega$ , $-7 V \le V_{test} \le 12 V$                                 | V (see Figure 8-1)(1)               | 1.5                   | 3.6                   |      | V  |

| V <sub>OD</sub>               |                                                                 | $R_L = 60 \Omega$ , $-7 V \le V_{test} \le 12 V_{test}$                          | V , 4.5 V ≤ V <sub>CC</sub> ≤ 5.5 V | 2.4                   | 2.6                   |      |    |

|                               | Differential output voltage                                     | (see Figure 8-1)                                                                 |                                     | 2.1                   | 3.6                   |      |    |

|                               |                                                                 | $R_L = 100 \Omega$ , $C_L = 50pF$ (see                                           | Figure 8-2)                         | 2                     | 4.2                   |      | V  |

|                               |                                                                 | $R_L = 54 \Omega m C_L = 50 pF$ (see                                             | Figure 8-2)                         | 1.5                   | 3.6                   |      | V  |

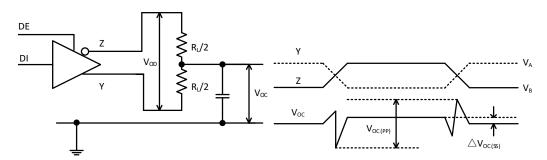

| $\Lambda I V \cap I$          | Change in differential output voltage                           |                                                                                  |                                     | -50                   |                       | 50   | mV |

| Voc                           | Common-mode output voltage                                      |                                                                                  |                                     | 1                     | V <sub>CC</sub> /2    | 3.3  | V  |

| $\Delta V_{\text{OC(SS)}}$    | Change in steady-state common-mode output voltage               | $R_L$ = 54 $\Omega$ or $100\Omega$ , $C_L$ = 50pF, (see Figure 8-2)              |                                     | -50                   |                       | 50   | mV |

| $\Delta V_{\text{OC(pp)}}$    | Change in steady-state common-mode output voltage, peak to peak |                                                                                  |                                     |                       | 450                   |      |    |

| los                           | Short-circuit output current                                    | DE = $V_{CC}$ , -7 V $\leq V_{O} \leq 12$ V                                      |                                     |                       | 100                   | 150  | mA |

| Receiver                      |                                                                 |                                                                                  | 1                                   |                       |                       | ,    |    |

| I <sub>I</sub>                | Bus input current                                               | DE = 0 V, V <sub>CC</sub> = 0 V or 5 V                                           | V <sub>I</sub> = 12V                |                       | 75                    | 125  | μΑ |

| 11                            | bus input current                                               | DL = 0 v, v(( = 0 v 01 3 v                                                       | V <sub>I</sub> = -7V                | -100                  | -40                   |      | μΑ |

| R <sub>I</sub> R              | eceiver Input Resistance                                        | $V_A = -7V$ , $V_B = 12V^1$ or $V_A = 12V$ , $V_B = -7V^1$                       |                                     | 96                    |                       |      | kΩ |

| V/ <del></del>                | Receiver differential threshold voltage rising                  |                                                                                  |                                     |                       | -110                  | -50  | mV |

| V                             | Receiver differential threshold voltage falling                 | Over common-mode rang                                                            | e                                   | -200                  | -140                  |      | mV |

| V <sub>HYS</sub> <sup>2</sup> | Receiver input hysteresis                                       |                                                                                  |                                     |                       | 30                    |      | mV |

| V <sub>OH</sub>               | Output high voltage                                             | I <sub>OH</sub> = -4mA                                                           |                                     | V <sub>CC</sub> – 0.5 | V <sub>cc</sub> – 0.3 |      | V  |

| V <sub>OL</sub>               | Output low voltage                                              | I <sub>OH</sub> = 4mA                                                            |                                     |                       | 0.2                   | 0.4  | V  |

| O7B                           | Output high-impedance current                                   | $V_0 = 0 \text{ V or } V_{CC}$ , REB = $V_{CC}$                                  |                                     | -1                    |                       | 1    | μА |

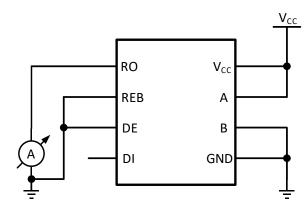

| I <sub>OSR</sub>              | Receiver output short current                                   | REB = DE = OV, see Figur                                                         | re 8-3                              |                       |                       | 95   | mA |

| Input Logic                   |                                                                 |                                                                                  |                                     |                       |                       |      |    |

| I <sub>IN</sub>               | Logic Input current                                             | $3 \text{ V} \le \text{V}_{CC} \le 5.5 \text{ V}, 0 \text{ V} \le \text{V}_{IN}$ | ≤ V <sub>CC</sub>                   | -5                    |                       | 5    | μΑ |

| Device                        |                                                                 |                                                                                  |                                     |                       |                       |      |    |

|                               |                                                                 | Driver and receiver enable<br>REB=0V, DE = V <sub>CC,</sub> No load              |                                     |                       | 900                   | 1400 | μΑ |

|                               | Cumply ourrent ( :                                              | Driver enabled, receiver<br>Disabled REB=V <sub>CC</sub> , DE = V <sub>C</sub>   | <sub>C,</sub> No load               |                       | 550                   | 900  | μΑ |

| Icc                           | Supply current (quiescent)                                      | Driver disabled, receiver e                                                      |                                     |                       | 500                   | 800  | μΑ |

|                               |                                                                 | Driver and receiver disable DE = 0V, D=open, No load                             |                                     |                       |                       | 5    | μА |

| l cn                          | Thermal shutdown temperature                                    |                                                                                  |                                     |                       | 170                   |      | °C |

|                               | T <sub>SD</sub> hysteresis                                      |                                                                                  |                                     |                       | 20                    |      | 1  |

#### Note:

- 1. The absolute voltage difference between A and B cannot exceed the maximum rated value of 13V. During testing, apply A/B single terminal voltage separately.

- 2. Under any condition, ensure that  $V_{TH+}$  is at least  $V_{HYS}$  higher than  $V_{TH-}$ .

## **CS48505Ax Switching Characteristics**

All typical specs are at  $V_{CC} = 5V$ ,  $T_A = 25$ °C, Min/Max specs are over recommended operating conditions unless otherwise specified.

|                                        | Parameter                                       | Test Conditions                                    | Minimum<br>value | Typical<br>value | Maximum<br>value | Unit |

|----------------------------------------|-------------------------------------------------|----------------------------------------------------|------------------|------------------|------------------|------|

| Driver                                 |                                                 |                                                    |                  |                  |                  |      |

| t <sub>r</sub> , t <sub>f</sub>        | Driver differential output rise/fall time       | D 540 C 50 5 22 5 22 5 22 0 5                      |                  | 150              | 500              | ns   |

| t <sub>PHL</sub> ,t <sub>PLH</sub>     | Propagation delay                               | $R_L = 54 \Omega$ , $C_L = 50 pF$ , see Figure 8-5 |                  | 100              | 250              | ns   |

| t <sub>SK(P)</sub>                     | Pulse skew  t <sub>PHL</sub> – t <sub>PLH</sub> |                                                    |                  |                  | 10               | ns   |

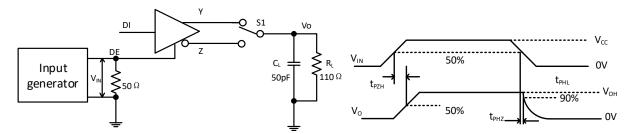

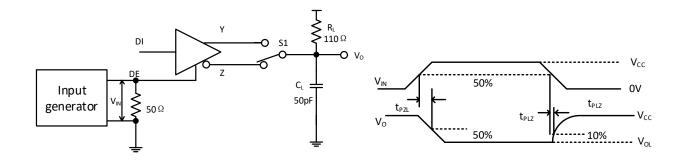

| t <sub>PHZ</sub> ,t <sub>PLZ</sub>     | Disable time                                    | See Figure 8-7, Figure 8-6                         |                  | 10               | 30               | ns   |

|                                        |                                                 | REB = 0V, See Figure 8-7, Figure 8-6               |                  | 300              | 800              | ns   |

| t <sub>PZH</sub> ,t <sub>PZL</sub> Ena | Enable time                                     | REB = V <sub>CC</sub> , See Figure 8-7, Figure 8-6 |                  | 6                | 12               | us   |

| Receiver                               |                                                 |                                                    |                  |                  |                  |      |

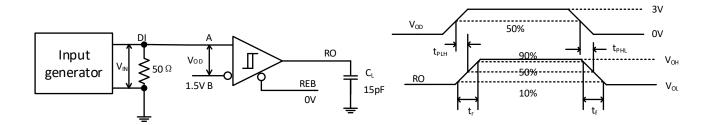

| t <sub>r</sub> , t <sub>f</sub>        | Output rise/fall time                           | C <sub>L</sub> = 15 pF, see                        |                  | 10               | 20               | ns   |

| t <sub>PHL</sub> ,t <sub>PLH</sub>     | Propagation delay                               |                                                    |                  | 50               | 100              | ns   |

| t <sub>SK(P)</sub>                     | Pulse skew  t <sub>PHL</sub> – t <sub>PLH</sub> | Figure <b>8-8</b>                                  |                  |                  | 7                | ns   |

| t <sub>PHZ</sub> , t <sub>PLZ</sub>    | Disable time                                    | see Figure 8-9                                     |                  | 30               | 60               | ns   |

| $t_{PZH(1)}$ , $t_{PZL(1)}$ ,          |                                                 | DE = V <sub>CC</sub> , see Figure 8-9, Figure 8-9  |                  | 50               | 100              | ns   |

| $t_{PZH(2)}$ , $t_{PZL(2)}$ ,          | Enable time                                     | DE = 0 V, see, Figure 8-9, Figure 8-9              |                  | 6                | 12               | μs   |

| Note:<br>1. C <sub>L</sub> in          | cludes external circuit (fixture and            | d instrumentation etc.) capacitance.               |                  |                  |                  |      |

## 7.7. CS48520Ax Switching Characteristics

All typical specs are at  $V_{CC} = 5V$ ,  $T_A = 25$ °C, Min/Max specs are over recommended operating conditions unless otherwise specified.

|                                                | Parameter                                       | Test Conditions                                    | Minimum<br>value | Typical<br>value | Maximum<br>value | Unit |

|------------------------------------------------|-------------------------------------------------|----------------------------------------------------|------------------|------------------|------------------|------|

| Driver                                         |                                                 |                                                    |                  |                  |                  |      |

| Driver differential output rise/fall time      |                                                 | D 540 C 50 75 222 5 2242 0 5                       |                  | 5                | 12               | ns   |

| t <sub>PHL</sub> ,t <sub>PLH</sub>             | Propagation delay                               | $R_L = 54 \Omega$ , $C_L = 50 pF$ , see Figure 8-5 |                  | 12               | 25               | ns   |

| t <sub>SK(P)</sub>                             | Pulse skew  t <sub>PHL</sub> - t <sub>PLH</sub> |                                                    |                  |                  | 3.5              | ns   |

| t <sub>PHZ</sub> ,t <sub>PLZ</sub>             | Disable time                                    | See Figure 8-7, Figure 8-6                         |                  | 10               | 30               | ns   |

|                                                | Enable time                                     | REB = 0V, See Figure 8-7, Figure 8-6               |                  | 300              | 800              | ns   |

| t <sub>PZH</sub> ,t <sub>PZL</sub> Enable time |                                                 | REB = V <sub>CC</sub> , See Figure 8-7, Figure 8-6 |                  | 6                | 12               | us   |

| Receiver                                       |                                                 |                                                    |                  |                  |                  |      |

| t <sub>r</sub> , t <sub>f</sub>                | Output rise/fall time                           | C <sub>L</sub> = 15 pF, see                        |                  | 4                | 8                | ns   |

| t <sub>PHL</sub> ,t <sub>PLH</sub>             | Propagation delay                               |                                                    |                  | 40               | 80               | ns   |

| t <sub>SK(P)</sub>                             | Pulse skew  t <sub>PHL</sub> - t <sub>PLH</sub> | Figure <b>8-8</b>                                  |                  |                  | 12               | ns   |

| t <sub>PHZ</sub> , t <sub>PLZ</sub>            | Disable time                                    | see Figure 8-9                                     |                  | 7                | 20               | ns   |

| t <sub>PZH(1)</sub> ,t <sub>PZL(1)</sub> ,     |                                                 | DE = V <sub>CC</sub> , see Figure 8-9 , Figure 8-9 |                  | 30               | 70               | ns   |

| $t_{PZH(2)}$ , $t_{PZL(2)}$ ,                  | Enable time                                     | DE = 0 V, see, Figure 8-9 , Figure 8-9             |                  | 6                | 12               | μs   |

| Note:                                          | ides external circuit (fixture and              | instrumentation etc.) capacitance.                 | •                |                  |                  |      |

# CHIPANALOG

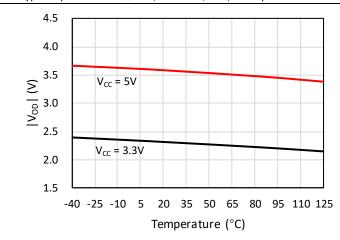

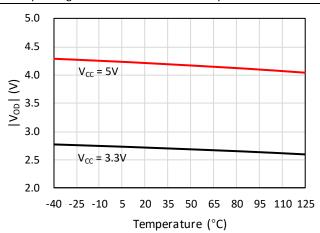

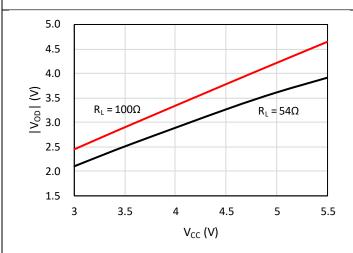

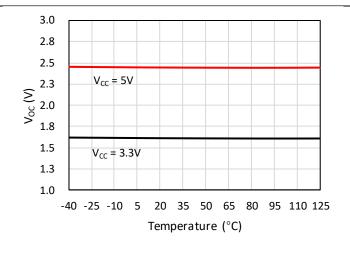

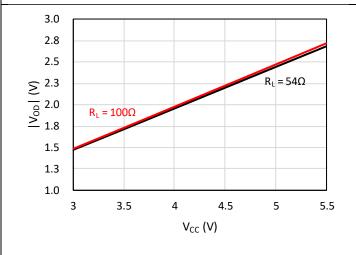

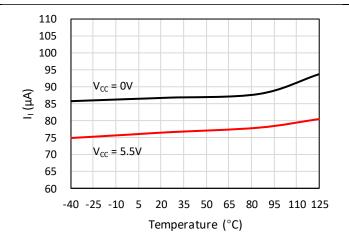

## 7.8. Typical Characteristics

All typical specs are at  $V_{CC} = 5V$ ,  $T_A = 25$ °C, Min/Max specs are over recommended operating conditions unless otherwise specified.

Figure 7-1 Driver Differential Output Voltage vs. Temperature,  $R_L = 54\Omega$

Figure 7-2 Driver Differential Output Voltage vs. Temperature,  $R_L = 100\Omega$

Figure 7-3 Driver Differential Output Voltage vs. Supply Voltage

Figure 7-4 Driver Common-mode Output Voltage vs. Temperature

Figure 7-5 Driver Common-mode Output Voltage vs. Supply Voltage

Figure 7-6 Bus Input Current vs. Temperature

## **Typical Characteristics (continued)**

Shanghai Chipanalog Microelectronics Co., Ltd.

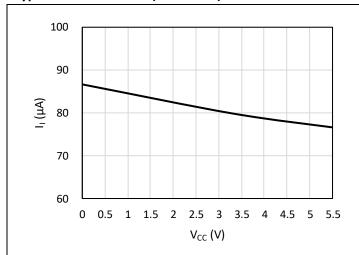

Figure 7-7 Bus Input Current vs. Supply Voltage, @ V<sub>I</sub> = 12V

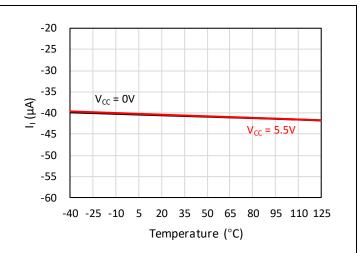

Figure 7-8 Bus Input Current vs. Temperature, @ V<sub>I</sub> = -7V

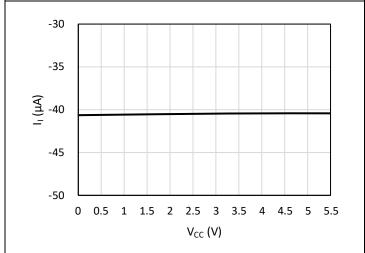

Figure 7-9 Bus Input Current vs. Supply Voltage, @ V<sub>I</sub> = -7V

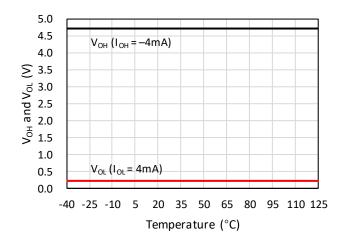

Figure 7-10 Receiver Output @ Logic-low vs. Temperature

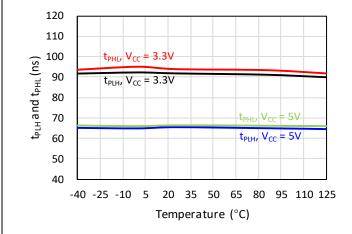

Figure 7-11 Driver Propagation Delay vs. Temperature (CS48505A)

Figure 7-12 Receiver Propagation Delay vs. Temperature (CS48505A)

## **Typical Characteristics (continued)**

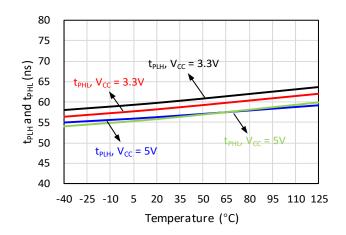

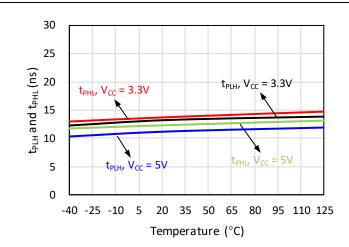

Figure 7-133 Driver Propagation Delay vs. Temperature (CS48520A)

Figure 7-14 Receiver Propagation Delay vs. Temperature (CS48520A)

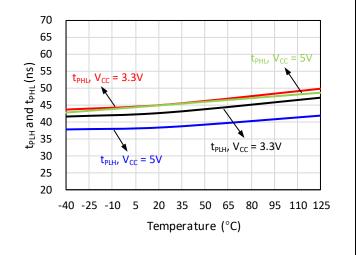

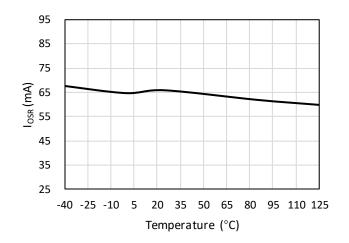

Figure 7-15 Driver Output Short Current vs. Temperature

Figure 7-16 Receiver Output Short Current vs. Temperature

## 8. Parameter Measurement Information

Shanghai Chipanalog Microelectronics Co., Ltd.

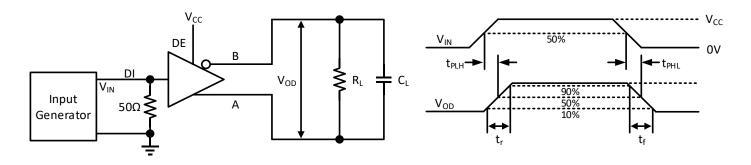

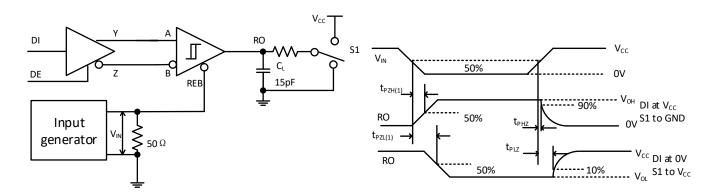

Figure 8-1. Driver Differential Output Voltage With Common-Mode Load

Figure 8-2. Driver Differential and Common-Mode Output With RS-485 Load

Figure 8-3. Receiver Output Short Current Measurement

Figure 8-4. Driver Differential Output Rise and Fall Times and Propagation Delays

Figure 8-5. Driver Enable and Disable Times with Active High Output and Pull-Down Load

Figure 8-6. Driver Enable and Disable Times with Active Low Output and Pull-up Load

Figure 8-7. Receiver Output Rise and Fall Times and Propagation Delays

Figure 8-8. Receiver Enable/Disable Times with Driver Enabled

Figure 8-9. Receiver Enable Times with Driver Disabled

#### 9. Detailed Description

#### 9.1. Overview

The CS485xxA family of devices are optimized for RS-485/RS-422 applications per the EIA/TIA-485 standard. These devices contain one differential driver and one differential receiver. The receiver features a 1/8-unit load input impedance, allowing up to 256 transceivers on a single bus. Driver Enable (DE) and Receiver Enable (REB) pins are included on these half-duplex transceivers. When disabled, the driver and receiver outputs are high impedance. In addition, the CS48505Ax features reduced slew-rate driver that minimize EMI and reduce reflections caused by improperly terminated cables, thus allowing error-free data transmission up to 500kbps. The driver slew-rate of the CS48520Ax is not limited, allowing them to transmit up to 20Mbps data rate.

To reduce system complexity and the need for external protection, the driver outputs/receiver inputs of the CS48505A/CS48520A incorporate a high ESD protection circuit capable of protecting against up to ±20kV of ESD Human Body Model (HBM) and ±6kV Contact Discharge per IEC 61000-4-2. In addition, two mechanisms against excessive power dissipation caused by faults or bus contention. The first, over-current protection on the output stage, provides immediate protection against short circuits over the entire common-mode voltage range. The second, a thermal shutdown circuit, forces the driver outputs into a high-impedance state once the junction temperature of the devices exceed the thermal shutdown threshold T<sub>SD</sub> (170°C, typ.). The shutdown condition is cleared when the junction temperature drops to 150°C.

#### 9.2. Device Functional Modes

#### 9.2.1. Driver

The CS485xxA driver accepts a single-ended, logic-level input (DI) and transfers it to a differential RS-485/RS-422 level output on the A and B driver outputs. Set the driver enable input (DE) low to disable the driver. A and B are high impedance when the driver is disabled. The DE pin has internal pull-down to GND. The DI pin has an internal pull-up resistor to  $V_{CC}$ , thus, when left open while the driver is enabled, the noninverting output A turns high and inverting output B turns low. See Table 9-1 for details.

| Input | Enable | Output |   | Function                   |

|-------|--------|--------|---|----------------------------|

| DI    | DE     | A      | В | Function                   |

| Н     | Н      | Н      | L | Drive bus high             |

| L     | Н      | L      | Н | Drive bus low              |

| Х     | L      | Z      | Z | Driver disabled            |

| Х     | OPEN   | Z      | Z | Driver disabled by default |

| OPEN  | Н      | Н      | L | Drive bus high by default  |

| Note: | •      |        |   | •                          |

Table 9-1. CS485xxA Driver Function Table

#### 9.2.2. Fail-Safe Receiver

L = Low level; H = High level; Z = high impedance; X = Don't care.

The CS485xxA receiver accepts a differential, RS-485/RS-422 level input on the A and B inputs and transfers it to a single-ended, logic-level output (RO). Drive the receiver enable input (REB) low to enable the receiver. Drive REB high to disable the receiver. RO is high impedance when REB is high. Also, REB pin has internal pull-up to  $V_{CC}$ .

The CS485xxA receiver includes a true fail-safe feature that ensures the receiver output (RO) is high when the receiver inputs are shorted or open, or when they are connected to a differentially terminated transmission line with all drivers disabled. If the differential receiver input voltage ( $V_A - V_B$ ) is greater than or equal to  $V_{TH+}$  (-50mV, maximum), RO is logic high; if the input voltage ( $V_A - V_B$ ) is less than the negative input threshold  $V_{TH-}$  (-200mV, minimum), the receiver output RO turns low. See Table 9-2 for more details.

CHIPANALOG

|  | Table 9-2. | CS485xxA | Receiver | Function | Table |

|--|------------|----------|----------|----------|-------|

|--|------------|----------|----------|----------|-------|

| Differential Input                                 | Enable | Output        | Function                     |  |  |

|----------------------------------------------------|--------|---------------|------------------------------|--|--|

| $V_{ID} = V_A - V_B$                               | REB    | RO            | Function                     |  |  |

| $V_{TH+} < V_{ID}$                                 | L      | Н             | High-level bus state         |  |  |

| $V_{TH-} < V_{ID} < V_{TH+}$                       | L      | Indeterminate | Indeterminate bus state      |  |  |

| $V_{ID} < V_{TH}$                                  | L      | L             | Low-level bus state          |  |  |

| X                                                  | Н      | Z             | Receiver disabled            |  |  |

| X                                                  | OPEN   | Z             | Receiver disabled by default |  |  |

| Open-circuit bus                                   | L      | Н             | Fail-safe high output        |  |  |

| Short-circuit bus                                  | L      | Н             | Fail-safe high output        |  |  |

| Idle (terminated) bus                              | L      | Н             | Fail-safe high output        |  |  |

| Note:                                              |        |               |                              |  |  |

| L = Low level; H = High level; Z = high impedance. |        |               |                              |  |  |

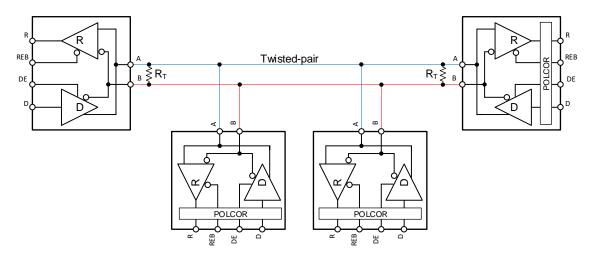

## 10. Application Information

The CS485xxA family of half-duplex RS-485/RS-422 transceivers commonly used for asynchronous data transmissions, the driver and receiver enable pins allow for the configuration of different operating modes. An RS-485/RS-422 bus consists of multiple transceivers connecting in parallel to a bus cable. As seen in the following Figure 10-1 typical network application circuit, to minimize reflections, terminate the line at both ends with a termination resistor,  $R_T$ , whose value matches the characteristic impedance( $Z_0$ ) of the cable, and keep stub lengths off the main line as short as possible. This method, known as parallel termination, generally allows for higher data rates over longer cable length.

To ensure reliable operation at all data rates and supply voltages, each supply should be decoupled with at least 100nF ceramic capacitor located as close to the supply pins as possible.

Figure 10-1. Typical RS-485 Network With CS485xxA Half-Duplex Transceivers

## 11. Package Information

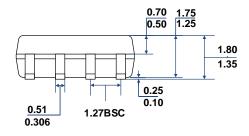

## 11.1. SOIC8 Package Outline

**TOP VIEW**

## **RECOMMENDED LAND PATTERN**

**FRONT VIEW**

**LEFT-SIDE VIEW**

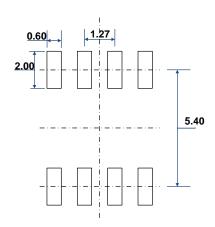

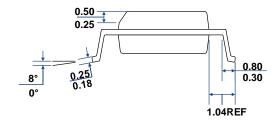

## 11.2. MSOP8 Package Outline

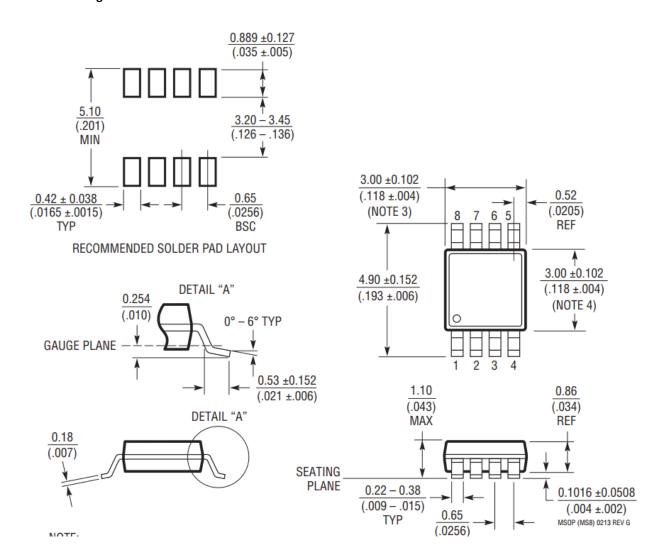

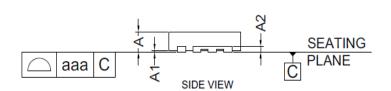

## 11.3. DFN8 Package Outline

**BOTTOM VIEW**

# COMMON DIMENSIONS (UNITS OF MEASURE=MILLIMETER)

| SYMBOL | MIN            | TYP     | MAX  |  |  |  |  |  |

|--------|----------------|---------|------|--|--|--|--|--|

| Α      | 0.70           | 0.75    | 0.80 |  |  |  |  |  |

| A1     | 0.00           | 0.02    | 0.05 |  |  |  |  |  |

| A2     |                | 0.203   |      |  |  |  |  |  |

| b      | 0.30           | 0.40    |      |  |  |  |  |  |

| D      | 2.90           | 3.00    | 3.10 |  |  |  |  |  |

| D1     | 2.51           | 2.61    |      |  |  |  |  |  |

| E      | 2.90           | 3.10    |      |  |  |  |  |  |

| E1     | 1.55           | 1,60    | 1.65 |  |  |  |  |  |

| е      |                | 0,65BSC |      |  |  |  |  |  |

| L      | 0.35 0.40 0.45 |         |      |  |  |  |  |  |

| N      | 8              |         |      |  |  |  |  |  |

| aaa    |                |         |      |  |  |  |  |  |

| bbb    | 0.10           |         |      |  |  |  |  |  |

#### NOTES:

- 1. CONTROLLING DIMENSIONS ARE IN MILLIMETERS(ANGLES IN DEGREES).

- 2. COPLANARITY APPLIES TO THE EXPOSED PAD AS THE TERMINALS.

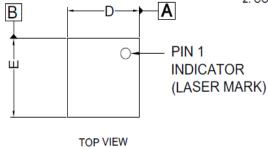

## 12. Soldering Temperature (reflow) Profile

Shanghai Chipanalog Microelectronics Co., Ltd.

Figure 12-1 Soldering Temperature (reflow) Profile

**Table12-1 Soldering Temperature Parameter**

| Profile Feature                            | Pb-Free Assembly |  |  |  |  |  |

|--------------------------------------------|------------------|--|--|--|--|--|

| Average ramp-up rate(217 °C to Peak)       | 3℃/second max    |  |  |  |  |  |

| Time of Preheat temp(from 150 °C to 200 °C | 60-120 second    |  |  |  |  |  |

| Time to be maintained above 217 ℃          | 60-150 second    |  |  |  |  |  |

| Peak temperature                           | 260 +5/-0 ℃      |  |  |  |  |  |

| Time within 5 °Cof actual peak temp        | 30 second        |  |  |  |  |  |

| Ramp-down rate                             | 6 ℃/second max.  |  |  |  |  |  |

| Time from 25°C to peak temp                | 8 minutes max    |  |  |  |  |  |

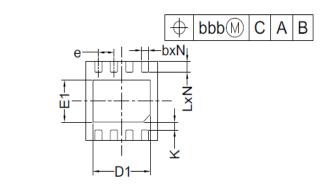

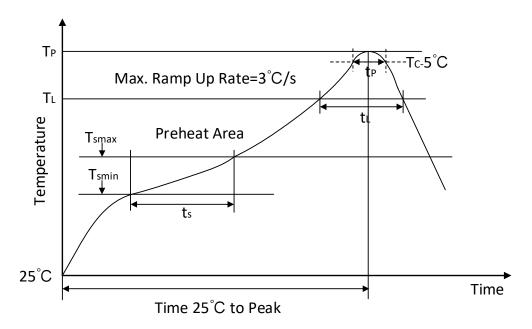

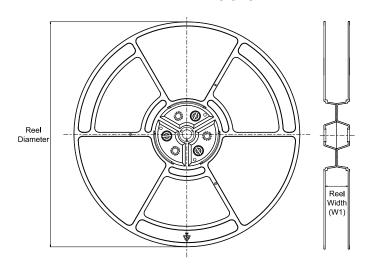

## 13. Tape and Reel Information

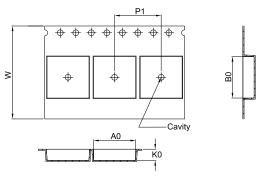

#### **REEL DIMENSIONS**

#### **TAPE DIMENSIONS**

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

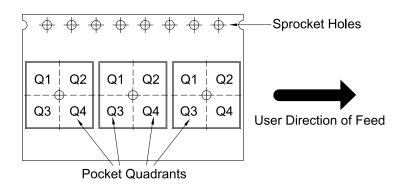

## **QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

#### \*All dimensions are nominal

| Device    | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | KO<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| CS48505AS | SOIC8           | S                  | 8    | 2500 | 330                      | 12.4                     | 6.5        | 5.4        | 2.1        | 8.0        | 12.0      | Q1               |

| CS48520AS | SOIC8           | S                  | 8    | 2500 | 330                      | 12.4                     | 6.5        | 5.4        | 2.1        | 8.0        | 12.0      | Q1               |

| CS48505AM | MSOP8           | М                  | 8    | 5000 | 330                      | 12.6                     | 6.55       | 5.4        | 1.9        | 8.0        | 12.0      | Q1               |

| CS48520AM | MSOP8           | М                  | 8    | 5000 | 330                      | 12.6                     | 6.55       | 5.4        | 1.9        | 8.0        | 12.0      | Q1               |

| CS48505AD | DFN8            | D                  | 8    | 3000 | 180                      | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q1               |

| CS48520AD | DFN8            | D                  | 8    | 3000 | 180                      | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q1               |

## 14. Important statement

The above information is for reference only and used for helping Chipanalog customers with design, research and development. Chipanalog reserves the rights to change the above information due to technological innovation without advance notice.

All Chipanalog products pass ex-factory test. As for specific practical applications, customers need to be responsible for evaluating and determining whether the products are applicable or not by themselves. Chipanalog's authorization for customers to use the resources are only limited to development of the related applications of the Chipanalog products. In addition to this, the resources cannot be copied or shown, and Chipanalog is not responsible for any claims, compensations, costs, losses, liabilities and the like arising from the use of the resources.

#### **Trademark information**

Chipanalog Inc.® and Chipanalog® are registered trademarks of Chipanalog.

http://www.chipanalog.com