# 15A Sink/Source, Single-Channel, Reinforced Isolated SiC/IGBT Gate Driver with Active Protection

- 1. Features

- 15A Peak Sink Current and 15A Peak Source Current

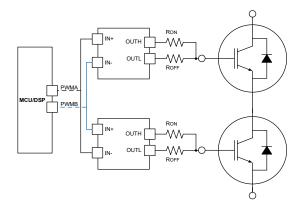

- OUTH and OUTL Split Outputs

- Drive High-power SiC MOSFET and IGBT with up to 2121 V<sub>PK</sub> Operating Voltage

- Up to 33V Output Drive Supply Range(V<sub>DD</sub>-V<sub>EE</sub>) with 12V VDD UVLO Detection and Power-Good Indication RDY

- Robust Galvanic Isolation

- High lifetime: >40 years

- Up to 5.7kV<sub>RMS</sub> isolation rating

- Common-mode transient immunity (CMTI) > ±150V/ns

- Input Features Fast Transient/Pulse Reject (< 40ns, typical)

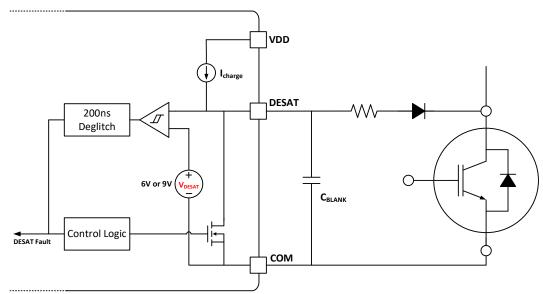

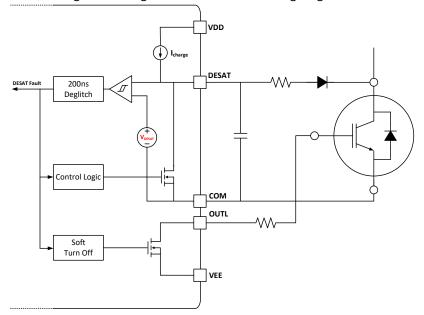

- Integrated Desaturation (DESAT) Protection with 200ns Fast-Response

- 4A Internal Active Miller Clamp

- Inputs and Outputs Features up to 5V Overshoot/Under-shoot Transient Immunity

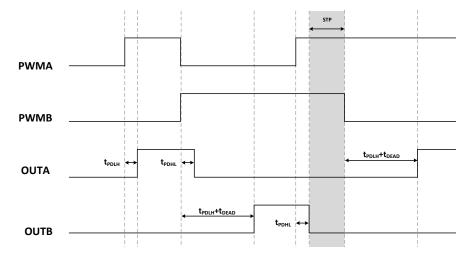

- Shoot Through Protection(CA-IS3215S\_ and CA-IS3216S\_ only)

- Fast Disable/Enable Control (RST/EN)

- Over-current Alarm FLT and Reset from RST/EN

- Propagation Delay :

- 130ns propagation delay (maximum)

- 30ns pulse skew

- 30ns part to part skew (maximum)

- 400mA (IGBT)/1A (SiC) Soft turn-off Current during Fault Occurs

- 16-pin Wide-body SOIC Package with Creepage and Clearance >8mm

- -40°C to +150°C Operating Junction Temperature (T<sub>J</sub>) Range

- Safety regulatory approvals

- VDE Reinforced isolation and Basic isolation per DIN EN IEC 60747-17 (VDE 0884-17): 2021-10

- UL certification per UL 1577 for 1 minute

- CQC certification per GB 4943.1-2022

- AEC-Q100, Grade 1

# 2. Applications

- HEV and EV Traction Inverter

- On Board Charger (OBC)

- Automotive High-voltage DC-DC Convertor

# 3. General Description

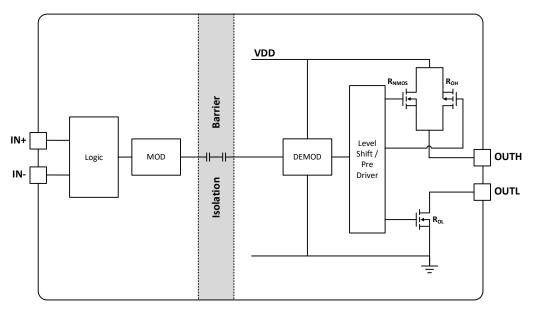

The CA-IS3215/6 devices are a family of single-channel reinforced isolated gate driver capable of sinking 15A and sourcing 15A peak-current. These devices operate with dual supplies or a single supply of up to 33V wide voltage range of  $V_{DD}$  -  $V_{EE}$ , making them ideal to drive high-power MOSFET, IGBT or silicon-carbide(SiC) transistors in various inverter, motor control or isolated power supply systems. The CA-IS3215/6 gate drivers integrate extensive active protection, such as active Miller clamp, UVLO detection on both control-side and driver-side supply, over-current and short-circuit fault alarm and protection, to optimize SiC and IGBT control and improve system reliability.

All devices have integrated digital galvanic isolation between control-side and driver-side using Chipanalog's proprietary SiO<sub>2</sub> capacitive isolation technology which features isolation for a withstand voltage rating of up to  $5.7kV_{RMS}$  for 60 seconds with minimum common-mode transient immunity (CMTI) of 150V/ns, support up to 1500V<sub>RMS</sub> isolation working voltage and 12.8kV<sub>PK</sub> surge rating.

The CA-IS3215/6 devices are available in a 16-pin widebody SOIC package with creepage and clearance > 8mm. All devices are rated for operation at junction temperatures of -40°C to +150°C. Higher operation temperature range extends gate driver designs in the industrial and automotive applications.

# Shanghai Chipanalog Microelectronics Co., Ltd.

# **Device Information**

| Part Number     | Package      | Package Size<br>(Nominal Value) |  |  |

|-----------------|--------------|---------------------------------|--|--|

| CA-IS3215xxW-Q1 | SOIC16-WB(W) | 10.3mm x 7.5mm                  |  |  |

| CA-IS3216xxW-Q1 | SOIC16-WB(W) | 10.3mm x 7.5mm                  |  |  |

#### **Simplified Schematic**

# 4. Ordering Information

#### Table 4-1. Ordering Information

| Part #          | Power Switch | DESAT     | Soft turn-off | Dead-time for Shoot | Internal/External | Package      |

|-----------------|--------------|-----------|---------------|---------------------|-------------------|--------------|

|                 |              | Threshold | Current       | Through Protection  | Clamp             |              |

| CA-IS3215NNW-Q1 | IGBT         | 9 V       | 400 mA        | N.A.                | CLAMPI            | SOIC16-WB(W) |

| CA-IS3215LNW-Q1 | IGBT         | 9 V       | 400 mA        | N.A.                | CLAMPI            | SOIC16-WB(W) |

| CA-IS3215VNW-Q1 | IGBT         | 9 V       | 400 mA        | N.A.                | CLAMPI            | SOIC16-WB(W) |

| CA-IS3215NEW-Q1 | IGBT         | 9 V       | 400 mA        | N.A.                | CLAMPE            | SOIC16-WB(W) |

| CA-IS3215SNW-Q1 | IGBT         | 9 V       | 400 mA        | 800 ns              | CLAMPI            | SOIC16-WB(W) |

| CA-IS3215SEW-Q1 | IGBT         | 9 V       | 400 mA        | 800 ns              | CLAMPE            | SOIC16-WB(W) |

| CA-IS3216NNW-Q1 | SiC          | 6 V       | 1 A           | N.A.                | CLAMPI            | SOIC16-WB(W) |

| CA-IS3216NEW-Q1 | SiC          | 6 V       | 1 A           | N.A.                | CLAMPE            | SOIC16-WB(W) |

| CA-IS3216SNW-Q1 | SiC          | 6 V       | 1 A           | 140 ns              | CLAMPI            | SOIC16-WB(W) |

| CA-IS3216SEW-Q1 | SiC          | 6 V       | 1 A           | 140 ns              | CLAMPE            | SOIC16-WB(W) |

# CA-IS3215-Q1, CA-IS3216-Q1 Datasheet V1.0

# **Table of Contents**

| 1. | Featur       | es1                                     |

|----|--------------|-----------------------------------------|

| 2. | Applic       | ations1                                 |

| 3. | Gener        | al Description1                         |

| 4. | Orderi       | ng Information2                         |

| 5. | Revisi       | on History3                             |

| 6. | Pin Co       | nfiguration and Description4            |

|    | 6.1.         | CA-IS321xNNW-Q1 and CA-IS321xSNW-Q1 Pin |

|    | Configu      | ration and Description4                 |

|    | 6.2.         | CA-IS3215LNW-Q1 Pin Configuration and   |

|    | Descript     | tion5                                   |

|    | 6.3.         | CA-IS3215LNW-Q1 Pin Configuration and   |

|    | Descript     | tion6                                   |

|    | 6.4.         | CA-IS321xNEW-Q1 and CA-IS321xSEW-Q1Pin  |

|    | -            | ration and Description7                 |

| 7. | Specif       | ications8                               |

|    | 7.1.         | Absolute Maximum Ratings <sup>1</sup> 8 |

|    | 7.2.         | ESD Ratings8                            |

|    | 7.3.         | Recommended Operating Conditions8       |

|    | 7.4.         | Thermal Information8                    |

|    | 7.5.         | Power Ratings8                          |

|    | 7.6.         | Insulation Specifications9              |

|    | 7.7.         | Safety-Related Certifications10         |

|    | 7.8.         | Safety Limits10                         |

|    | 7.9.         | Electrical Characteristics11            |

|    | 7.10.        | Switching Characteristics13             |

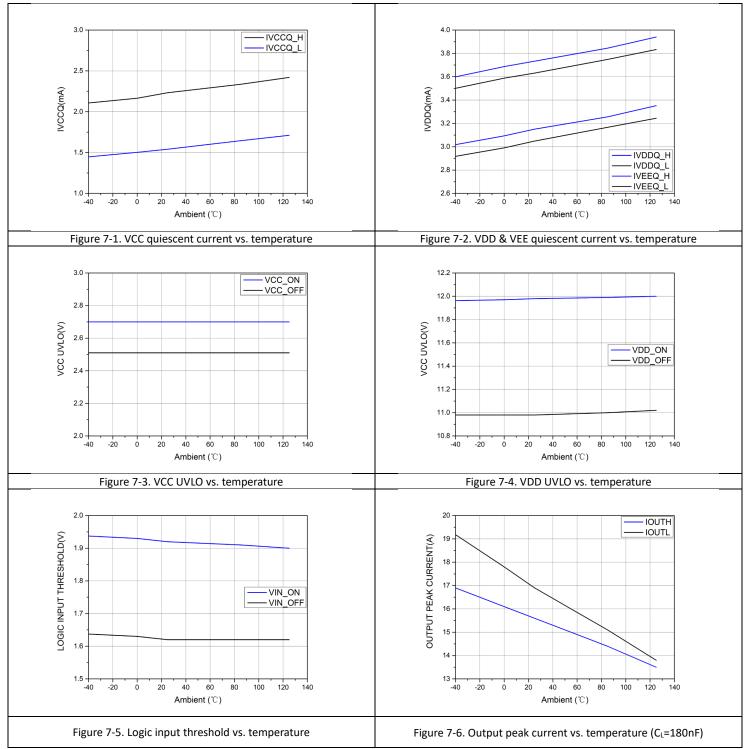

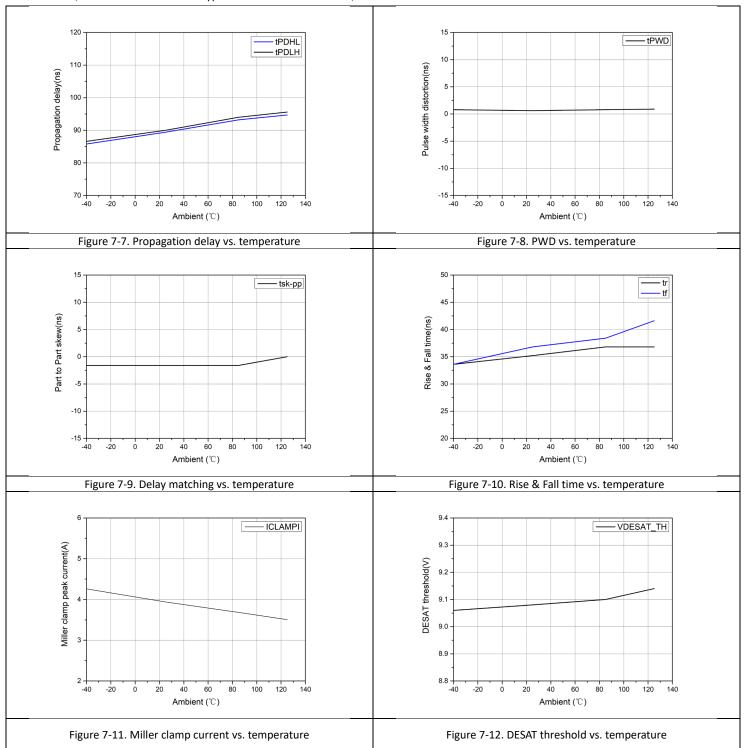

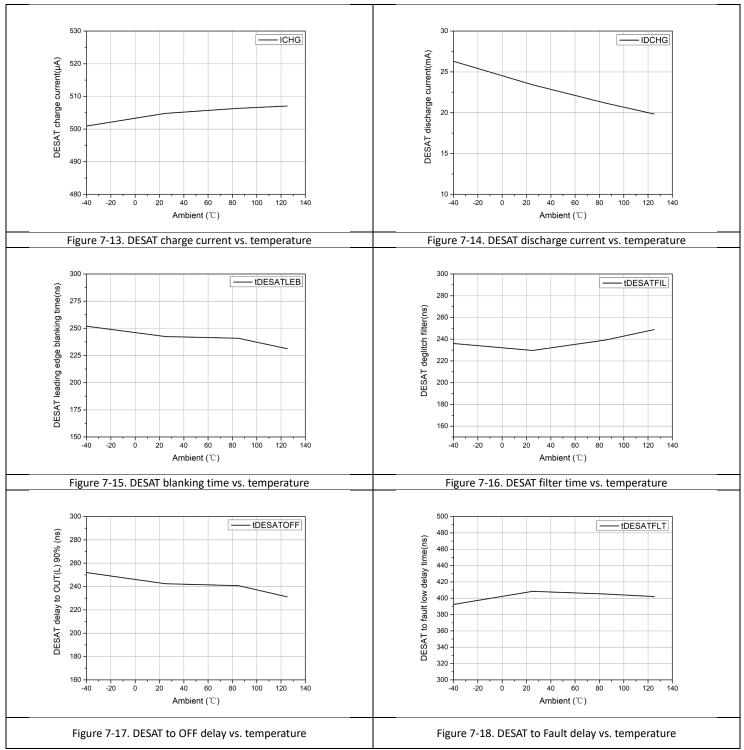

|    | 7.11.        | Typical Characteristics14               |

| 8. |              | eter Measurement Information17          |

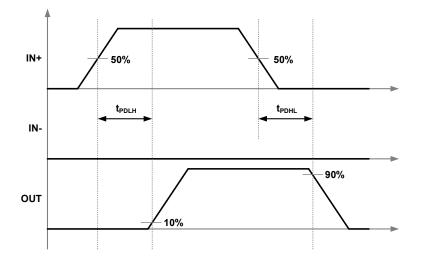

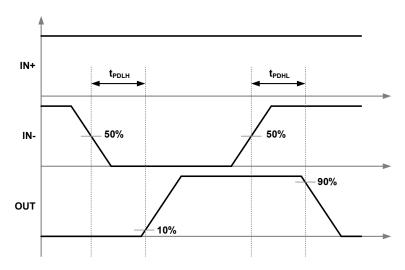

|    | 8.1.         | Propagation Delay17                     |

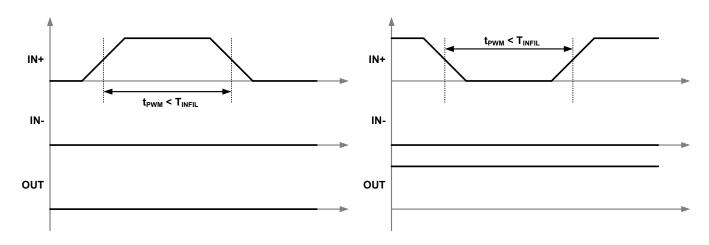

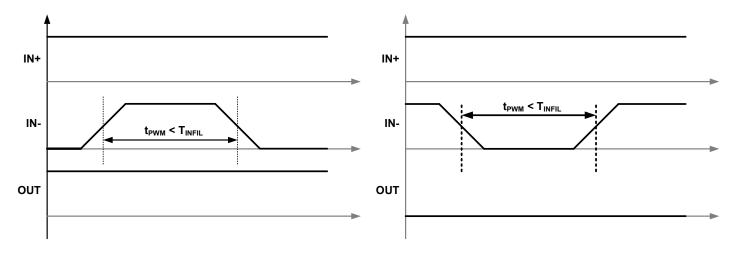

|    | 8.2.         | Input Glitch Filter                     |

|    | 8.3.         | Active Miller Clamp19                   |

|    | 8.3.         |                                         |

|    | 8.3.<br>8.4. |                                         |

|    | 8.4.<br>8.4. | Power-up UVLO Delay                     |

|    | 8.4.         |                                         |

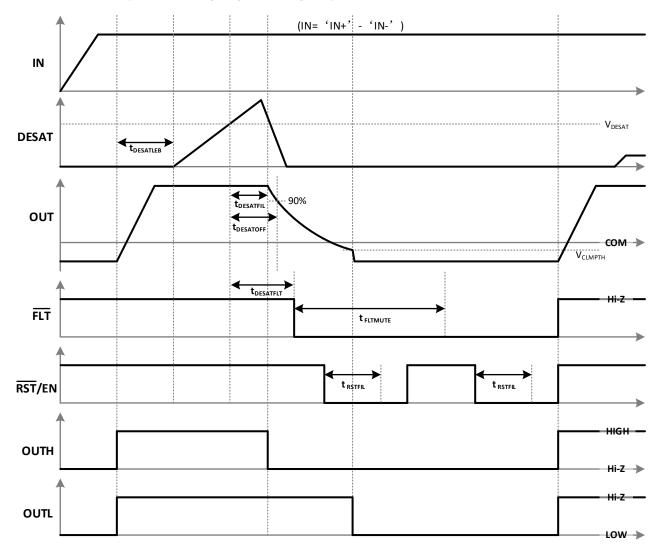

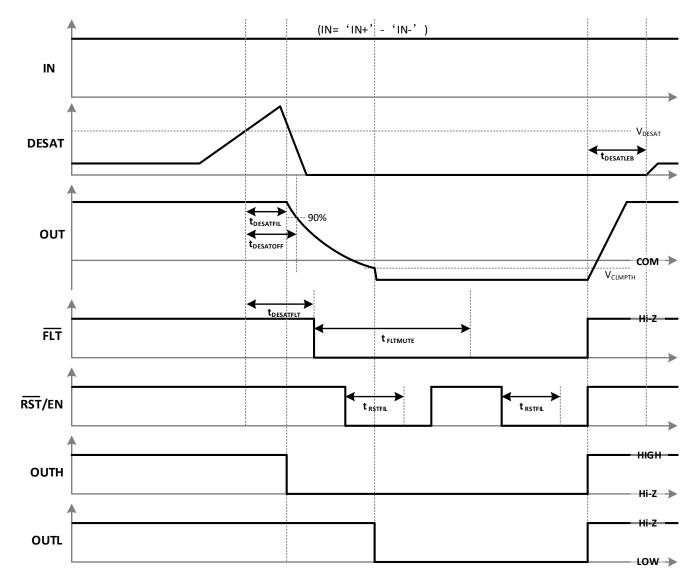

|    | 8.5.         | DESAT Protection                        |

|    | 8.5.         |                                         |

|    |              |                                         |

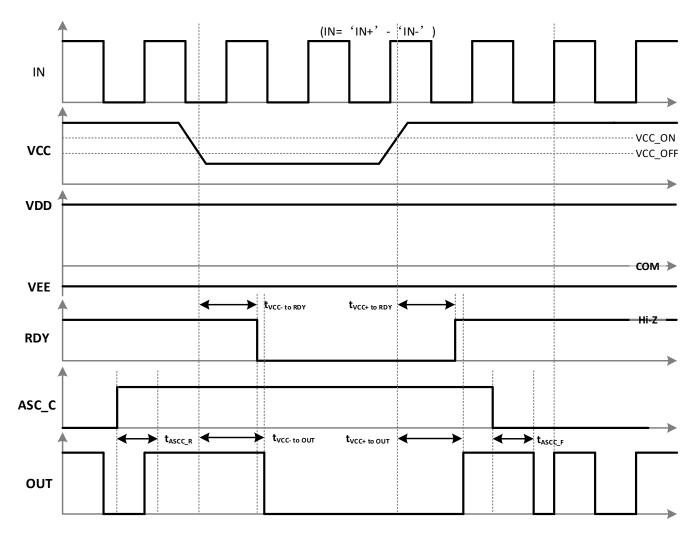

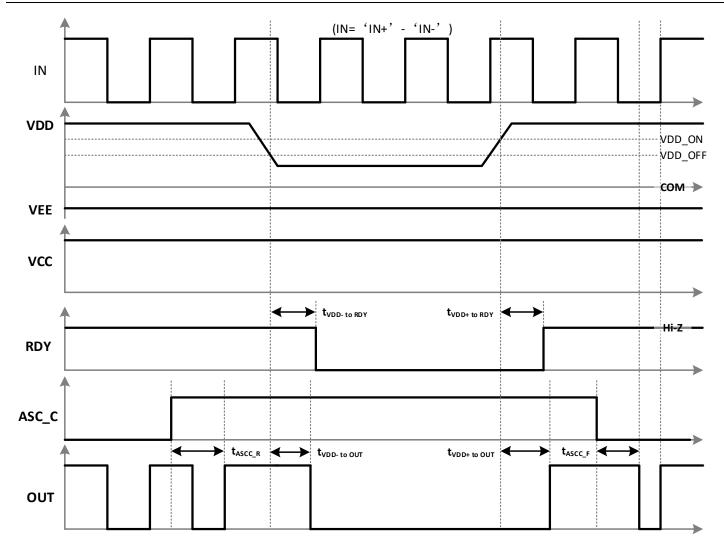

|     | 8.6.   | Activ | ve Short-circuit Protection (ASC)             | 24   |

|-----|--------|-------|-----------------------------------------------|------|

|     | 8.6    | .1.   | Active Short-circuit Protection on Control-si | ide  |

|     | ASC    | C_C   | 24                                            |      |

|     | 8.6    | .2.   | Active Short-circuit Protection on Driver-sid | e    |

|     | ASC    | C_D   | 26                                            |      |

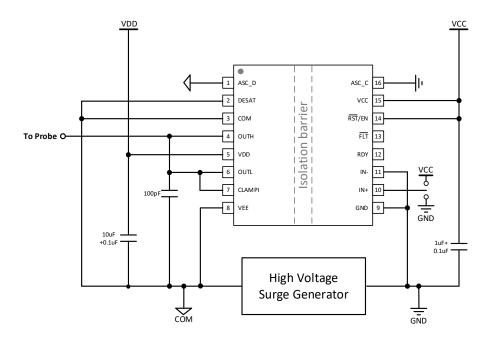

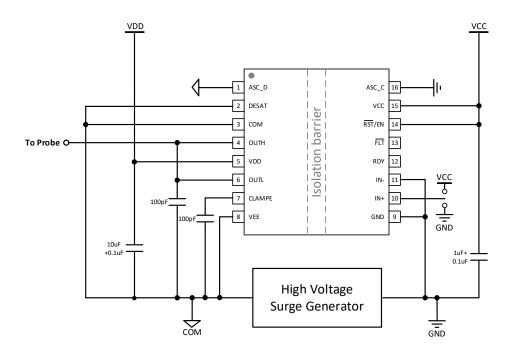

|     | 8.7.   | CMT   | 'I Test Circuit                               | 28   |

| 9.  | Detail | ed D  | escription                                    | 29   |

|     | 9.1.   | Over  | rview                                         | 29   |

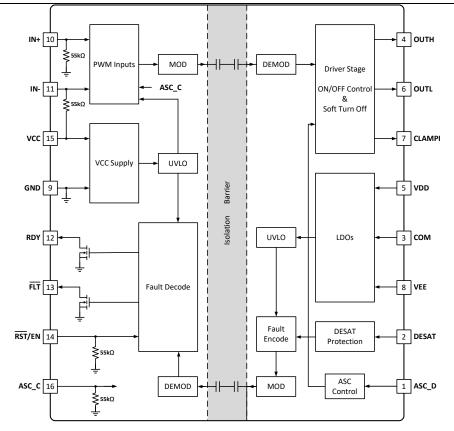

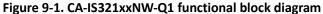

|     | 9.2.   | Fund  | ctional Block Diagram                         | 29   |

|     | 9.3.   | Inpu  | t Stage                                       | 31   |

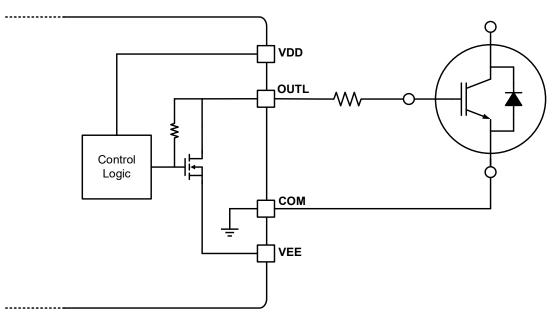

|     | 9.4.   | Driv  | er Output Stage                               | 31   |

|     | 9.5.   | Prot  | ection Functions                              | 32   |

|     | 9.5    | .1.   | VCC and VDD Undervoltage Lockout (UVLO)       | ) 32 |

|     | 9.5    | .2.   | Active Pulldown                               | 32   |

|     | 9.5    | .3.   | Short-Circuit Clamping                        | 33   |

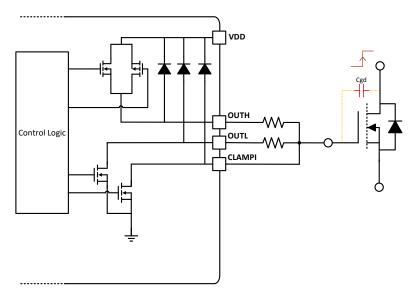

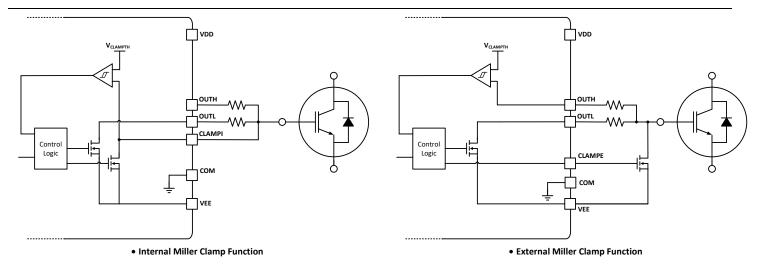

|     | 9.5    | .4.   | Active Miller Clamp                           |      |

|     | 9.5    | -     | Desaturation (DESAT) Protection               |      |

|     | 9.5    | -     | Soft turn-off                                 |      |

|     | 9.5    |       | Active Short Circuit (ASC) Protection         |      |

|     | 9.5    |       | Shoot-through Protection (STP)                |      |

|     | 9.6.   |       | t Indication and Reset (FLT, RST/EN)          |      |

|     | 9.7.   |       | ce Functional Modes                           |      |

| 10. |        |       | n and Implementation                          |      |

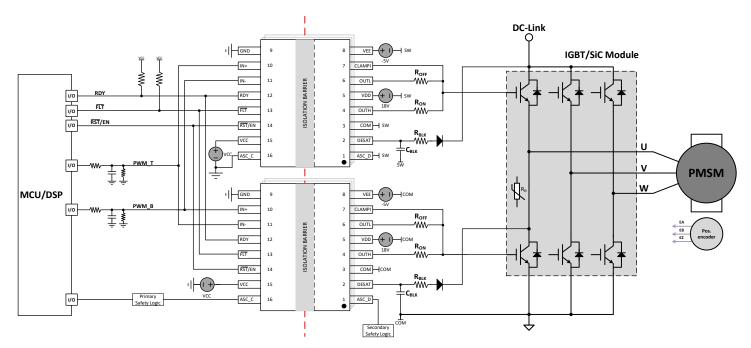

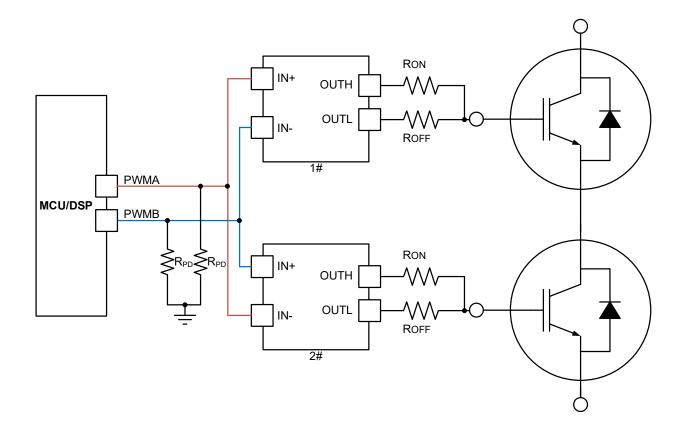

|     | 10.1.  |       | cal Application                               |      |

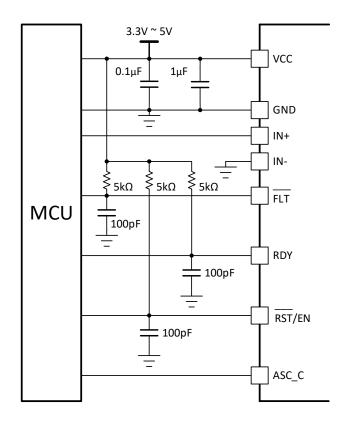

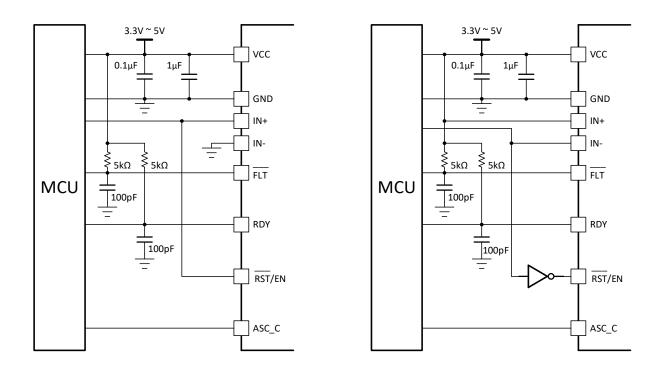

|     | 10.2.  | •     | t Filters                                     |      |

|     | 10.3.  | •     | t Filters                                     |      |

|     | 10.4.  | Inter | rlock configuration                           | 39   |

|     | 10.5.  |       | RDY pins                                      |      |

|     | 10.6.  | Auto  | o-Reset Control RST/EN                        | 41   |

|     | 10.7.  | Gate  | Priver Resisters Selection                    | 42   |

|     | 10.8.  | Over  | r-current and Short-circuit Protection        | 42   |

| 11. | PCB La | ayout | t Guidelines                                  | 43   |

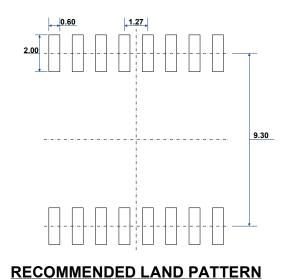

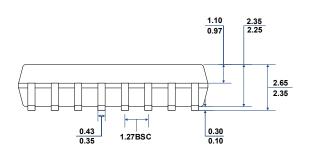

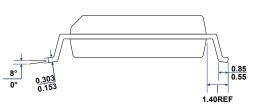

| 12. | Packa  | ge In | formation                                     | 44   |

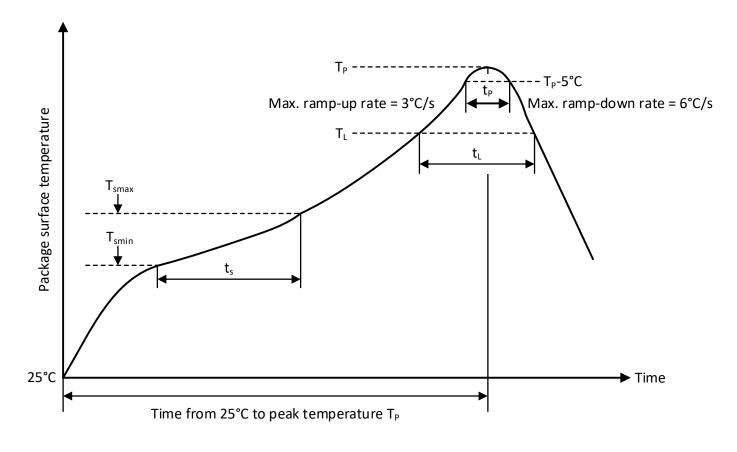

| 13. |        |       | Temperature (reflow) Profile                  |      |

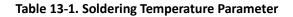

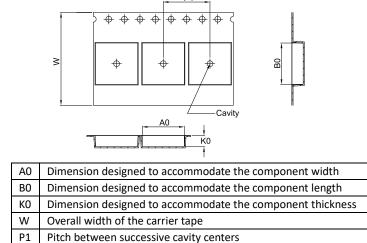

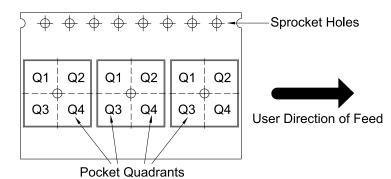

| 14. |        | -     | eel Information                               |      |

| 15. | •      |       | statement                                     |      |

|     |        |       |                                               |      |

# 5. Revision History

| Revision Number       | Description                                                 | Revised Date | Page Changed |

|-----------------------|-------------------------------------------------------------|--------------|--------------|

| Preliminary Datasheet | N/A                                                         | 2023/12/21   | N/A          |

| Datasheet V1.0        | 1. Update the certificate information of VDE $\$ UL $\$ CQC | 2024/04/16   | 1,11         |

# 6. Pin Configuration and Description

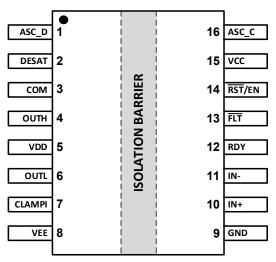

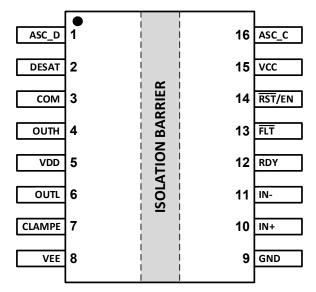

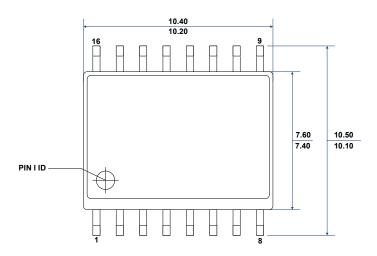

6.1. CA-IS321xNNW-Q1 and CA-IS321xSNW-Q1 Pin Configuration and Description

Figure 6-1. CA-IS321xNNW-Q1/ CA-IS321xSNW-Q1 Pin Configuration

| Pin Name | Pin Number | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|----------|------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ASC_D    | 1          | I                 | Active short circuit(ASC) control input (active high) for driver-side. Drive ASC_D high to initial the ASC protection and force the driver output to high-level during fault occurs. Connect this pin to COM if not used.                                                                                                                                                                                             |  |  |  |

| DESAT    | 2          | I                 | Desaturation protection input.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| COM      | 3          | Р                 | Gate driver common pin. Connect COM to external IGBT's emitter pin or SiC MOSFET's source pin.                                                                                                                                                                                                                                                                                                                        |  |  |  |

| OUTH     | 4          | 0                 | Positive gate drive output.                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| VDD      | 5          | Р                 | Positive power supply input for gate driver. Bypass VDD to COM with at least 10µF capacitor as close as possible to the pin VDD.                                                                                                                                                                                                                                                                                      |  |  |  |

| OUTL     | 6          | 0                 | Negative gate drive output.                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| CLAMPI   | 7          | -                 | Internal active Miller clamp input. Connect CLAMPI to the gate of the power MOSFET.                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| VEE      | 8          | Р                 | Negative power supply input for gate driver. Bypass VEE to COM with at least 10µF capacitor as close as possible to the pin VEE.                                                                                                                                                                                                                                                                                      |  |  |  |

| GND      | 9          | G                 | Ground reference for control-side.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| IN+      | 10         | -                 | on-inverting driver input on control-side. It has internal pulldown to GND.                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| IN-      | 11         | -                 | verting driver input on control-side. It has internal pullup to VCC.                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| RDY      | 12         | 0                 | ctive-high, open-drain, power-good output. RDY goes high when VCC and VDD are both above their<br>espective UVLO thresholds, indicating that the device is powered up and ready for operation.                                                                                                                                                                                                                        |  |  |  |

| FLT      | 13         | 0                 | Active-low, open-drain output fault indicator. FLT goes low to indicate that over-current or short-circuit fault occurs.                                                                                                                                                                                                                                                                                              |  |  |  |

| RST/EN   | 14         | I                 | <ul> <li>Reset and enable control input. RST/EN has internal pulldown.</li> <li>1) Enable /Shutdown control for driver-side. Put RST/EN low to turn-off the external power transistors;</li> <li>2) Resets the desaturation condition indicator output at pin FLT. Put RST/EN to low for more than 800ns, assert FLT reset at the rising edge of RST/EN and reset DESAT fault indication latch at pin FLT.</li> </ul> |  |  |  |

| VCC      | 15         | Р                 | 3.0V o 5.5V power supply input for control-side. Bypass VCC to GND with at least $1\mu$ F ceramic capacitor as close as possible to VCC pin.                                                                                                                                                                                                                                                                          |  |  |  |

| ASC_C    | 16         | Ι                 | Active short circuit (ASC) input for control-side. ASC_C has internal pulldown. If ASC_C is high, OUTH/OUTL is pulled high. If ASC_C is low, the OUTH/OUTL pins follow the IN+ and IN_ pin logical truth table, see Table 9-1. Connect ASC_C to GND if not used.                                                                                                                                                      |  |  |  |

Note:

1. P = power supply, G = GND, I = input, O = output

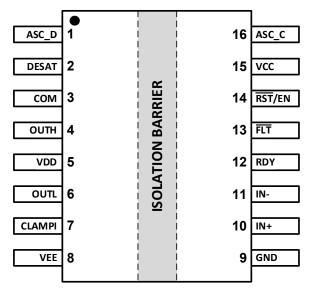

6.2.

# Shanghai Chipanalog Microelectronics Co., Ltd.

# Table 6-2. CA-IS3215LNW-Q1 Pin Description

| Pin Name | Pin Number | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|----------|------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| VEE      | 1          | Р                 | Negative power supply input for gate driver. Bypass VEE to COM with at least $10\mu$ F capacitor as close as possible to the pin VEE.                                                                                                                                                                                                                                                                                |  |  |  |  |

| DESAT    | 2          | I                 | Desaturation protection input.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| COM      | 3          | Р                 | Gate driver common pin. Connect COM to external IGBT's emitter pin or SiC MOSFET's source pin.                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| OUTH     | 4          | 0                 | ive gate drive output.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| VDD      | 5          | Р                 | ive power supply input for gate driver. Bypass VDD to COM with at least 10µF capacitor as close as ible to the pin VDD.                                                                                                                                                                                                                                                                                              |  |  |  |  |

| OUTL     | 6          | 0                 | Negative gate drive output.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| CLAMPI   | 7          | I                 | Internal active Miller clamp input. Connect CLAMPI to the gate of the power MOSFET.                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| VEE      | 8          | Р                 | Negative power supply input for gate driver. Bypass VEE to COM with at least 10µF capacitor as close as possible to the pin VEE.                                                                                                                                                                                                                                                                                     |  |  |  |  |

| GND      | 9          | G                 | Ground reference for control-side.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| IN+      | 10         | I                 | Non-inverting driver input on control-side. It has internal pulldown to GND.                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| IN–      | 11         | I                 | rting driver input on control-side. It has internal pullup to VCC.                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| RDY      | 12         | 0                 | Active-high, open-drain, power-good output. RDY goes high when VCC and VDD are both above their respective UVLO thresholds, indicating that the device is powered up and ready for operation.                                                                                                                                                                                                                        |  |  |  |  |

| FLT      | 13         | 0                 | Active-low, open-drain output fault indicator. FLT goes low to indicate that over-current or short-circuit faul occurs.                                                                                                                                                                                                                                                                                              |  |  |  |  |

| RST/EN   | 14         | I                 | <ul> <li>Reset and enable control input. RST/EN has internal pulldown.</li> <li>3) Enable /Shutdown control for driver-side. Put RST/EN low to turn-off the external power transistors;</li> <li>4) Resets the desaturation condition indicator output at pin FLT. Put RST/EN to low for more than 800ns assert FLT reset at the rising edge of RST/EN and reset DESAT fault indication latch at pin FLT.</li> </ul> |  |  |  |  |

| VCC      | 15         | Р                 | 3.0V o 5.5V power supply input for control-side. Bypass VCC to GND with at least $1\mu$ F ceramic capacitor as close as possible to VCC pin.                                                                                                                                                                                                                                                                         |  |  |  |  |

| ASC_C    | 16         | I                 | Active short circuit (ASC) input for control-side. ASC_C has internal pulldown. If ASC_C is high, OUTH/OUTL is pulled high. If ASC_C is low, the OUTH/OUTL pins follow the IN+ and IN_ pin logical truth table, see Table 9-1. Connect ASC_C to GND if not used.                                                                                                                                                     |  |  |  |  |

Shanghai Chipanalog Microelectronics Co., Ltd.

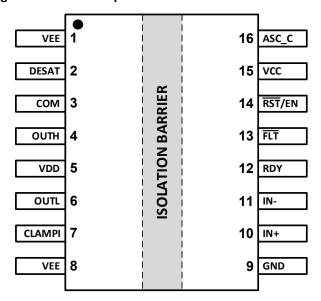

# 6.3. CA-IS3215LNW-Q1 Pin Configuration and Description

Figure 6-3. CA-IS3215LNW-Q1 Pin Configuration

#### Table 6-3. CA-IS3215LNW-Q1 Pin Description

| Pin Name | Pin Number | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|----------|------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| VEE      | 1          | Р                 | Negative power supply input for gate driver. Bypass VEE to COM with at least $10\mu$ F capacitor as close as possible to the pin VEE.                                                                                                                                                                                                                                                                                |  |  |  |

| DESAT    | 2          | I                 | Desaturation protection input.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| СОМ      | 3          | Р                 | Gate driver common pin. Connect COM to external IGBT's emitter pin or SiC MOSFET's source pin.                                                                                                                                                                                                                                                                                                                       |  |  |  |

| NC       | 4          | -                 | onnection                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| VDD      | 5          | Р                 | Positive power supply input for gate driver. Bypass VDD to COM with at least 10µF capacitor as close as possible to the pin VDD.                                                                                                                                                                                                                                                                                     |  |  |  |

| OUT      | 6          | 0                 | Gate drive output.                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| CLAMPI   | 7          | I                 | Internal active Miller clamp input. Connect CLAMPI to the gate of the power MOSFET.                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| VEE      | 8          | Р                 | Negative power supply input for gate driver. Bypass VEE to COM with at least 10µF capacitor as close as possible to the pin VEE.                                                                                                                                                                                                                                                                                     |  |  |  |

| GND      | 9          | G                 | Ground reference for control-side.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| IN+      | 10         | I                 | Non-inverting driver input on control-side. It has internal pulldown to GND.                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| IN-      | 11         | I                 | ting driver input on control-side. It has internal pullup to VCC.                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| RDY      | 12         | о                 | Active-high, open-drain, power-good output. RDY goes high when VCC and VDD are both above their respective UVLO thresholds, indicating that the device is powered up and ready for operation.                                                                                                                                                                                                                        |  |  |  |

| FLT      | 13         | 0                 | tive-low, open-drain output fault indicator. FLT goes low to indicate that over-current or short-circuit fault curs.                                                                                                                                                                                                                                                                                                 |  |  |  |

| RST/EN   | 14         | I                 | <ul> <li>Reset and enable control input. RST/EN has internal pulldown.</li> <li>5) Enable /Shutdown control for driver-side. Put RST/EN low to turn-off the external power transistors;</li> <li>6) Resets the desaturation condition indicator output at pin FLT. Put RST/EN to low for more than 800ns assert FLT reset at the rising edge of RST/EN and reset DESAT fault indication latch at pin FLT.</li> </ul> |  |  |  |

| VCC      | 15         | Р                 | 3.0V o 5.5V power supply input for control-side. Bypass VCC to GND with at least $1\mu$ F ceramic capacitor as close as possible to VCC pin.                                                                                                                                                                                                                                                                         |  |  |  |

| ASC_C    | 16         | I                 | Active short circuit (ASC) input for control-side. ASC_C has internal pulldown. If ASC_C is high, OUTH/OUTL is pulled high. If ASC_C is low, the OUTH/OUTL pins follow the IN+ and IN_ pin logical truth table, see Table 9-1. Connect ASC_C to GND if not used.                                                                                                                                                     |  |  |  |

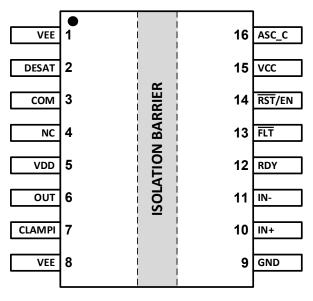

6.4. CA-IS321xNEW-Q1 and CA-IS321xSEW-Q1Pin Configuration and Description

# Figure 6-4. CA-IS321xNEW-Q1/ CA-IS321xSEW-Q1 Pin Configuration

# Table 6-4. CA-IS321xNEW-Q1/ CA-IS321xSEW-Q1 Pin Description

| Pin Name | Pin Number | Type <sup>1</sup> | Description                                                                                                                               |                                                                                                                 |    |                                                                                                                  |

|----------|------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----|------------------------------------------------------------------------------------------------------------------|

|          | 1          | 1                 | Active short circuit(ASC) control input (active high) for driver-side. Drive ASC_D high to initial the ASC function                       |                                                                                                                 |    |                                                                                                                  |

| ASC_D    | T          | I                 | and force the driver output to high-level during fault occurs. Connect this pin to COM if not used.                                       |                                                                                                                 |    |                                                                                                                  |

| DESAT    | 2          | I                 | Desaturation protection input.                                                                                                            |                                                                                                                 |    |                                                                                                                  |

| СОМ      | 3          | Р                 | Gate driver common pin. Connect COM to the IGBT's emitter pin or SiC MOSFET's source pin.                                                 |                                                                                                                 |    |                                                                                                                  |

| OUTH     | 4          | 0                 | ve gate drive output.                                                                                                                     |                                                                                                                 |    |                                                                                                                  |

|          | F          | <b>_</b>          | Positive power supply input for gate driver. Bypass VDD to COM with at least 10µF capacitor as close as                                   |                                                                                                                 |    |                                                                                                                  |

| VDD      | 5          | Р                 | possible to the pin VDD.                                                                                                                  |                                                                                                                 |    |                                                                                                                  |

| OUTL     | 6          | 0                 | Negative gate drive output.                                                                                                               |                                                                                                                 |    |                                                                                                                  |

| CLAMPE   | 7          | 0                 | External active Miller clamp input. Connect CLAMPE to the gate of the external Miller clamp MOSFET. Leave this pin float if not used.     |                                                                                                                 |    |                                                                                                                  |

| VEE      | 8          | Р                 | Negative power supply input for gate driver. Bypass VEE to COM with at least $10\mu$ F capacitor as close as possible to the pin VEE.     |                                                                                                                 |    |                                                                                                                  |

| GND      | 9          | G                 | Ground reference for control-side.                                                                                                        |                                                                                                                 |    |                                                                                                                  |

| IN+      | 10         | I                 | iverting driver input on control-side. It has internal pulldown to GND.                                                                   |                                                                                                                 |    |                                                                                                                  |

| IN-      | 11         | I                 | rting driver input on control-side. It has internal pullup to VCC.                                                                        |                                                                                                                 |    |                                                                                                                  |

| 551      | 12         | _                 | Active-high, open-drain, power-good output. RDY goes high when VCC and VDD are both above their                                           |                                                                                                                 |    |                                                                                                                  |

| RDY      |            | 12                | 12                                                                                                                                        | 12                                                                                                              | 12 | 0                                                                                                                |

| FLT      | 13         | 10                | 12                                                                                                                                        | <u> </u>                                                                                                        | 0  | Active-low, open-drain output fault indicator. FLT goes low to indicate that over-current or short-circuit fault |

| FLI      |            | 0                 | occurs.                                                                                                                                   |                                                                                                                 |    |                                                                                                                  |

|          |            |                   | Reset and enable control input. RST/EN has internal pulldown.                                                                             |                                                                                                                 |    |                                                                                                                  |

|          |            | 1                 | 1) Enable /Shutdown control for driver-side. Put RST/EN low to turn-off the external power transistors;                                   |                                                                                                                 |    |                                                                                                                  |

| RST/EN   | 14         | 1                 | 2) Resets the desaturation condition indicator output at pin FLT. Put RST/EN to low for more than 800ns,                                  |                                                                                                                 |    |                                                                                                                  |

|          |            |                   | assert $\overline{FLT}$ reset at the rising edge of $\overline{RST}$ /EN and reset DESAT fault indication latch at pin $\overline{FLT}$ . |                                                                                                                 |    |                                                                                                                  |

| NCC      | 15         | Р                 | 3.0V o 5.5V power supply input for control-side. Bypass VCC to GND with at least 1µF ceramic capacitor as                                 |                                                                                                                 |    |                                                                                                                  |

| VCC      | 15         | Р                 | close as possible to VCC pin.                                                                                                             |                                                                                                                 |    |                                                                                                                  |

|          |            |                   | Active short circuit (ASC) input for control-side. ASC_C has internal pulldown. If ASC_C is high, OUTH/OUTL is                            |                                                                                                                 |    |                                                                                                                  |

| ASC_C    | 16         | 16                | I                                                                                                                                         | pulled high. If ASC_C is low, the OUTH/OUTL pins follow the IN+ and IN_ pin logical truth table, see Table 9-1. |    |                                                                                                                  |

| —        |            | 1                 | Connect ASC_C to GND if not used.                                                                                                         |                                                                                                                 |    |                                                                                                                  |

# 7. Specifications

# 7.1. Absolute Maximum Ratings<sup>1</sup>

Over operating free-air temperature range unless otherwise specified.

|                                     | Parameters                            | Minimum | Maximum | Unit |

|-------------------------------------|---------------------------------------|---------|---------|------|

| VCC                                 | VCC–GND                               | -0.3    | 6       | V    |

| VDD                                 | VDD-COM                               | -0.3    | 36      | V    |

| VEE                                 | VEE–COM                               | -17.5   | 0.3     | V    |

| Vmax                                | VDD-VEE                               | -0.3    | 36      | V    |

| IN+, IN–, RST/EN, ASC_C             | DC                                    | GND-0.3 | VCC     | V    |

| DESAT                               | Referenced to COM                     | COM-0.3 | VDD+0.3 | V    |

| ASC_D                               | Referenced to COM                     | -0.3    | VDD+0.3 | V    |

| OUTH, OUTL, CLAMPI                  | DC                                    | VEE-0.3 | VDD     | V    |

| RDY, FLT                            |                                       | GND-0.3 | VCC     | V    |

| Γ <sub>FLT</sub> , Ι <sub>RDY</sub> | Input current for pin FLT and pin RDY |         | 20      | mA   |

| Tj                                  | Junction temperature                  | -40     | 150     | °C   |

| T <sub>stg</sub>                    | Storage temperature                   | -65     | 150     | °C   |

Notes:

1. The stresses listed under "Absolute Maximum Ratings" are stress ratings only, not for functional operation condition. Exposure to absolute maximum rating conditions for extended periods may cause permanent damage to the device.

2. Bench test result.

# 7.2. ESD Ratings

|                                                                                                        |                                                       | Value | Unit |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------|------|--|--|--|--|--|

| V <sub>FSD</sub> Electrostatic discharge                                                               | Human body model (HBM), per AEC-Q100-002 <sup>1</sup> | ±3000 | V    |  |  |  |  |  |

| V <sub>ESD</sub> Electrostatic discharge                                                               | Charged device model (CDM), per AEC-Q100-01           | ±2000 | v    |  |  |  |  |  |

| Note:                                                                                                  |                                                       |       |      |  |  |  |  |  |

| 1. AEC Q100-002 indicates that HBM stressing should comply with ANSI/ESDA/JEDEC JS-001 specifications. |                                                       |       |      |  |  |  |  |  |

# 7.3. Recommended Operating Conditions

Over operating free-air temperature range unless otherwise specified.

|                     | Parameters                | Minimum          | Maximum             | Unit                |    |

|---------------------|---------------------------|------------------|---------------------|---------------------|----|

| VCC                 | VCC–GND                   |                  | 3.0                 | 5.5                 | V  |

| VDD                 | VDD-COM                   |                  | 13                  | 33                  | V  |

| VMAX                | VDD-VEE                   |                  | -                   | 33                  | V  |

| IN+, IN–,           | Referenced to GND.        | Logic-high input | 0.7xV <sub>cc</sub> | V <sub>CC</sub>     | V  |

| RST/EN, ASC_C       | Referenced to GND.        | Logic-low input  | 0                   | 0.3×V <sub>CC</sub> | v  |

| ASC_D               | Referenced to COM.        |                  | 0                   | 5.5                 | V  |

| t <sub>RST/EN</sub> | Fault-latch reset pulse w | vidth            | 800                 |                     | ns |

| T <sub>A</sub>      | Junction temperature      |                  | -40                 | 125                 | °C |

| Tj                  | Ambient temperature       |                  | -40                 | 150                 | °C |

# 7.4. Thermal Information

|                  | Thermal Metric                         | SOIC16-WB | Unit |

|------------------|----------------------------------------|-----------|------|

| R <sub>0JA</sub> | Junction-to-ambient thermal resistance | 63.0      | °C/W |

# 7.5. Power Ratings

|          | Parameters                                 | Test Conditions                           | Typical Value | Unit |

|----------|--------------------------------------------|-------------------------------------------|---------------|------|

| PD       | Maximum input and output power dissipation | VCC=5V, VDD–COM=20V, COM–VEE=5V,          | 982.5         | mW   |

| $P_{D1}$ | Maximum input power dissipation            | IN+/IN- = 5V, 150kHz square wave with 50% | 17.5          | mW   |

| $P_{D2}$ | Maximum output power dissipation           | duty cycle, $C_L$ = 10Nf, $T_A$ =25°C     | 965           | mW   |

# 7.6. Insulation Specifications

|                   | Parameters                                          | Test Conditions                                                                                                                                                                                  | Specifications<br>W | Unit            |

|-------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|

| CLR               | External clearance                                  | Shortest terminal-to-terminal distance through air                                                                                                                                               | 8                   | mm              |

| CPG               | External creepage                                   | Shortest terminal-to-terminal distance across the package surface                                                                                                                                | 8                   | mm              |

| DTI               | Distance through the insulation                     | Minimum internal gap (internal clearance)                                                                                                                                                        | > 24                | μm              |

| CTI               | Comparative tracking index                          | DIN EN 60112 (VDE 0303-11); IEC 60112                                                                                                                                                            | > 600               | V               |

|                   | Material group                                      | According to IEC 60664-1                                                                                                                                                                         | I                   |                 |

|                   |                                                     | Rated mains voltage ≤ 300 V <sub>RMS</sub>                                                                                                                                                       | I-IV                |                 |

|                   | IEC 60664-1 over-voltage category                   | Rated mains voltage ≤ 600 V <sub>RMS</sub>                                                                                                                                                       | I-IV                |                 |

|                   |                                                     | Rated mains voltage ≤ 1000 V <sub>RMS</sub>                                                                                                                                                      | -                   |                 |

| DIN V \           | /DE V 0884-11:2021-10 <sup>1</sup>                  | •                                                                                                                                                                                                |                     |                 |

| V <sub>IORM</sub> | Maximum repetitive peak isolation voltage           | AC voltage (bipolar)                                                                                                                                                                             | 2121                | V <sub>PK</sub> |

| V <sub>IOWM</sub> | Maximum operating isolation voltage                 | AC voltage; time-dependent dielectric breakdown (TDDB) test                                                                                                                                      | 1500                | V <sub>RM</sub> |

| • 10 • 10         |                                                     | DC voltage                                                                                                                                                                                       | 2121                | VDC             |

|                   |                                                     | V <sub>TEST</sub> = V <sub>IOTM</sub> , t=60 s (qualification);                                                                                                                                  | 8000                |                 |

| V <sub>IOTM</sub> | Maximum transient isolation voltage                 | 9600                                                                                                                                                                                             | VPK                 |                 |

| V <sub>IOSM</sub> | Maximum surge isolation voltage <sup>2</sup>        | V <sub>TEST</sub> = $1.2 \times V_{IOTM}$ , t=1 s (100% product test)<br>Test method per IEC 62368-1, 1.2/50 μs waveform,<br>V <sub>TEST</sub> = $1.6 \times V_{IOSM}$                           | 8000                | VP              |

|                   |                                                     |                                                                                                                                                                                                  | ≤5                  |                 |

| q <sub>pd</sub>   | Apparent charge <sup>3</sup>                        | Method a, after environmental tests subgroup 1,<br>$V_{ini} = V_{IOTM}$ , $t_{ini} = 60s$ ;<br>$V_{pd(m)} = 1.6 \times V_{IORM}$ , $t_m = 10s$                                                   | ≤5                  | pC              |

|                   |                                                     | Method b1, at routine test (100% production test) and<br>preconditioning (sample test)<br>$V_{ini} = 1.2 \times V_{IOTM}$ , $t_{ini} = 1s$ ;<br>$V_{pd(m)} = 1.875 \times V_{IORM}$ , $t_m = 1s$ | ≤5                  | -               |

| CIO               | Barrier capacitance, input to output <sup>4</sup>   | $V_{10} = 0.4 \times \sin(2\pi ft), f = 1 \text{ MHz}$                                                                                                                                           | ~1                  | pF              |

|                   |                                                     | V <sub>IO</sub> = 500 V, T <sub>A</sub> = 25°C                                                                                                                                                   | >1012               |                 |

| R <sub>IO</sub>   | Isolation resistance , input to output <sup>4</sup> | V <sub>IO</sub> = 500 V, 100°C ≤ T <sub>A</sub> ≤ 125°C                                                                                                                                          | >1011               | Ω               |

|                   |                                                     | $V_{IO} = 500 \text{ V} \text{ at } T_{S} = 150^{\circ}\text{C}$                                                                                                                                 | >109                | 1               |

|                   | Pollution degree                                    |                                                                                                                                                                                                  | 2                   |                 |

|                   | Climatic category                                   |                                                                                                                                                                                                  | 40/125/21           |                 |

| UL 157            | 7                                                   |                                                                                                                                                                                                  | -                   |                 |

|                   | Maximum isolation voltage                           | $V_{TEST} = V_{ISO}$ , t = 60 s (certified)<br>$V_{TEST} = 1.2 \times V_{ISO}$ , t = 1 s (100% production test)                                                                                  | 5700                | V <sub>RM</sub> |

2. Devices are immersed in oil during surge characterization.

3. The characterization charge is discharging charge (pd) caused by partial discharge.

4. Capacitance and resistance are measured with all pins on field-side and logic-side tied together.

# CA-IS3215-Q1, CA-IS3216-Q1

# Datasheet V1.0

# Shanghai Chipanalog Microelectronics Co., Ltd.

# 7.7. Safety-Related Certifications

| VDE                                                                                                                                                                                                                        | UL                                                                                  | CQC                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------|

| Certified according to DIN EN IEC 60747-17<br>(VDE 0884-17):2021-10; EN IEC 60747-17:<br>2020+AC:2021                                                                                                                      | Certified according to UL 1577 Component<br>Recognition Program                     | Certified according to GB4943.1-2022 |

| Reinforced isolation(SOIC16-WB):<br>Maximum transient isolation voltage: 8000V <sub>pk</sub><br>Maximum repetitive-peak isolation voltage: 2121<br>V <sub>pk</sub><br>Maximum surge isolation voltage: 8000V <sub>pk</sub> | Protection voltage:<br>- 5700V <sub>RMS</sub> for SOIC16-WB packages                | Reinforced insulation for SOIC16-WB  |

| Certificate number: 40057278<br>CA-IS3215LNW-Q1: Pending<br>CA-IS3215VNW-Q1: Pending                                                                                                                                       | Certificate number: E511334<br>CA-IS3215LNW-Q1: Pending<br>CA-IS3215VNW-Q1: Pending | Certificate number: CQC23001406424   |

# 7.8. Safety Limits

|    | Parameters                             | Test Conditions                                      | Minimum | Typical | Maximum | Unit  |

|----|----------------------------------------|------------------------------------------------------|---------|---------|---------|-------|

|    |                                        | R <sub>θJA</sub> =68.3°C/W, VDD=15V,                 |         |         | 61      |       |

|    | Cofoty input output or cupply surrout  | VEE=–5V, T <sub>J</sub> =150°C, T <sub>A</sub> =25°C |         |         | 01      | A     |

| Is | Safety input, output or supply current | R <sub>0JA</sub> =68.3°C/W, VDD=20V,                 |         |         | 49      | mA    |

|    |                                        | VEE=–5V, TJ=150°C, TA=25°C                           |         |         | 49      |       |

| р  | Safety power dissipation               | R <sub>0JA</sub> =68.3°C/W, VDD=20V,                 |         |         | 1200    | mW    |

| Ps | Salety power dissipation               | VEE=–5V, T <sub>J</sub> =150°C, T <sub>A</sub> =25°C |         |         | 1200    | IIIVV |

| Ts | Maximum safety temperature             |                                                      |         |         | 150     | °C    |

# 7.9. Electrical Characteristics

$V_{CC}$  = 3.3V or 5V, connect a 1µF bypass capacitor between VCC and GND; VDD-COM = 20V, 18V or 15V; COM–VEE=0V, 5V, 8V or 15V; C<sub>L</sub>=100pF; -40°C < T<sub>J</sub> < +150°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.<sup>1, 2</sup>

|                              | Parameters                                          | Test Conditions                  | Minimum | Typical | Maximum | Uni |

|------------------------------|-----------------------------------------------------|----------------------------------|---------|---------|---------|-----|

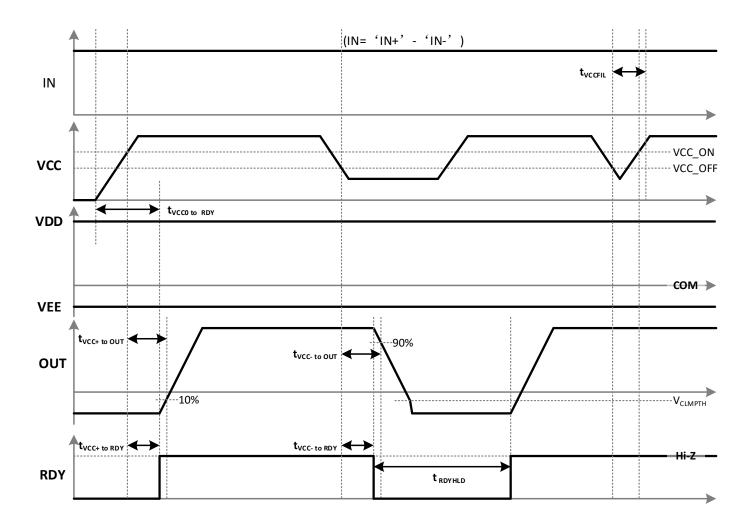

| VCC UVLO th                  | reshold and delay                                   |                                  |         |         |         |     |

| V <sub>VCC_ON</sub>          | VCC raising                                         |                                  | 2.55    | 2.7     | 2.85    |     |

| V <sub>VCC_OFF</sub>         | VCC falling                                         | VCC–GND                          | 2.35    | 2.5     | 2.65    | v   |

| V <sub>VCC_HYS</sub>         | Undervoltage-lockout threshold<br>hysteresis        |                                  |         | 0.2     |         | v   |

| t <sub>VCCFIL</sub>          | VCC UVLO detection deglitch time                    |                                  |         | 5       |         |     |

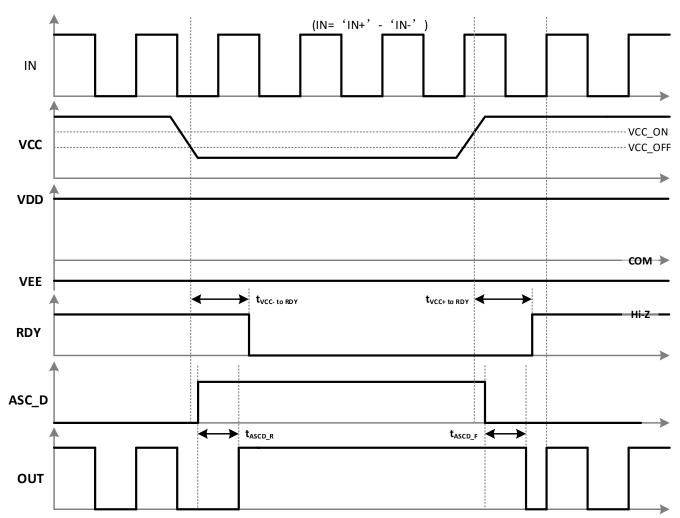

| t <sub>VCC+ to</sub> OUT     | VCC power up delay, UVLO raising to output high     |                                  |         | 30      | 70      |     |

| tvcc- to out                 | VCC power down delay, UVLO falling to output low    | IN+=VCC, IN-=GND                 |         | 7       | 15      |     |

| t <sub>VCC+ to RDY</sub>     | VCC power up delay, UVLO raising to RDY high        |                                  |         | 30      | 70      | μ   |

| t <sub>VCC- to RDY</sub>     | VCC power down delay, UVLO falling<br>to RDY low    | RST/EN=VCC                       |         | 7       | 15      |     |

| t <sub>VCC0 to RDY</sub>     | VCC power on from 0V, to RDY high                   | RST/EN=VCC, VCC power up from 0V |         | 150     |         |     |

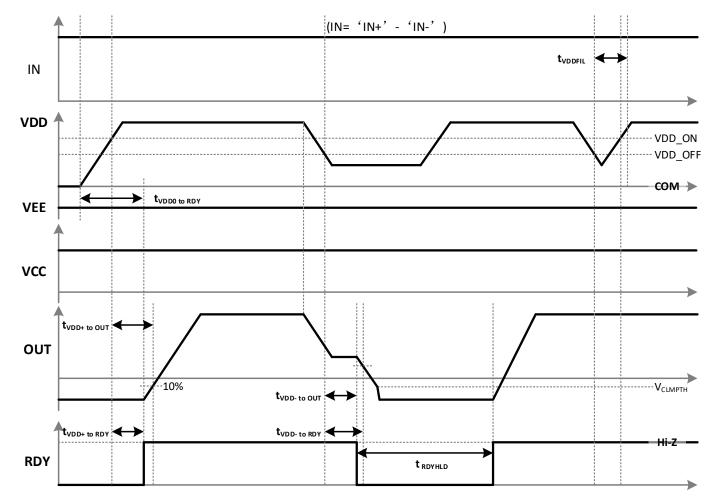

|                              | reshold and delay                                   | · · ·                            | •       |         |         |     |

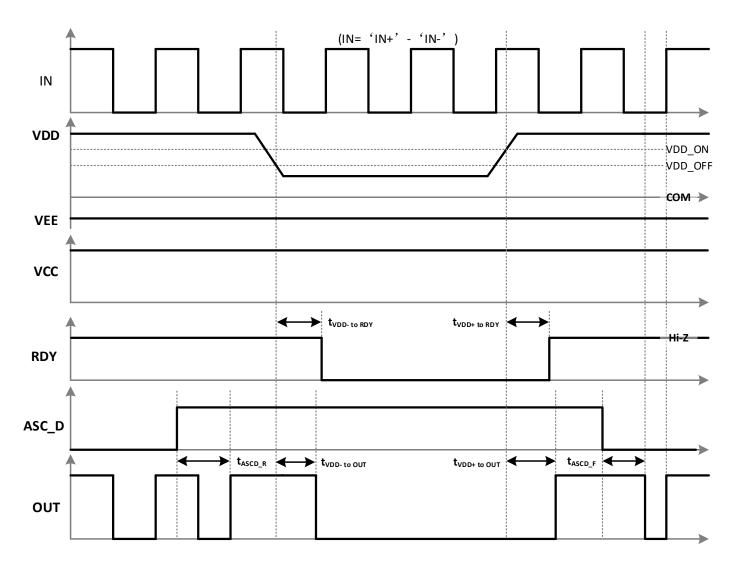

| V <sub>VDD_ON</sub>          | VDD raising                                         |                                  | 11.0    | 12.0    | 13.0    |     |

| V <sub>VDD_OFF</sub>         | VDD falling                                         |                                  | 10.0    | 11.0    | 12.0    | \   |

| $V_{\text{VDD}\_\text{HYS}}$ | Undervoltage-lockout threshold<br>hysteresis        | VDD–COM                          |         | 1.0     |         |     |

| t <sub>VDDFIL</sub>          | VDD UVLO detection deglitch time                    |                                  |         | 5       |         |     |

| t <sub>VDD+ to OUT</sub>     | VDD power up delay, UVLO raising to output high     |                                  |         | 7       | 15      |     |

| t <sub>VDD- to OUT</sub>     | VDD power down delay, UVLO<br>falling to output low | IN+=VCC, IN-=GND                 |         | 7       | 15      |     |

| t <sub>VDD+ to RDY</sub>     | VDD power up delay, UVLO raising to RDY high        |                                  |         | 7       | 15      | μ   |

| $t_{\text{VDD- to RDY}}$     | VDD power down delay, UVLO<br>falling to RDY low    | RST/EN=VCC                       |         | 7       | 15      |     |

| t <sub>VDD0 to RDY</sub>     | VDD power on from 0V to RDY high                    | VDD power up from 0V             |         | 100     |         |     |

| VCC, VDD sup                 | pply current                                        |                                  |         |         |         |     |

| Ivccq                        | V <sub>cc</sub> quiescent current                   | OUT(H)=high                      | 1.4     | 2.3     | 3.5     |     |

| ••••••                       |                                                     | OUT(L)=low                       | 0.8     | 1.5     | 2.3     | m   |

| IVDDQ                        | V <sub>DD</sub> quiescent current                   | OUT=high/low                     | 2.5     | 3.7     | 5.3     |     |

| IVEEQ                        | V <sub>EE</sub> quiescent current                   | OUT=High/Low                     | 2.1     | 3.1     | 4.7     |     |

All voltage is referenced to COM unless otherwise noted.

# CA-IS3215-Q1, CA-IS3216-Q1

# Datasheet V1.0

# Shanghai Chipanalog Microelectronics Co., Ltd.

СНІ

.0G

#### **Electrical Characteristics (continued)**

$V_{CC}$  = 3.3V or 5V, connect a 1µF bypass capacitor between VCC and GND; VDD-COM = 20V, 18V or 15V; COM–VEE=0V, 5V, 8V or 15V; C<sub>L</sub>=100pF; -40°C < T<sub>J</sub> < +150°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.<sup>1, 2</sup>

|                         | Parameters                        | Test Conditions                                               | Minimum | Typical | Maximum | Unit |

|-------------------------|-----------------------------------|---------------------------------------------------------------|---------|---------|---------|------|

| Logic input: IN+,       | IN–, RST/EN, ASC_C                |                                                               |         |         |         |      |

| V <sub>INH</sub>        | Logic-high input voltage          |                                                               |         | 1.85    | 2.31    | V    |

| V <sub>INL</sub>        | Logic-low input voltage           | VCC=3.3V                                                      | 0.99    | 1.52    |         | V    |

| VINHYS                  | Input hysteresis                  |                                                               |         | 0.33    |         | V    |

| Іін                     | Logic-high input leakage          | V <sub>IN</sub> =VCC                                          |         | 90      |         | μΑ   |

| IIL                     | Logic-low input leakage           | V <sub>IN</sub> =GND                                          |         | -90     |         | μA   |

| R <sub>IND</sub>        | Input pulldown resistance         | IN+, RST/EN, ASC_C; See Figure 9-1                            |         | 55      |         | kΩ   |

| R <sub>INU</sub>        | Input pullup resistance           | IN–, See Figure 9-1                                           |         | 55      |         | kΩ   |

|                         | IN+, IN–, RST/EN, ASC_C input     | f=50kHz, see Figure 8-3, Figure 8-4                           | 28      | 40      | 60      | ns   |

| t <sub>INFIL</sub>      | deglitch time (rising or falling) | Only for CA-IS3215SxW and CA-                                 |         | 10      |         | ns   |

|                         |                                   | IS3216SxW                                                     |         |         |         |      |

| t <sub>rstfil</sub>     | FLT filter reset time             | See Figure 8-9                                                | 400     | 550     | 800     | ns   |

| Gate driver             |                                   |                                                               |         |         |         |      |

| I <sub>OUTH</sub>       | Peak sourcing current             | $C_{VDD}$ =10 $\mu$ F, $C_{L}$ =0.18 $\mu$ F, $f_{S}$ =1kHz   | 10      | 15      |         | Α    |

| I <sub>OUTL</sub>       | Peak sink current                 | $C_{VEE}$ =10µF, C <sub>L</sub> =0.18µF, f <sub>S</sub> =1kHz | 10      | 15      |         | Α    |

| Routh                   | Pullup resistance                 | I <sub>OUT</sub> =-0.1A                                       |         | 1.6     |         | Ω    |

| Routl                   | Pulldown resistance               | I <sub>OUT</sub> =0.1A                                        |         | 0.23    |         | Ω    |

| VOUTH                   | Output high voltage               | I <sub>OUT</sub> =–0.2A, VDD=18V                              |         | 17.6    |         | V    |

| VOUTL                   | Output low voltage                | I <sub>OUT</sub> =0.2A                                        |         | 50      |         | mV   |

| Active pulldown         |                                   |                                                               |         |         |         | -    |

| VOUTPD                  | Active pulldown, OUTH, OUTL       | I <sub>OUTL</sub> =1A, VDD=OPEN, VEE=COM                      |         | 2.0     |         | V    |

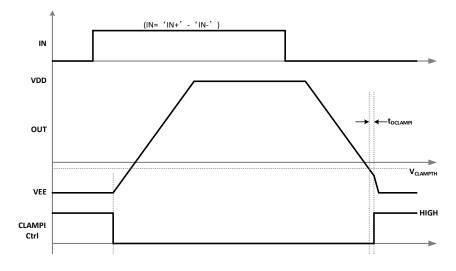

| Internal active N       | /iller clamp (CA-IS321xxNW-Q1)    |                                                               |         |         |         |      |

| VCLMPTH                 | Miller clamp threshold            | Referenced to VEE                                             | 1.5     | 2.0     | 2.5     | V    |

| V <sub>CLAMPI</sub>     | Low-level output clamp voltage    | I <sub>CLAMPI</sub> =1A                                       |         | VEE+0.4 |         | V    |

| ICLAMPI                 | Low-level output clamp current    | V <sub>CLAMPI</sub> =0V, VEE=-4V                              |         | 4       |         | Α    |

| R <sub>CLAMPI</sub>     | Miller clamp pulldown resistance  | I <sub>CLAMPI</sub> =0.2A                                     |         | 0.4     |         | Ω    |

| t <sub>DCLAMPI</sub>    | Miller clamp delay time           | C <sub>L</sub> =1.8nF, see Figure 8-5                         |         | 15      | 50      | ns   |

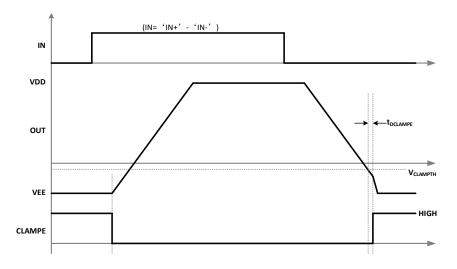

| External active N       | Viller clamp (CA-IS321xxEW-Q1)    |                                                               |         |         |         |      |

| V <sub>CLMPTH</sub>     | Miller clamp threshold            |                                                               | 1.5     | 2.0     | 2.5     | V    |

| V <sub>CLAMPE</sub>     | High-level output voltage         | Referenced to VEE                                             | 4.8     | 5.0     | 5.3     | V    |

| ICLAMPEH                | Pullup peak current               | C 10-5                                                        | 0.12    | 0.25    |         | Α    |

| ICLAMPEL                | Pulldown peak current             | C <sub>CLAMPE</sub> =10nF                                     | 0.12    | 0.25    |         | Α    |

| t <sub>clamper</sub>    | Rising time                       |                                                               |         | 20      | 40      | ns   |

| t <sub>DCLAMPE</sub>    | Miller clamp turn-on time         | C <sub>CLAMPE</sub> =330pF, see Figure 8-6                    |         | 40      | 70      | ns   |

| Short-circuit cla       | mp                                |                                                               | •       |         |         |      |

| V <sub>CLP-OUT(H)</sub> | V <sub>OUTH</sub> -VDD            | OUT=Low, I <sub>OUT(H)</sub> =500mA, t <sub>CLP</sub> =10µs   |         | 0.73    |         | V    |