## CA-IF1021Lx-Q1 Automotive LIN Transceiver with Inhibit and Wake-up

#### 1. Features

- Meets LIN2.0、LIN2.1、LIN2.2、LIN2.2A and ISO 17987-4:2016(12V) Physical-layer (EPL) Standards

- Compliant to SAE J2602-1 and SAE J2602-2 LIN Physical-layer Specification

- Designed to Support 12V Applications with Wide Operating Supply Range:

- 5.5V to 27V supply range (V<sub>BAT</sub>)

- 3.3V and 5.0V Input Logic Compatible

- System-level Power Control via INH pin

- Power-up/down Glitch-free Operation on LIN bus and RXD output

- Integrated 30kΩ LIN pull-up Resistor

- Support up to 20kbps LIN Transmission Data Rate

- Operating Mode:

- Normal operation

- Low-power sleep

- Low-power standby

- Power-on

#### Wake-up from Low-power Mode:

- Remote wake-up via LIN bus

- Local wake-up via WAKE N or SLP N pins

#### Integrated Protection Increases Robustness

- ±42V fault-tolerant LIN bus

- 42V load dump protection

- Enhanced ESD protection

- Undervoltage protection on V<sub>BAT</sub>

- Transmitter dominant timeout prevents lockup

- Thermal shutdown

- System level fail-safe protection for the unpowered node or ground disconnection

- –40°C to 150°C Junction Temperatures Range

- Available in SOIC8 and DFN8 (3.0mm x 3.0mm)

Packages

- AEC-Q100 Qualified for Automotive Application

#### 2. Applications

- Body electronics

- Automotive gateway

- Infotainment and cluster

- Hybrid electric vehicles and powertrain systems

#### 3. General Description

The CA-IF1021Lx-Q1 family of device is Local Interconnect Network (LIN) transceiver with integrated wake-up and protection features for automotive applications. LIN is low-speed universal asynchronous receiver transmitter (UART) communication protocol used to support in-vehicle networks. The CA-IF1021Lx-Q1 transceiver controls the LIN bus state via the TXD input and reports the bus state on its open-drain output RXD between the protocol controller and physical LIN networks. These device features slew-rate control and wave-shaping to reach a very low level of electromagnetic emission (EME) within a broad frequency range.

The CA-IS1021x-Q1 devices are designed to support 12V automotive applications with 5.5V to 27V wide V<sub>BAT</sub> input voltage operating range and have up to ±42V fault protection on LIN bus, with integrated ESD protection, these devices help to reduce external components in the design. Also, these devices feature low-power sleep mode, as well as wake-up capability over LIN bus, or via the WAKE\_N pin, SLP\_N pin. Inhibit output (INH) can be used to control one or more external voltage regulators presented on a node to reduce the battery power consumption at system level. In the event of a ground shift or supply voltage disconnection, the devices can prevent back-feed current through LIN to the supply input.

The CA-IF1021Lx-Q1 transceiver is available in a standard 8-pin SOIC package and 8-pin DFN package, operates over the -40°C to +150°C junction temperature range.

Table 3-1. Device Information

| Part number    | Package                             | Package size(NOM) |

|----------------|-------------------------------------|-------------------|

| CA-IF1021LS-Q1 | -IF1021LS-Q1 SOIC8(S) 4.9mm x 3.9mm |                   |

| CA-IF1021LD-Q1 | .D-Q1 DFN8(D) 3mm x 3mm             |                   |

🖈 імн RXD 🛣 RECEIVER FILTER VBAT SLEEP/ SLP\_N NORMAL CONTROL WAKE-UP TIMER WAKE\_N 🛣 LIN TXD TIME-OUT TIMER 🛣 GND TXD 🛣 SLOPE CONTROL TEMPERATURE PROTECTION

Figure 3-1. Simplified Block Diagram

## 4. Ordering Information

**Table 4-1. Ordering Information**

| Part Number    | Features                  | Package  |

|----------------|---------------------------|----------|

| CA-IF1021LS-Q1 | Automotive qualified part | SOIC8(S) |

| CA-IF1021LD-Q1 | Automotive qualified part | DFN8(D)  |

## **Table of Contents**

| 1. | Features       |                                   | 1 |

|----|----------------|-----------------------------------|---|

| 2. | Applications   |                                   | 1 |

| 3. | General Descri | ption                             | 1 |

| 4. | Ordering Infor | mation                            | 2 |

| 5. |                | ſ <b>y</b>                        |   |

| 6. |                | on and Functions                  |   |

| 7. |                |                                   |   |

|    | •              | Maximum Ratings                   |   |

|    |                | ings                              |   |

|    |                | ended Operating Conditions        |   |

|    |                | Information                       |   |

|    | 7.5. Electrica | l Characteristics                 | 6 |

|    | 7.5.1.         | DC Characteristics (Power Supply) | 6 |

|    | 7.5.2.         | Power on reset                    |   |

|    | 7.5.3.         | TXD                               | 6 |

|    | 7.5.4.         | SLP_N                             | 6 |

|    | 7.5.5.         | RXD                               |   |

|    | 7.5.6.         | WAKE_N                            |   |

|    | 7.5.7.         | INH                               |   |

|    | 7.5.8.         | LIN                               | 7 |

|    | 7.5.9.         | Thermal Shutdown                  |   |

|    | 7.5.10.        | Duty cycle                        | 7 |

|    | 7.5.11.        | Switching Characteristics         | 8 |

| 8.         | Parameter Me         | easurement Information     | 8  |

|------------|----------------------|----------------------------|----|

| 9.         | <b>Detailed Desc</b> | ription                    | 10 |

|            | 9.1. Overvie         | °W                         | 10 |

|            | 9.2. Protect         | ion Functions              | 10 |

|            | 9.2.1.               | Overvoltage Protection     | 10 |

|            | 9.2.2.               | Short-circuit Protection   | 10 |

|            | 9.2.3.               | Thermal Shutdown           | 10 |

|            | 9.2.4.               | Undervoltage Lockout       | 10 |

|            | 9.2.5.               | Fail-safe                  | 10 |

|            | 9.2.6.               | Dominant Timeout           | 11 |

|            | 9.3. Operati         | ng Mode                    | 11 |

|            | 9.3.1.               | Normal Mode                | 11 |

|            | 9.3.2.               | Sleep mode                 | 11 |

|            | 9.3.3.               | Standby mode               | 12 |

|            | 9.3.4.               | Power-on mode              | 12 |

|            | 9.4. Wake-υ          | p Events                   | 13 |

|            | 9.4.1.               | Remote Wake-up             | 13 |

|            | 9.4.2.               | Local Wake-Up              | 14 |

| <b>10.</b> | Application Ir       | formation                  | 14 |

| 11.        | Package Infor        | mation                     | 16 |

| 12.        | Soldering Ten        | nperature (reflow) Profile | 18 |

| 13.        | Tape and Ree         | Information                | 19 |

| 14.        | Important Sta        | itement                    | 20 |

|            |                      |                            |    |

## 5. Revision History

| Revision Number | Description | Page Changed |

|-----------------|-------------|--------------|

| Version 1.00    | N/A         | N/A          |

## 6. Pin Configuration and Functions

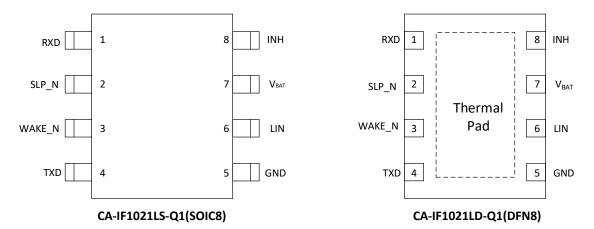

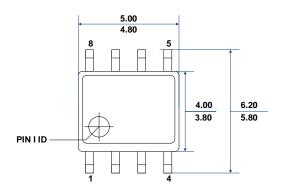

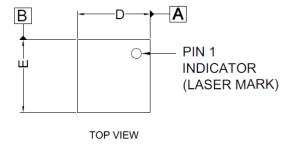

Figure 6-1. CA-IF1021Lx-Q1 Pin Configuration

Table 6-1. CA-IF1021Lx-Q1 Pin Configuration and Description

| Pin Name                                                                 | Pin #           | Туре                                                | Description                                                                                                |

|--------------------------------------------------------------------------|-----------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------|

|                                                                          |                 |                                                     | Data receive output. Open-drain output, requires an external pull-up resistor. The RXD reads               |

| RXD 1                                                                    |                 | Digital I/O                                         | back information from the LIN bus in normal operation mode and indicates a wake-up event                   |

|                                                                          |                 |                                                     | in standby mode, RXD is low if a wake event occurred.                                                      |

| SLP N                                                                    | 2               | Digital I/O                                         | Enable input with integrated pull-down resistor to GND. A logic-high on SLP_N pin puts the                 |

| JLP_IN                                                                   | 2               | Digital I/O                                         | transceiver in normal operating mode. A logic-low on SLP_N pin to select the sleep mode.                   |

| WAKE_N                                                                   | 3               | High-voltage I/O                                    | Active-low local wake-up input. Pull WAKE low to generate a local wake-up event.                           |

|                                                                          |                 |                                                     | Transmit data input. TXD is a CMOS/TTL compatible input from microcontroller with an                       |

| TXD 4                                                                    |                 |                                                     | internal pulled down resistor to GND. Set this pin to "low" to drive a dominant stat on LIN                |

|                                                                          |                 | Digital I/O                                         | bus.                                                                                                       |

|                                                                          |                 |                                                     | In standby mode, TXD indicates the wake-up source as an output. Active low after a wake-up                 |

|                                                                          |                 |                                                     | event.                                                                                                     |

| GND <sup>1</sup>                                                         | 5               | GND                                                 | Ground.                                                                                                    |

| LIN                                                                      | 6               | Bus I/O                                             | LIN bus input/output.                                                                                      |

| V                                                                        | 7               | Dawar                                               | Battery voltage input. Bypass V <sub>BAT</sub> to ground with at least 0.1µF ceramic capacitor as close as |

| V <sub>BAT</sub> 7 Power                                                 |                 | Power                                               | possible to the device.                                                                                    |

| INH                                                                      | 8               | High voltage I/O                                    | Inhibit Output. INH can be used to control one or more external voltage regulators and                     |

| INH 8 High-voltage I/O microcontroller. Active high after a wake-up even |                 | microcontroller. Active high after a wake-up event. |                                                                                                            |

| Note: The The                                                            | rmal Pad chip p | packaged in DFN8 is i                               | nternally connected to GND to enhance heat dissipation.                                                    |

## 7. Specifications

## 7.1. Absolute Maximum Ratings

| Symbol              | PARAMETER                          | TEST CONDITIONS                                                          | Min. | Max.                  | Unit                 |

|---------------------|------------------------------------|--------------------------------------------------------------------------|------|-----------------------|----------------------|

| V <sub>BAT</sub>    | Supply voltage range               |                                                                          | -0.3 | 42                    | V                    |

| V                   | TVD voltage range                  | Without I <sub>TXD</sub> current limit                                   | -0.3 | 6                     | V                    |

| $V_{TXD}$           | TXD voltage range                  | I <sub>TXD</sub> < 500μA                                                 | -0.3 | 7                     | V                    |

| V                   | DVD welters were                   | Without I <sub>RXD</sub> current limit                                   | -0.3 | 6                     | V                    |

| $V_{RXD}$           | RXD voltage range                  | I <sub>RXD</sub> < 500μA                                                 | -0.3 | 7                     | V                    |

| V <sub>SLP_N</sub>  | CLD Niveltane vana                 | Without I <sub>SLP_N</sub> current limit                                 | -0.3 | 6                     | V                    |

|                     | SLP_N voltage range                | I <sub>SLP_N</sub> < 500μA                                               | -0.3 | 7                     | V                    |

| V <sub>LIN</sub>    | LIN bus voltage range              |                                                                          | -42  | 42                    | V                    |

| V <sub>WAKE_N</sub> | WAKE_N voltage range               |                                                                          | -0.3 | 42                    | V                    |

| I <sub>WAKE_N</sub> | WAKE_N terminal current            | V <sub>WAKE_N</sub> < V <sub>GND</sub> -0.3 only; from WAKE_N to ground. | -15  |                       | mA                   |

| V <sub>INH</sub>    | INH output voltage range           |                                                                          | -0.3 | V <sub>BAT</sub> +0.3 | V                    |

| I <sub>O(INH)</sub> | INH output current                 |                                                                          | -50  | 15                    | mA                   |

| TJ                  | Virtual junction temperature range |                                                                          | -40  | 150                   | $^{\circ}\mathbb{C}$ |

| T <sub>STG</sub>    | Storage temperature range          |                                                                          | -55  | 150                   | $^{\circ}\mathbb{C}$ |

#### Note:

## 7.2. ESD Ratings

|                                              | TEST CONDITIONS                                                                               |                                                    | Value | Unit |

|----------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------|-------|------|

| HBM ESD                                      | WAKE_N, LIN, V <sub>BAT</sub> , INH pins to GND                                               |                                                    | ±8000 | V    |

| TIBIVI ESD                                   | RXD, SLP_N, TXD pins to GND                                                                   |                                                    | ±8000 | V    |

| CDM ESD                                      | Other pins to GND                                                                             |                                                    | ±2000 | V    |

| System Level ESD <sup>1</sup>                | WAKE_N, LIN and V <sub>BAT</sub> pins to GND                                                  | IEC 61000-4-2: contact discharge, without power-up | ±6000 | V    |

| Note: V <sub>BAT</sub> . GND:1nF, LIN. GND:1 | Note: V <sub>BAT</sub> . GND:1nF, LIN. GND:1nF, WAKE_ N pin series connection 30k Ω resistor. |                                                    |       |      |

## 7.3. Recommended Operating Conditions

|                  | PARAMETER                   | Min. | Max. | Unit       |

|------------------|-----------------------------|------|------|------------|

| $V_{BAT}$        | Battery voltage range       | 5.5  | 27   | V          |

| V <sub>LIN</sub> | LIN bus voltage range       | 0    | 27   | V          |

| $V_{LOGIC}$      | Logic voltage range         | 0    | 5.25 | V          |

| T <sub>A</sub>   | Operation temperature range | -40  | 125  | $^{\circ}$ |

## 7.4. Thermal Information

| Thermal Metric   |                                        | DFN8 | SOIC8 | Unit |

|------------------|----------------------------------------|------|-------|------|

| R <sub>0JA</sub> | Junction-to-ambient thermal resistance | 40   | 170   | °C/W |

<sup>1.</sup> The stresses listed under "Absolute Maximum Ratings" are stress ratings only, not for functional operation condition. Exposure to absolute maximum rating conditions for extended periods may cause permanent damage to the device.

## 7.5. Electrical Characteristics

Over recommended operating conditions,  $T_A = -40$ °C to 125°C (unless otherwise noted).

## 7.5.1. DC Characteristics (Power Supply)

|                  | PARAMETER                | TEST CONDITIONS                                                                                                                                                                  | Min. | Тур. | Max. | Unit |

|------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| I <sub>BAT</sub> | V <sub>BAT</sub> Current | Sleep mode: V <sub>LIN</sub> =V <sub>BAT</sub> V <sub>WAKE_N</sub> =V <sub>BAT</sub> V <sub>TXD</sub> =0V V <sub>SLP_N</sub> =0V V <sub>BAT</sub> =12V                           | 3    | 15   | 25   | μΑ   |

| I <sub>BAT</sub> | V <sub>BAT</sub> Current | Standby mode(recessive): V <sub>INH</sub> =V <sub>BAT</sub> V <sub>LIN</sub> =V <sub>BAT</sub> V <sub>WAKE_N</sub> =V <sub>BAT</sub> V <sub>TXD</sub> =0V V <sub>SLP_N</sub> =0V | 150  | 350  | 1000 | μΑ   |

| I <sub>BAT</sub> | V <sub>BAT</sub> Current | Standby mode(dominant): $V_{BAT} = 12V V_{INH} = 12V V_{LIN} = 0V V_{WAKE\_N} = 12V V_{TXD} = 0V V_{SLP\_N} = 0V$                                                                | 200  | 670  | 1200 | μΑ   |

| I <sub>BAT</sub> | V <sub>BAT</sub> Current | Normal mode(recessive): V <sub>INH</sub> =V <sub>BAT</sub> V <sub>LIN</sub> =V <sub>BAT</sub> V <sub>WAKE_N</sub> =V <sub>BAT</sub> V <sub>TXD</sub> =5V V <sub>SLP_N</sub> =5V  | 200  | 320  | 1200 | μΑ   |

| I <sub>BAT</sub> | V <sub>BAT</sub> Current | Normal mode (dominant): $V_{BAT} = 12V V_{INH} = 12V V_{WAKE\_N} = 12V V_{TXD} = 0V V_{SLP\_N} = 5V$                                                                             | 0.6  | 1.3  | 2    | mA   |

## 7.5.2. Power on reset

|                         | PARAMETER                                  | TEST CONDITIONS | Min. | Тур. | Max. | Unit |

|-------------------------|--------------------------------------------|-----------------|------|------|------|------|

| $V_{th(POR)L}$          | Power-on reset threshold _low level        |                 | 1.6  | 3.3  | 3.9  | V    |

| $V_{th(POR)H}$          | Power-on reset threshold _high level       |                 | 2.3  | 3.6  | 4.3  | V    |

| V <sub>hys(POR)</sub>   | Power-on reset hysteresis                  |                 | 0.05 | 0.3  | 1    | V    |

| V <sub>th(VBATL)L</sub> | V <sub>BAT</sub> low threshold _low level  |                 | 3.9  | 4.3  | 4.7  | V    |

| V <sub>th(VBATH)H</sub> | V <sub>BAT</sub> low threshold _high level |                 | 4.2  | 4.5  | 4.9  | V    |

| V <sub>hys(VBATL)</sub> | V <sub>BAT</sub> low hysteresis            |                 | 0.05 | 0.3  | 1    | V    |

## 7.5.3. TXD

|                      | PARAMETER                | TEST CONDITIONS                                                                          | Min. | Тур. | Max. | Unit |

|----------------------|--------------------------|------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>IH</sub>      | High-level input voltage |                                                                                          | 2    |      | 7    | V    |

| V <sub>IL</sub>      | Low-level input voltage  |                                                                                          | -0.3 |      | 0.8  | V    |

| V <sub>hys</sub>     | Hysteresis voltage       |                                                                                          | 50   | 200  | 400  | mV   |

| R <sub>PD(TXD)</sub> | TXD pull-down resistor   | V <sub>TXD</sub> =5V                                                                     | 140  | 500  | 1200 | kΩ   |

| I <sub>IL</sub>      | Low-level input current  | V <sub>TXD</sub> =0V                                                                     | -5   | 0    | 5    | μΑ   |

| I <sub>OL</sub>      | Low-level output current | Local wake-up; Standby mode; $V_{WAKE\_N} = 0V$ ; $V_{LIN} = V_{BAT}$ ; $V_{TXD} = 0.4V$ | 1.5  |      |      | mA   |

## 7.5.4. SLP\_N

|                        | PARAMETER                | TEST CONDITIONS        | Min. | Тур. | Max. | Unit |

|------------------------|--------------------------|------------------------|------|------|------|------|

| V <sub>IH</sub>        | High-level input voltage |                        | 2    |      | 7    | V    |

| V <sub>IL</sub>        | Low-level input voltage  |                        | -0.3 |      | 0.8  | V    |

| V <sub>hys</sub>       | Hysteresis voltage       |                        | 50   | 200  | 400  | mV   |

| R <sub>PD(SLP_N)</sub> | SLP_N pull-down resistor | V <sub>SLP_N</sub> =5V | 140  | 500  | 1200 | kΩ   |

| I <sub>IL</sub>        | Low-level input current  | V <sub>SLP_N</sub> =0V | -5   | 0    | 5    | μΑ   |

## 7.5.5. RXD

|                 | PARAMETER                  | TEST CONDITIONS                                                         | Min. | Тур. | Max. | Unit |

|-----------------|----------------------------|-------------------------------------------------------------------------|------|------|------|------|

| I <sub>OL</sub> | Low-level output current   | Normal mode: V <sub>RXD</sub> = 0.4V; V <sub>LIN</sub> = 0V             | 1.5  |      |      | mA   |

| I <sub>LH</sub> | High-level leakage current | Normal mode: V <sub>RXD</sub> = 5V; V <sub>LIN</sub> = V <sub>BAT</sub> | -5   | 0    | 5    | μΑ   |

## 7.5.6. WAKE\_N

|                    | PARAMETER                        | TEST CONDITIONS                    | Min.                | Тур. | Max.                  | Unit |

|--------------------|----------------------------------|------------------------------------|---------------------|------|-----------------------|------|

| V <sub>IH</sub>    | High-level input voltage         |                                    | V <sub>BAT</sub> -1 |      | V <sub>BAT</sub> +0.3 | V    |

| V <sub>IL</sub>    | Low-level input voltage          |                                    | -0.3                |      | V <sub>BAT</sub> -3.3 | V    |

| I <sub>pu(L)</sub> | Low-level pull-down current      | V <sub>WAKE_N</sub> = 0V           | -30                 | -12  | -1                    | μΑ   |

| I <sub>LH</sub>    | High-level input leakage current | $V_{WAKE_N} = 27V; V_{BAT} = 27V;$ | -5                  | 0    | 5                     | μΑ   |

## 7.5.7. INH

| PARAMETER                  |                                                       | TEST CONDITIONS                                  | Min. | Тур. | Max. | Unit |

|----------------------------|-------------------------------------------------------|--------------------------------------------------|------|------|------|------|

| R <sub>SW</sub>            | Switch-on resistance between V <sub>RAT</sub> and INH | Standby, normal and power on :                   |      | 20   | 50   | Ω    |

| NSW                        | Switch-off resistance between VBAT and INTI           | I <sub>INH</sub> = -15mA; V <sub>BAT</sub> = 12V |      | 20   | 30   | 7.2  |

| Ligh level leakage gurrent |                                                       | Sleep mode:                                      | E    |      | Е    | μA   |

| ILH                        | High-level leakage current                            | V <sub>INH</sub> = 27V; V <sub>BAT</sub> = 27V   | -5   | -    | 3    | μΑ   |

## 7.5.8. LIN

|                                    | PARAMETER                                  | TEST CONDITIONS                                                            | Min.                 | Тур.                 | Max.                  | Unit |

|------------------------------------|--------------------------------------------|----------------------------------------------------------------------------|----------------------|----------------------|-----------------------|------|

| I <sub>BUS_LIM</sub>               | Driver output current limitation @dominant | V <sub>TXD</sub> =0V;V <sub>LIN</sub> =V <sub>BAT</sub> =18V               | 40                   |                      | 150                   | mA   |

| R <sub>pu</sub>                    | Pull-up resistor                           | Sleep mode: V <sub>SLP_N</sub> =0V                                         | 50                   | 160                  | 250                   | kΩ   |

| I <sub>BUS_PAS_rec</sub>           | Receiver input leakage current@ recessive  | V <sub>TXD</sub> =5V;V <sub>LIN</sub> = 27V;V <sub>BAT</sub> =5.5V         |                      |                      | 20                    | μΑ   |

| I <sub>BUS_PAS_dom</sub>           | Receiver input leakage current@ dominant   | Normal mode; $V_{TXD} = 5V$ ; $V_{LIN} = 0V$ ; $V_{RAT} = 12V$             | -600                 |                      |                       | μΑ   |

| V <sub>SerDiode</sub> <sup>1</sup> | Voltage drop on the serial diode           | Pull-up path with $R_{slave}$ $I_{SerDiode} = 10 \mu A^{[1]}$              | 0.4                  | 0.7                  | 1                     | V    |

| I <sub>BUS_NO_GND</sub>            | Bus current @ loss ground                  | V <sub>BAT</sub> =27V; V <sub>LIN</sub> = 0V                               | -750                 |                      | 10                    | μΑ   |

| I <sub>BUS_NO_BAT</sub>            | Bus current @ loss battery                 | V <sub>BAT</sub> =0V; V <sub>LIN</sub> = 27V                               |                      |                      | 10                    | μΑ   |

| V <sub>BUSdom</sub>                | LIN receiver dominant state                |                                                                            |                      |                      | 0.4V <sub>BAT</sub>   | V    |

| $V_{BUSrec}$                       | LIN receiver recessive state               |                                                                            | 0.6V <sub>BAT</sub>  |                      |                       | V    |

| V <sub>BUS_CNT</sub>               | LIN receiver center threshold              | $V_{BUS\_CNT} = (V_{BUSdom} + V_{BUSrec})/2$                               | 0.44V <sub>BAT</sub> | 0. 5V <sub>BAT</sub> | 0.56V <sub>BAT</sub>  | V    |

| V <sub>HYS</sub>                   | LIN receiver hysteresis voltage            | V <sub>HYS</sub> = V <sub>BUSrec</sub> -V <sub>BUSdom</sub>                |                      |                      | 0.175V <sub>BAT</sub> | V    |

| R <sub>slave</sub>                 | Slave resistance                           | Resistance between LIN and $V_{BAT}$ ;<br>$V_{LIN} = 0V$ ; $V_{BAT} = 12V$ | 20                   | 30                   | 47                    | kΩ   |

| C <sub>LIN</sub> <sup>1</sup>      | Capacitance on LIN pin                     | [1]                                                                        |                      |                      | 30                    | pF   |

| V                                  | LINI dominant autout                       | Normal mode; V <sub>TXD</sub> = 0V; V <sub>BAT</sub> = 7V                  |                      |                      | 1.4                   | V    |

| $V_{O(DOM)}$                       | LIN dominant output                        | Normal mode; V <sub>TXD</sub> = 0V; V <sub>BAT</sub> = 18V                 |                      |                      | 2.0                   | V    |

| Note: 1.Gua                        | ranteed by design.                         |                                                                            |                      |                      |                       |      |

## 7.5.9. Thermal Shutdown

|                                    | PARAMETER                                         | TEST CONDITIONS | Min. | Тур. | Max. | Unit       |  |

|------------------------------------|---------------------------------------------------|-----------------|------|------|------|------------|--|

| T <sub>jsd(sd)</sub> <sup>1</sup>  | Thermal shutdown temperature                      |                 | 160  | 175  | 200  | $^{\circ}$ |  |

| T <sub>jsd(hys)</sub> <sup>1</sup> | Thermal shutdown temperature threshold hysteresis |                 |      | 20   |      | $^{\circ}$ |  |

| Note: 1.0                          | Note: 1.Guaranteed by design.                     |                 |      |      |      |            |  |

## **7.5.10.** Duty cycle

| PARAMETER                      | TEST CONDITIONS                                                                                                                             | Min.  | Тур. | Max.  | Unit |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| $\delta 1^{1,2}$ Duty cycle 1  | $V_{th(rec)(max)}$ =0.744x $V_{BAT}$ ; $V_{th(dom)(max)}$ =0.581x $V_{BAT}$ ; $t_{bit}$ =50 $\mu$ s; $V_{BAT}$ =7 $V^{\sim}$ 18 $V$         | 0.396 |      |       |      |

| $\delta 1^{1,2}$ Duty cycle 1  | $V_{th(rec)(max)} = 0.76xV_{BAT}$ ; $V_{th(dom)(max)} = 0.593xV_{BAT}$ ; $t_{bit} = 50\mu s$ ; $V_{BAT} = 5.5V^{\sim}7V$                    | 0.396 |      |       |      |

| δ2 <sup>2,3</sup> Duty cycle 2 | $V_{th(rec)(min)}$ =0.422x $V_{BAT}$ ; $V_{th(dom)(min)}$ =0.284x $V_{BAT}$ ; $t_{bit}$ =50 $\mu$ s; $V_{BAT}$ =7.6 $V^{\sim}$ 18 $V$       |       |      | 0.581 |      |

| 02-7- Duty cycle 2             | $V_{th(rec)(min)} = 0.41 x V_{BAT}; V_{th(dom)(min)} = 0.275 x V_{BAT}; t_{bit} = 50 \mu s; V_{BAT} = 6.1 V^{7}.6 V_{BAT}$                  |       |      | 0.581 |      |

| δ3 <sup>1,2</sup> Duty cycle 3 | $V_{th(rec)(max)}$ =0.778x $V_{BAT}$ ; $V_{th(dom)(max)}$ =0.616x $V_{BAT}$ ; $t_{bit}$ =96 $\mu$ s; $V_{BAT}$ =7 $V$ ~18 $V$               | 0.417 |      |       |      |

| δ3 <sup>1,2</sup> Duty cycle 3 | $V_{th(rec)(max)}$ =0.797x $V_{BAT}$ ; $V_{th(dom)(max)}$ =0.630x $V_{BAT}$ ; $t_{bit}$ =96 $\mu$ s; $V_{BAT}$ =5.5 $V^{\sim}7V$            | 0.417 |      |       |      |

| δ4 <sup>2,3</sup> Duty cycle 4 | $V_{th(rec)(min)}$ =0.389x $V_{BAT}$ ; $V_{th(dom)(min)}$ =0.251x $V_{BAT}$ ; $t_{bit}$ =96 $\mu$ s; $V_{BAT}$ =7.6 $V^{\sim}$ 18 $V_{BAT}$ |       |      | 0.590 |      |

| 04-75 Duty cycle 4             | $V_{th(rec)(min)} = 0.378xV_{BAT}; V_{th(dom)(min)} = 0.242xV_{BAT}; t_{bit} = 96\mu s; V_{BAT} = 6.1V^{-7.6V}$                             |       |      | 0.590 |      |

#### 7.5.11. Switching Characteristics

Over recommended operating conditions,  $5.5V \le V_{BAT} \le 27V$ ,  $T_J = -40^{\circ}C$  to  $150^{\circ}C$  (unless otherwise noted).

|                                    | PARAMETER                                                             | TEST CONDITIONS        | Min. | Тур. | Max. | Unit |

|------------------------------------|-----------------------------------------------------------------------|------------------------|------|------|------|------|

| t <sub>f</sub> <sup>2</sup>        | Fall time                                                             |                        |      |      | 22.5 | μs   |

| t <sub>r</sub> <sup>2</sup>        | Rise time                                                             |                        |      |      | 22.5 | μs   |

| $\triangle t_{(r-f)}^2$            | Difference between rise and fall time                                 | V <sub>BAT</sub> =7.3V | -5   |      | 5    | μs   |

| t <sub>P(TX)</sub> <sup>2</sup>    | TXD propagation delay                                                 | Rise and fall          |      |      | 6    | μs   |

| t <sub>P(TX)sym</sub> <sup>2</sup> | TXD propagation delay symmetry                                        |                        | -2.5 |      | 2.5  | μs   |

| t <sub>P(RX)</sub> <sup>4</sup>    | RXD propagation delay                                                 | Rise and fall          |      |      | 6    | μs   |

| t <sub>P(RX)sym</sub> <sup>4</sup> | RXD propagation delay symmetry                                        |                        | -2   |      | 2    | μs   |

| t <sub>wake(dom)LIN</sub>          | LIN dominant wake-up time(remote wake-up)                             | Sleep mode             | 30   | 80   | 150  | μs   |

| t <sub>wake(dom)WAKE_f</sub>       | Dominant wake-up time @ WAKE_N(local wake-up)                         | Sleep mode             | 7    | 30   | 50   | μs   |

| t <sub>gotonorm</sub>              | Mode change time, from sleep, power-on or standby mode to normal mode |                        | 2    | 5.5  | 10   | μs   |

| t <sub>gotosleep</sub>             | Mode change time: from normal mode to sleep mode                      |                        | 2    | 6.5  | 10   | μs   |

| t <sub>to(dom)TXD</sub>            | TXD-dominant timeout                                                  | V <sub>TXD</sub> = 0V  | 27   | 55   | 90   | ms   |

#### Notes:

1.  $\delta$ 1,  $\delta$ 3 =  $\frac{t_{bus(rec)(min)}}{2 \times t_{bit}}$

2.LIN bus load condition: (1)  $C_{BUS} = 1$ nF,  $R_{BUS} = 1$ k $\Omega$ ; (2)  $C_{BUS} = 6.8$ nF,  $R_{BUS} = 660$  $\Omega$ ; (3)  $C_{BUS} = 10$ nF,  $R_{BUS} = 500$  $\Omega$ .

3.  $\delta 2$ ,  $\delta 4 = \frac{t_{bus(rec)(max)}}{2 \times t_{bit}}$

4.Receiver output (RXD) load condition:  $C_{RXD}$  = 20pF,  $R_{RXD}$  = 2.4k $\Omega$ .

## 8. Parameter Measurement Information

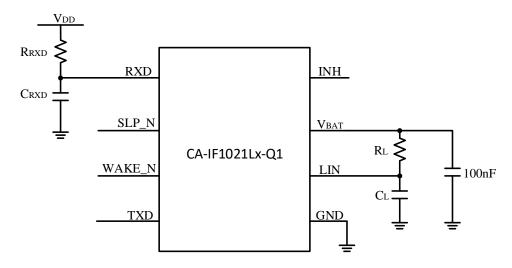

Figure 8-1. LIN Transceiver Timing Test Circuit

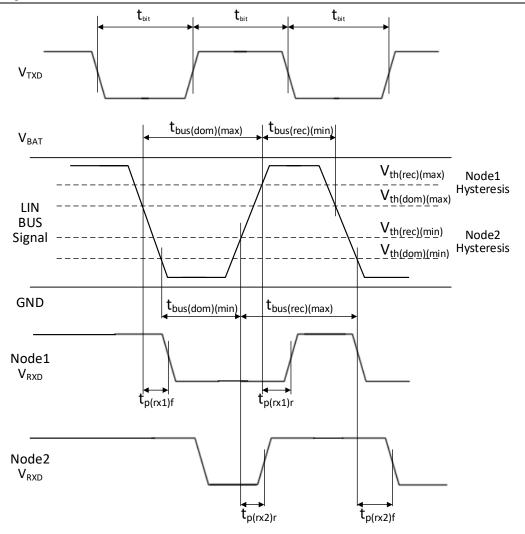

Figure 8-2. LIN Bus Transmission Timing Diagram

#### 9. Detailed Description

#### 9.1. Overview

The CA-IF1021Lx-Q1 family of devices is fault-protected Local Interconnect Network (LIN) transceiver, meets the LIN 2.x/ISO 17987-4:2016/SAE J2602 physical layer standard. These devices are designed for harsh automotive applications with a number of integrated robust protection features that improve the reliability of end equipment. The extended fault-protected voltage range of ±58V on LIN bus line and 5.5V to 27V wide input voltage operating range allow for use in +12V automotive and truck applications. Dominant timeout prevents the bus from being blocked by a hung-up microcontroller. The LIN driver output is short-circuit current-limited and protected against excessive power dissipation by thermal shutdown circuitry that disable the transmitter to protect the device.

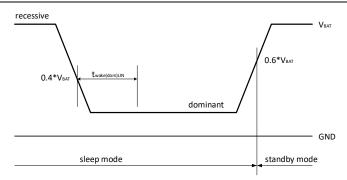

The LIN bus has two valid states: dominant and recessive. In the dominant state, LIN bus voltage level close to GND level; In the recessive state, LIN bus voltage level pulled up to the supply voltage V<sub>BAT</sub> by bus termination, see Figure 8-2 for more detail about the LIN bus specification definition. The CA-IF1021Lx-Q1 transceiver can operate up to 20kbps data rate and the LIN driver converts the transmit data streams on the TXD input to LIN bus signals with optimized slew rates in order to minimize the level of electromagnetic emission on the LIN networks. The LIN receiver output reads back the information from the LIN bus to the microcontroller.

#### 9.2. Protection Functions

## 9.2.1. Overvoltage Protection

The CA-IF1021Lx-Q1 devices have an internal ±42V overvoltage protection circuit on the driver output and receiver input to protect the devices from accidental shorts between a local power supply and the data line of the transceiver. This level of protection is present whether the transceiver is powered or un-powered.

#### 9.2.2. Short-circuit Protection

The CA-IF1021Lx-Q1 protects the transmitter output stage against a short-circuit to pin  $V_{BAT}$  or GND by limiting the driver current. However, this will cause large supply current and dissipation. Thermal shutdown further protects the devices from excessive temperatures that may result from a short circuit. The transmitter returns to normal operation once the short is removed.

#### 9.2.3. Thermal Shutdown

If the junction temperature of the CA-IF1021Lx-Q1 devices exceed the thermal shutdown threshold T<sub>jsd(sd)</sub>, the device turns off the LIN driver circuits thus blocking the TXD-to-bus transmission path, and put the LIN bus terminal to recessive state. The shutdown condition is cleared and LIN driver enabled when the junction temperature drops at least the thermal shutdown hysteresis temperature below the thermal shutdown threshold.

#### 9.2.4. Undervoltage Lockout

The CA-IF1021Lx-Q1 has undervoltage detection on  $V_{BAT}$  supply terminal, if the supply voltage  $V_{BAT}$  is less than  $V_{th(VBATL)L}$ , and greater than  $V_{th(POR)L}$ , will disable LIN driver. Once the undervoltage condition is cleared, the battery supply voltage has returned to a valid level:  $V_{BAT} > V_{th(VBATL)H}$ , the driver enabled again. During normal operation, if supply voltage drops to  $V_{BAT} < V_{th(POR)L}$ , the transceiver enters sleep mode. Once  $V_{BAT}$  increased to greater than  $V_{th(POR)H}$  from power down, the device enters power-on mode.

#### 9.2.5. Fail-safe

The CA-IF1021Lx-Q1 LIN transceivers feature fail-safe design. Both TXD and SLP\_N pins have internal pull-down resistors to GND that place the input to low-level when floating. RXD pin is floating when V<sub>BAT</sub> off. When the device is unpowered, the bus terminal and logic I/O pins have extremely low leakage currents, and there is no impact on both LIN bus and microcontroller. Also, there is no reverse current from the LIN bus in the even of supply voltage or ground disconnection. The LIN transceiver can be disconnected from the power supply without influencing the LIN bus.

#### 9.2.6. Dominant Timeout

The CA-IF1021Lx-Q1 family of devices features a transmitter-dominant timeout( $t_{to(dom)TXD}$ ) that prevents erroneous LIN controllers from clamping the bus to a dominant level by maintaining a continuous low TXD signal. When TXD remains in the dominant state (low) for greater than  $t_{to(dom)TXD}$ , the transmitter is disabled, releasing the bus to a recessive state. After a dominant timeout fault, the transmitter is re-enabled when receiving a rising edge at TXD. The transmitter-dominant timeout limits the minimum possible data rate.

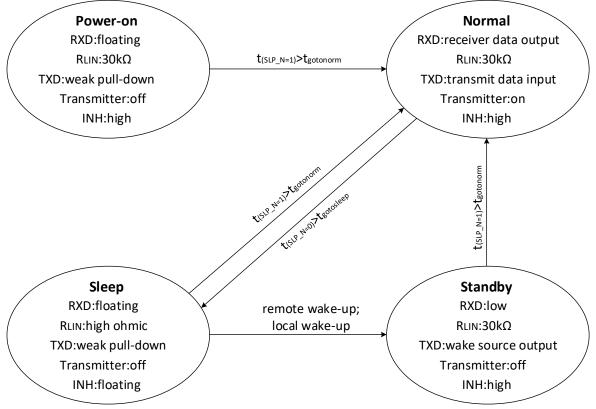

## 9.3. Operating Mode

All devices have four operating modes: power-on mode, normal operation mode, low-power standby mode and very low-power sleep mode. The operating mode is determined by an internal state machine controlled by SLP\_N and WAKE\_N, as well as several internal flags, see Table 9-1 and Figure 9-1 for more details about the CA-IF1021Lx-Q1 operating modes.

| MODE         | SLP_N | TXD                                                                      | RXD                                        | INH      | LIN Driver       | Note                                                                                                                     |

|--------------|-------|--------------------------------------------------------------------------|--------------------------------------------|----------|------------------|--------------------------------------------------------------------------------------------------------------------------|

| Sleep mode   | Low   | Weak pull-down                                                           | Floating                                   | Floating | Off              | No wake-up event detected.                                                                                               |

| Standby mode | Low   | Weak pull-down if LIN bus wake-up;<br>Strong pull-down if local wake-up. | Low                                        | High     | Off              | Detected wake-up request; TXD is wake-up source output; Waiting microcontroller to enable the transceiver via SLP_N pin. |

| Normal mode  | High  | High: recessive state  Low: dominant state                               | Recessive state: High  Dominant state: Low | High     | Normal operation | Transmission data rate is up to 20kbps.                                                                                  |

| Power-on     | Low   | Weak pull-down                                                           | Floating                                   | High     | Off              | Power-on mode after $V_{BAT}$ power up.                                                                                  |

**Table 9-1. Operating Mode**

#### 9.3.1. Normal Mode

Select the normal mode of devices operation by setting SLP\_N terminal to logic-high. The LIN driver and receiver are fully operational and LIN communication is bi-directional. Drive TXD to transmit data on the LIN bus line, the LIN bus state is presented on RXD. INH is logic-high during normal operation, can be used to enable external voltage regulators and microcontroller.

The driver translates a logic input on TXD to LIN bus output. The receiver translates the LIN bus signal to a single-ended logic output on RXD. By setting the TXD input of the CA-IF1021Lx-Q1 to logic low, the transceiver generates a dominant level on the LIN bus (LIN pin); the RXD output reads the signal on the corresponding LIN bus and indicates the dominant LIN bus signal with a logic-low signal to the microcontroller. Setting the TXD pin to logic-high, the CA-IF1021Lx-Q1 driver sets the LIN interface pin LIN to the recessive level; at the same time a logic-high signal on the RXD output indicates the recessive level on the LIN bus.

During normal operation, the CA-IF1021Lx-Q1 switches to sleep mode in case of a low-level on pin SLP\_N and maintained at least t<sub>gotosleep</sub>. The normal operation mode can be entered from all modes of operation by setting the SLP\_N input to high-level and maintained at least t<sub>gotonorm</sub>.

#### 9.3.2. Sleep mode

Sleep mode is the lowest-power operating mode. In sleep mode, the LIN transmitter and receiver are disabled, while the transceiver is still able to wake-up by a message on the LIN bus or local wake-up events through WAKE\_N pin or SLP\_N pin. The LIN Bus, WAKE\_N pin and SLP\_N pin are continuously monitored for a valid bus wake-up signal in sleep mode. To improve the system operation reliability and prevent false wake-up, the CA-IF1021Lx-Q1 features filtered LIN bus status wake-up detection and WAKE\_N, SLP\_N wake-up signal detections. This means, for a valid wake-up events to be considered, the LIN bus or WAKE\_N, or pin SLP\_N inputs must be kept in that state for more than the respective blocking time.

If the SLP\_N input pin remains low, whenever a local or remote wake-up occurs, the transceiver will enter the standby mode automatically; Drive SLP\_N input pin to high-level and maintained at least  $t_{gotonorm}$ , the transceiver will enter to normal operation directly. The CA-IF1021Lx-Q1 enters sleep mode if SLP\_N is pulled to low-level and maintained at least  $t_{gotosleep}$  when the transceiver is in normal operation mode. Also, when  $V_{BAT}$  drops below the power-on-reset threshold  $V_{th(POR)L}$ , the CA-IF1021Lx-Q1 enters sleep mode. In sleep mode, INH becomes floating; The internal slave termination between pins LIN and  $V_{BAT}$  is disabled to minimize the power dissipation, only a weak pull-up between pins LIN and  $V_{BAT}$  is present.

#### 9.3.3. Standby mode

Standby mode is low-power operating mode. The LIN transmitter and receiver are disabled and no communication with the LIN bus is possible in standby mode. TXD input is inactive and this pin indicates wake-up source as an output: weak pull-down for a remote wake-up request and strong pull-down for a local wake-up request; RXD is placed at low-level that can be used as an interrupt for the microcontroller. INH output is switched on and remains logic-high to enable external voltage regulators and microcontroller.

Standby mode is entered automatically whenever a local or remote wake-up occurs while the CA-IF1021Lx-Q1 transceiver is in sleep mode and the SLP\_N input pin remains low. This also enable the slave termination resistor at the pin LIN. In standby mode, pulling pin SLP N to logic high results in the following events immediately:

- · Reset TXD wake-up source flag and release the strong pull-down at pin TXD before the mode changed;

- · Reset the wake-up request signal on pin RXD;

- · Enter to normal operation mode if the high-level on SLP\_N pin has been maintained for at least tgotonorm.

#### 9.3.4. Power-on mode

When  $V_{BAT}$  exceeds the power-on-reset threshold voltage  $V_{th(POR)H}$  from power-down, the CA-IF1021Lx-Q1 transceiver enters power-on mode. Though the CA-IF1021Lx-Q1 is powered-up and INH is high, both LIN transmitter and receiver are still inactive. The RXD output is floating, TXD is at weak pull-down. INH is logic-high, can be used to enable external voltage regulators. The normal operation mode can be entered by setting the SLP\_N input pin to high-level for  $t_{gotonorm}$ .

Figure 9-1. State Diagram

#### 9.4. Wake-up Events

Advanced power management and wake-up capability make the CA-IF1021Lx-Q1 ideal for automotive electronic control unit (ECU) modules or other battery power applications that are permanently supplied by battery. For CA-IF1021Lx-Q1 devices, there are two different ways to exit sleep mode:

#### • Remote wake-up:

The transceiver wake-up via a valid dominant signal on the LIN bus for at least the time twake(dom)LIN.

#### • Local wake-up:

The operation mode changed by setting the SLP\_N input high at least the time t<sub>gotonorm</sub>, or The transceiver waked-up by setting the WAKE\_N low for at least t<sub>wake(dom)WAKE\_N</sub>.

The TXD output is used to indicate wake-up source while the device is in standby mode: weak pull-down for a remote wake-up request and strong pull-down for a local wake-up request; RXD is placed at low-level that can be used as an interrupt for the microcontroller. These wake-up source flags are cleared once the CA-IF1021Lx-Q1 leaves standby mode

## 9.4.1. Remote Wake-up

The bus wake-up, also called remote wake-up, changes the transceiver's operation mode from sleep mode to standby mode. A falling edge on the LIN Bus, followed by a valid dominant bus signal for  $t > t_{wake(dom)LIN}$ , bus results in a bus wake-up event. The mode change to standby mode is performed with the subsequent rising edge on the LIN bus(the change from dominant to recessive), see Figure 9-2. Remote Wake-up.

Figure 9-2. Remote Wake-up

Remote wake-up capability allows the CA-IF1021Lx-Q1 to restore power to the node upon detection of LIN bus activity. Once a successful wake-up event is detected. The external microcontroller can drive the SLP\_N high based on the wake-up signal from RXD for normal operation. RXD is floating until a valid wake-up is received during sleep mode, see Figure 9-1 for more details.

#### 9.4.2. Local Wake-Up

A valid local wake-up request is generated when the logic level on WAKE\_N changes to low and remains low-level stable for  $t_{wake(dom)WAKE_N}$ . The WAKE\_N pin has internal pull-up towards pin  $V_{BAT}$ . However, for the unused pin WAKE\_N, it is recommended to connect pin WAKE\_N to pin  $V_{BAT}$  to prevent EMI issues. The wake-up request is indicated by an active low signal on pin RXD, that can be used to interrupt the external microcontroller.

Also, it is possible to change a transceiver's mode from sleep mode to normal operation mode directly by setting the corresponding SLP\_N input to high at least the time t<sub>gotonorm</sub>. This feature is useful with an external microcontroller that is continuously powered, instead of being controlled by the INH output. The SLP\_N pin has integrated pull-down resistor to ensure the transceiver remains in sleep mode or in standby mode even in case the pin SLP\_N is unsupplied.

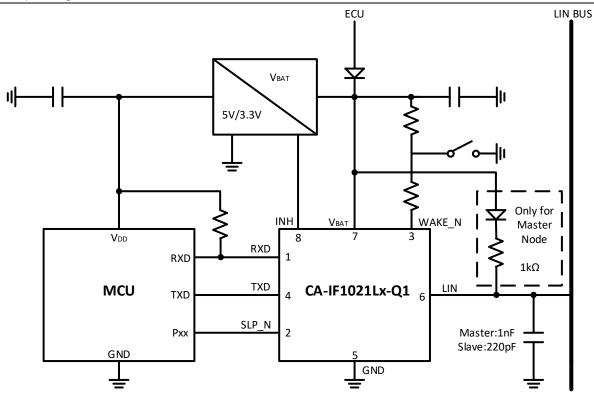

## 10. Application Information

The LIN interface is a single wire bidirectional bus used for in-vehicle networks. The CA-IF1021Lx-Q1 LIN transceiver is the interface between the microcontroller and physical LIN bus (see Figure 10-1). Every LIN network consists of a master node and one or more slave nodes. To configure the CA-IF1021Lx-Q1 transceiver for master node applications, a 1kΩ termination resistor and a diode must be connected between LIN bus and battery power supply V<sub>BAT</sub>, connect 1nF bypass capacitor between LIN and GND, see Figure 10-1. As there is an internal pull-up resistor with a serial diode structure to V<sub>BAT</sub> for the CA-IF1021Lx-Q1 LIN transmitter, so no external pull-up components are required for LIN slave node applications, a 220pF bypass capacitor is needed between LIN and GND.

The CA-IF1021Lx-Q1 devices support 3.3V and 5.0V logic input, allowing operation with a variety of microcontrollers with common I/O voltage levels. The receive data outputs RXD features open drain behavior for allowing the output level to the microcontroller supply voltage. In case the microcontroller port pin does not provide integrated pull-up, an external pull-up resistor connected to the microcontroller logic supply voltage is required as shown in below typical application circuit.

Figure 10-1. CA-IF1021 Typical Application Circuit in LIN Bus

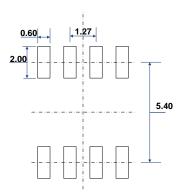

## 11. Package Information

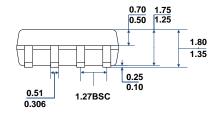

## **SOIC8 Package Outline**

## **TOP VIEW**

**RECOMMENDED LAND PATTERN**

**FRONT VIEW**

**LEFT-SIDE VIEW**

#### Note:

1. Controlling dimensions are in millimeters.

Figure 11-1. SOIC8 Package Outline

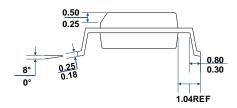

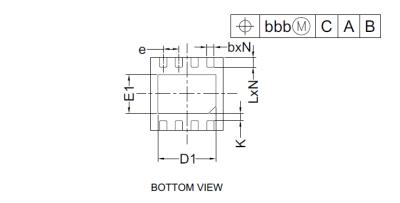

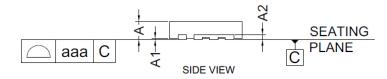

## **DFN8 Package Outline**

# COMMON DIMENSIONS (UNITS OF MEASURE=MILLIMETER)

| SYMBOL | MIN  | TYP     | MAX  |  |

|--------|------|---------|------|--|

| Α      | 0.70 | 0.75    | 0.80 |  |

| A1     | 0.00 | 0.02    | 0.05 |  |

| A2     |      | 0.203   |      |  |

| b      | 0.25 | 0.30    | 0.35 |  |

| D      | 2.90 | 3.00    | 3.10 |  |

| D1     | 2.35 | 2.40    | 2.45 |  |

| Е      | 2.90 | 3.00    | 3.10 |  |

| E1     | 1.55 | 1.60    | 1.65 |  |

| е      |      | 0.65BSC |      |  |

| L      | 0.35 | 0.40    | 0.45 |  |

| K      | 0.20 | -       | -    |  |

| Z      | 8    |         |      |  |

| aaa    | 0.08 |         |      |  |

| bbb    |      | 0.10    |      |  |

#### Note:

1. Controlling dimensions are in millimeters.

Figure 11-2. DFN8 Package Outline

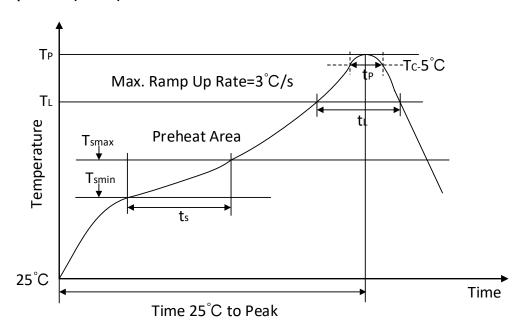

## 12. Soldering Temperature (reflow) Profile

Figure 12-1. Soldering Temperature (reflow) Profile

**Table 12-1. Soldering Temperature Parameter**

| Profile Feature                                                                | Pb-Free Assembly |

|--------------------------------------------------------------------------------|------------------|

| Average ramp-up rate(217 $^{\circ}{\mathbb C}$ to Peak)                        | 3°C/second max   |

| Time of Preheat temp(from 150 $^{\circ}\mathrm{C}$ to 200 $^{\circ}\mathrm{C}$ | 60-120 second    |

| Time to be maintained above 217 $^{\circ}\mathrm{C}$                           | 60-150 second    |

| Peak temperature                                                               | 260 +5/-0 °C     |

| Time within 5 ℃ of actual peak temp                                            | 30 second        |

| Ramp-down rate                                                                 | 6 °C/second max. |

| Time from 25°C to peak temp                                                    | 8 minutes max    |

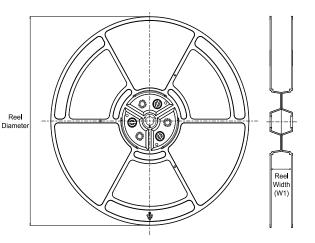

## 13. Tape and Reel Information

#### **REEL DIMENSIONS**

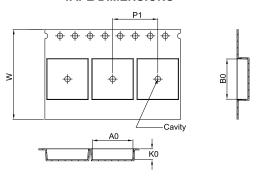

## **TAPE DIMENSIONS**

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

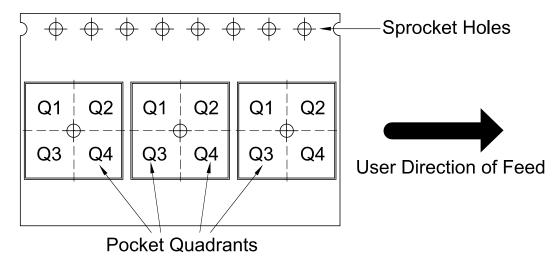

## **QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device         | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|------|------|--------------------------|-----------------------|------------|------------|------------|------------|-----------|------------------|

| CA-IF1021LS-Q1 | SOIC            | S                  | 8    | 2500 | 330                      | 12.4                  | 6.5        | 5.4        | 2.1        | 8          | 12        | Q1               |

| CA-IF1021LD-Q1 | DFN             | D                  | 8    | 3000 | 330                      | 12.4                  | 3.3        | 3.3        | 1.1        | 8          | 12        | Q1               |

19

## 14. Important Statement

The above information is for reference only and used for helping Chipanalog customers with design, research and development. Chipanalog reserves the rights to change the above information due to technological innovation without advance notice.

All Chipanalog products pass ex-factory test. As for specific practical applications, customers need to be responsible for evaluating and determining whether the products are applicable or not by themselves. Chipanalog's authorization for customers to use the resources are only limited to development of the related applications of the Chipanalog products. In addition to this, the resources cannot be copied or shown, and Chipanalog is not responsible for any claims, compensations, costs, losses, liabilities and the like arising from the use of the resources.

#### **Trademark information**

Chipanalog Inc.® and Chipanalog® are registered trademarks of Chipanalog.

http://www.chipanalog.com