# **CA-IF4888HS Bus-Polarity Correcting RS-485 Transceiver**

# 1 Key Features

- Meets Requirements of TIA/EIA-485A Standard

- Bus-Polarity Correction Within 114ms (t<sub>FS-max</sub>)

- Data Rate: 300bps to 500kbps

- Supply Voltage: 3V to 5.5V

- Current-limiting Driver and Thermal Shutdown Function

- Bus I/O ESD Protection:

- ±30kV HBM

- ±8kV IEC 61000-4-2 Contact Discharge

- 1/8 Unit Load (Up to 256 Nodes on a Bus)

- Operating Temperature Range: -40°C to 125°C

- Common Mode Voltage Range: ±15V

- Fault Protection Range: ±30V

- Low Power Current: 960µA (max.) @ Receive Mode

- Standby Current: < 5μA

- Narrow-Body SOIC8 Package

### 2 Applications

.

- Industrial Automation

- HVAC Systems

- DMX512-Networks

- Process Control

- Battery-Powered Applications

- Motion Control

Telecom Equipment

# 3 Description

The CA-IF4888HS is a low-power RS-485 transceiver with automatic bus-polarity correction. Upon hot plug-in, the device detects and corrects the bus polarity within the first 114ms ( $t_{FS-max}$ ) of bus idling. This device can extend the common mode voltage range to ±15V, and the fault protection range to ±30V. Therefore, this device is suitable for long cable applications. The bus pins are robust to electrostatic discharge (ESD) events, with high levels of protection to human-body model (HBM), and contact discharge specifications.

The CA-IF4888HS is available in a narrow-body SOIC8 package, which is suitable for space-constrained applications. This device is specified over ambient free-air temperature range of  $-40^{\circ}$ C to 125°C.

# **Device Information**

| PART<br>NUMBER | PACKAGE   | BODY SIZE (NOM) |

|----------------|-----------|-----------------|

| CA-IF4888HS    | SOIC8 (S) | 3.9mm × 4.9mm   |

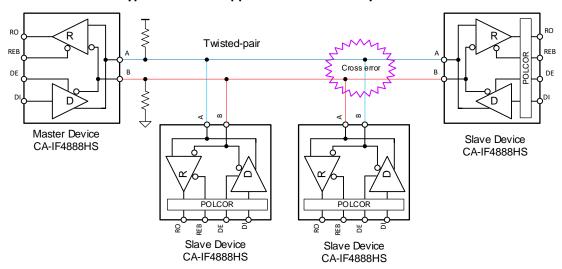

# **Typical Network Application With Polarity Correction**

# CA-IF4888HS

# Version 1.00

4 Ordering Guide

# Shanghai Chipanalog Microelectronics Co., Ltd.

# Table 4-1 Ordering Guide for Valid Ordering Part Number

| Part Number | Full/Half-Duplex | Function                          | Date Rate (kbps) | Package   |

|-------------|------------------|-----------------------------------|------------------|-----------|

| CA-IF4888HS | Half-Duplex      | Automatic bus-polarity correction | 500              | SOIC8 (S) |

# Table of Contents

| 1 | Кеу  | Features                              | 1 |

|---|------|---------------------------------------|---|

| 2 | Арр  | lications                             | 1 |

| 3 | Des  | cription                              | 1 |

| 4 | Ord  | ering Guide                           | 2 |

| 5 | Revi | ision History                         | 3 |

| 6 | Pin  | Descriptions and Functions            | 4 |

| 7 | Spe  | cifications                           | 5 |

|   | 7.1  | Absolute Maximum Ratings <sup>1</sup> | 5 |

|   | 7.2  | ESD Ratings                           | 5 |

|   | 7.3  | Recommended Operating Conditions      | 5 |

|   | 7.4  | Thermal Information                   | 5 |

|   | 7.5  | Electrical Characteristics            | 6 |

|   | 7.6  | Timing Characteristics                | 7 |

|   | 7.7  | Typical Characteristics               | 8 |

| 8 | Para | meter Measurement Information         | 9 |

| 9  | Det  | ailed Description              | 12 |

|----|------|--------------------------------|----|

|    | 9.1  | Overview                       | 12 |

|    | 9.2  | Device Function Mode           | 12 |

|    | 9    | 9.2.1 Driver                   | 12 |

|    | 9    | 9.2.2 Receiver                 | 12 |

|    | 9.3  | Bus Polarity Correction        | 13 |

| 10 |      | Application and Implementation | 15 |

|    | 10.1 | Power Supply Recommendation    | 15 |

|    | 10.2 | Cautions                       | 15 |

| 11 |      | Package Information            | 16 |

|    | 11.1 | SOIC8 (S) Package              | 16 |

| 12 |      | Soldering Information          | 17 |

| 13 |      | Tape and Reel Information      | 18 |

| 14 |      | Important Notice               | 19 |

# 5 Revision History

| Revision     | Description | Date       | Page |

|--------------|-------------|------------|------|

| Version 1.00 | NA          | 2022.02.08 | NA   |

CHIPANALOG

# Shanghai Chipanalog Microelectronics Co., Ltd.

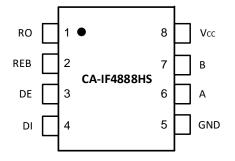

# 6 Pin Descriptions and Functions

# Table 6-1 CA-IF4888HS Pin Description and Functions

| NAME            | PIN NUMBER | ТҮРЕ                                                   | DESCRIPTION                                                          |  |  |

|-----------------|------------|--------------------------------------------------------|----------------------------------------------------------------------|--|--|

| RO              | 1          | Digital Output                                         | Receiver data output.                                                |  |  |

|                 |            |                                                        | Receiver enabled control, pulled up internally:                      |  |  |

| REB             | 2          | Digital Input                                          | 1. When REB is low, receiver is enabled;                             |  |  |

|                 |            |                                                        | 2. When REB is high or open, receiver is disabled.                   |  |  |

|                 |            |                                                        | Driver enabled control, pulled down internally:                      |  |  |

| DE              | 3          | Digital Input                                          | 1. When DE is high, driver is enabled;                               |  |  |

|                 |            |                                                        | 2. When DE is low or open, driver is disabled.                       |  |  |

| DI              | 4          | Digital Input                                          | Driver data input, pulled up internally.                             |  |  |

| GND             | 5          | Ground                                                 | Ground.                                                              |  |  |

| А               | 6          | Bus Input/Output                                       | Noninverting driver output/receiver input.                           |  |  |

| В               | 7          | Bus Input/Output                                       | Inverting driver output/receiver input.                              |  |  |

| V               | 0          | Dowor                                                  | Power supply input, bypass $V_{CC}$ to GND with at least $0.1 \mu F$ |  |  |

| V <sub>cc</sub> | 8          | 8 Power capacitors as close as possible to the device. |                                                                      |  |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings<sup>1</sup>

|                  | PARAMETER                               | MIN  | MAX                                | UNIT |

|------------------|-----------------------------------------|------|------------------------------------|------|

| V <sub>CC</sub>  | Supply voltage <sup>2</sup>             | -0.5 | 7                                  | V    |

| V <sub>IO</sub>  | Bus voltage of A and B <sup>2</sup>     | -30  | 30                                 | V    |

| V <sub>IO</sub>  | Input logical voltage of DI, DE and REB | -0.3 | 7                                  | V    |

| V <sub>IO</sub>  | Output logical voltage of RO            | -0.3 | V <sub>CC</sub> + 0.3 <sup>3</sup> | V    |

| TJ               | Junction Temperature                    |      | 150                                | °C   |

| T <sub>STG</sub> | Storage Temperature                     | -65  | 150                                | °C   |

|                  |                                         |      |                                    |      |

NOTE:

1. Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- 2. All voltage values are with respect to the ground terminal and are peak voltage values.

- 3. Maximum voltage must not exceed 7V.

# 7.2 ESD Ratings

|                                          |                                                                           |                        | VALUE | UNIT |  |

|------------------------------------------|---------------------------------------------------------------------------|------------------------|-------|------|--|

|                                          | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001                        | Bus pins (A, B) to GND | ±30   |      |  |

| V <sub>FSD</sub> Electrostatic discharge |                                                                           | All other pins         | ±6    | kV   |  |

| V <sub>ESD</sub> Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins |                        | ±2    |      |  |

| Contact discharge, per IEC 61000-4-2     |                                                                           | ±8                     | kV    |      |  |

# 7.3 Recommended Operating Conditions

|                   | PARAMETER                                  | MIN | NOM | MAX             | UNIT |

|-------------------|--------------------------------------------|-----|-----|-----------------|------|

| Vcc               | Supply voltage, with respect to GND        | 3.0 | 5.0 | 5.5             | V    |

| V <sub>IN</sub>   | Bus input voltage                          | -15 |     | 15              | V    |

| V <sub>IH</sub>   | High-level input voltage of DI, DE and REB | 2.0 |     | V <sub>CC</sub> | V    |

| V <sub>IL</sub>   | Low-level input voltage of DI, DE and REB  | 0   |     | 0.8             | V    |

| RL                | Differential load resistance               | 54  |     |                 | Ω    |

| 1/t <sub>UI</sub> | Data Rate                                  | 0.3 |     | 500             | kbps |

| T <sub>A</sub>    | Ambient Temperature                        | -40 |     | 125             | °C   |

| Tj                | Junction Temperature                       | -40 |     | 150             | °C   |

# 7.4 Thermal Information

|                  | THERMAL METRIC                            | SOIC8 (S) | UNIT |

|------------------|-------------------------------------------|-----------|------|

| R <sub>0JA</sub> | Junction-to-ambient thermal resistance    | 115       | °C/W |

| R <sub>θJC</sub> | Junction-to-case (top) thermal resistance | 60        | °C/W |

# CA-IF4888HS

# Version 1.00

# Shanghai Chipanalog Microelectronics Co., Ltd.

## 7.5 Electrical Characteristics

Over recommended operating temperature range (unless otherwise noted). All typical specifications are at  $T_A = 25^{\circ}C$  and  $V_{CC} = 5V$ .

|                               | PARAMETER                                          | TEST CONDITI                                                                                                                                   | IONS                           | MIN            | ТҮР                | MAX | UNIT |  |

|-------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------|--------------------|-----|------|--|

| Driver                        |                                                    |                                                                                                                                                |                                |                |                    |     |      |  |

|                               |                                                    | $R_L = 60\Omega, -15V \le V_{test} \le 15V$                                                                                                    | V, see Figure 8-1 <sup>1</sup> | 1.5            | 3.5                |     | V    |  |

|                               |                                                    | $ \begin{array}{l} {\sf R}_{\sf L} = 60\Omega, -15V \le V_{test} \le 15V,  4.5V \le Vcc \\ \le 5.5V,  see \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$ |                                | 2.1            |                    |     | v    |  |

| V <sub>OD</sub>               | Differential output voltage                        |                                                                                                                                                |                                | 2.1            |                    |     | v    |  |

|                               |                                                    | $R_L = 100\Omega$ , $C_L = 50pF$ , see F                                                                                                       | igure 8-2                      | 2              | 4                  |     | V    |  |

|                               |                                                    | $R_L = 54\Omega$ , $C_L = 50pF$ , see Fig                                                                                                      | gure 8-2                       | 1.5            | 3.7                |     | V    |  |

| ∆ V <sub>od</sub>             | Change in magnitude of                             |                                                                                                                                                |                                | -200           |                    | 200 | mV   |  |

|                               | differential-output voltage                        |                                                                                                                                                |                                | -200           |                    | 200 | IIIV |  |

| V <sub>oc</sub>               | Common-mode output voltage                         | $R_L = 100\Omega \text{ or } 54\Omega, C_L = 50p$                                                                                              | F, see Figure 8-2              | 1              | V <sub>cc</sub> /2 | 3   | V    |  |

| ∆V <sub>OC(SS)</sub>          | Change in magnitude of common-                     |                                                                                                                                                |                                | -200           |                    | 200 | mV   |  |

|                               | mode output voltage                                |                                                                                                                                                |                                | 200            |                    | 200 | 1110 |  |

| l <sub>os</sub>               | Driver short-circuit output current                | DE = $V_{CC}$ , $-7V \le V_0 \le 12V$ , o                                                                                                      | or A shorted to B              | -250           |                    | 250 | mA   |  |

| Receiver                      |                                                    | 1                                                                                                                                              |                                |                |                    |     |      |  |

|                               |                                                    |                                                                                                                                                | V <sub>I</sub> = 12V           |                | 72                 | 125 |      |  |

| li -                          | Bus input current                                  | $DE = 0V, V_{CC} = 0V \text{ or } 5V$                                                                                                          | $V_1 = -7V$                    | -100           | -43                |     | μA   |  |

| ••                            | bus input current                                  |                                                                                                                                                | V <sub>I</sub> = 15V           |                | 91                 | 125 | р.,  |  |

|                               |                                                    |                                                                                                                                                | V <sub>I</sub> = -15V          | -200           | -97                |     |      |  |

| V <sub>TH+</sub>              | Positive-going receiver input<br>voltage threshold | Over common-mode range                                                                                                                         |                                |                | -100               | -20 | mV   |  |

| V <sub>TH-</sub>              | Negative-going receiver input voltage threshold    |                                                                                                                                                |                                | -200           | -130               |     | mV   |  |

|                               | Receiver differential-input voltage                | -                                                                                                                                              |                                |                |                    |     |      |  |

| V <sub>HYS</sub> <sup>2</sup> | threshold hysteresis, $V_{TH+} - V_{TH-}$          |                                                                                                                                                |                                |                | 30                 |     | mV   |  |

| V <sub>он</sub>               | High-level output voltage                          | I <sub>он</sub> = –4mA                                                                                                                         |                                | $V_{CC} - 0.4$ | $V_{CC} - 0.2$     |     | V    |  |

| V <sub>OL</sub>               | Low-level output voltage                           | I <sub>OL</sub> = 4mA                                                                                                                          |                                |                | 0.2                | 0.4 | V    |  |

| I <sub>OZR</sub>              | High-impedance output current                      | REB = $V_{CC}$ , $V_0$ = 0V or $V_{CC}$                                                                                                        |                                | -1             |                    | 1   | μA   |  |

| Input Log                     | gic (DI, DE, REB)                                  |                                                                                                                                                |                                |                |                    |     |      |  |

| IN                            | Input Current                                      | $0V \le V_{IN} \le V_{CC}$                                                                                                                     |                                | -6.2           |                    | 6.2 | μA   |  |

| Supply                        |                                                    |                                                                                                                                                |                                |                |                    |     | •    |  |

|                               |                                                    | Both driver and receiver er                                                                                                                    | nabled, REB = 0V,              |                | 2.4                | 2   |      |  |

|                               |                                                    | $DE = V_{CC}$ , empty load, no sy                                                                                                              | witching                       |                | 2.4                | 3   |      |  |

|                               |                                                    | Driver enabled and receive                                                                                                                     | er disabled, REB =             |                | 0.8                | 1 0 |      |  |

|                               | Quieceent supply surrent                           | $V_{CC}$ , DE = $V_{CC}$ , empty load,                                                                                                         | no switching                   |                | 0.8                | 1.2 | mA   |  |

| I <sub>CC</sub>               | Quiescent supply current                           | Driver disabled and receive                                                                                                                    |                                | 0.7            | 0.06               |     |      |  |

|                               |                                                    | 0V, DE = 0V, empty load, no                                                                                                                    |                                | 0.7            | 0.96               | L   |      |  |

|                               |                                                    | Both driver and receiver disabled, REB = DI                                                                                                    |                                |                | 2.4                | 5   |      |  |

|                               |                                                    | = V <sub>CC</sub> , DE = 0V, empty load,                                                                                                       | , no switching                 | 2.4            |                    | 5   | μA   |  |

|                               | Thermal shutdown threshold                         |                                                                                                                                                |                                |                | 180                |     | °C   |  |

Over recommended operating temperature range (unless otherwise noted). All typical specifications are at  $T_A = 25^{\circ}$ C and  $V_{CC} = 5V$ .

| CA-IF4888HS  |

|--------------|

| Version 1.00 |

|              |

|                                     | PARAMETER                                                 | TEST CONDITIONS                                       | MIN | ТҮР | MAX | UNIT |

|-------------------------------------|-----------------------------------------------------------|-------------------------------------------------------|-----|-----|-----|------|

| Driver                              |                                                           |                                                       |     |     |     | -    |

| t <sub>r</sub> , t <sub>f</sub>     | Differential output rise and fall time                    |                                                       | 250 | 360 | 680 | ns   |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Driver propagation delay                                  | $R_L = 54\Omega$ , $C_L = 50pF$ , see Figure 8-3      |     | 280 | 500 | ns   |

| t <sub>SK(P)</sub>                  | Driver pulse skew,  t <sub>PHL</sub> – t <sub>PLH</sub>   |                                                       |     |     | 10  | ns   |

| t <sub>PHZ</sub> , t <sub>PLZ</sub> | Driver disable time                                       | see Figure 8-4 and Figure 8-5                         |     | 10  | 200 | ns   |

|                                     |                                                           | REB = 0V, see Figure 8-4 and Figure 8-5               |     | 100 | 600 | ns   |

| t <sub>PZH</sub> , t <sub>PZL</sub> | Driver enable time <sup>1</sup>                           | REB = V <sub>CC</sub> , see Figure 8-4 and Figure 8-5 |     | 7.2 | 11  | μs   |

| Receiver                            |                                                           |                                                       |     |     |     |      |

| t <sub>r</sub> , t <sub>f</sub>     | Receiver output rise and fall time                        |                                                       |     | 3.8 | 10  | ns   |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Receiver propagation delay time                           | $C_L = 15 pF^2$ , see Figure 8-6                      |     | 23  | 110 | ns   |

| t <sub>SK(P)</sub>                  | Receiver pulse skew,  t <sub>PHL</sub> – t <sub>PLH</sub> |                                                       |     |     | 7   | ns   |

| t <sub>PHZ</sub> , t <sub>PLZ</sub> | Receiver disable time                                     | See Figure 8-7                                        |     | 7   | 20  | ns   |

| t <sub>PZH(1)</sub> ,               |                                                           | DE = V <sub>cc</sub> , see Figure 8-7                 |     | 8   | 20  | ns   |

| t <sub>PZL(1)</sub> ,               | Receiver enable time <sup>3</sup>                         |                                                       |     |     |     |      |

| t <sub>PZH(2)</sub> ,               |                                                           | DE = OV, see Figure 8-8                               |     | 7   | 14  | μs   |

| t <sub>PZL(2)</sub>                 |                                                           |                                                       |     |     |     |      |

| t <sub>FS</sub>                     | Bus failsafe time                                         | Driver disabled                                       | 38  | 76  | 114 | ms   |

NO TE:

1. When DE and REB are shorted together, driver enable time refers to the case when REB = OV.

2. C<sub>L</sub> includes probe and fixture capacitance.

When DE and REB are shorted together, receiver enable time refers to the case when DE =  $V_{CC}$ . 3.

# CHIPANALOG

Shanghai Chipanalog Microelectronics Co., Ltd.

# CA-IF4888HS

# Version 1.00

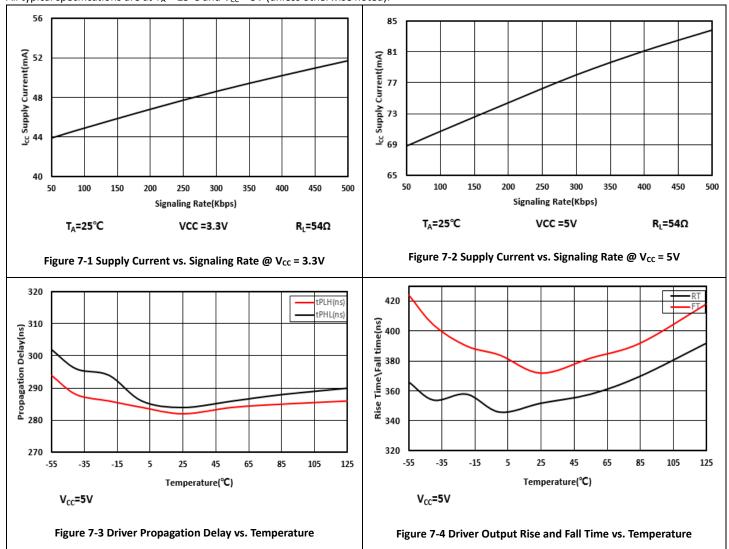

# 7.7 Typical Characteristics

All typical specifications are at  $T_A = 25^{\circ}C$  and  $V_{CC} = 5V$  (unless otherwise noted).

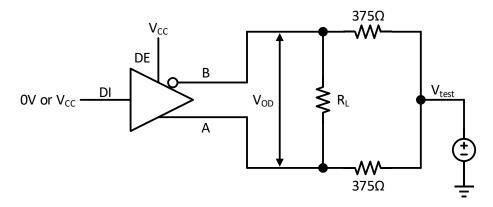

8 Parameter Measurement Information

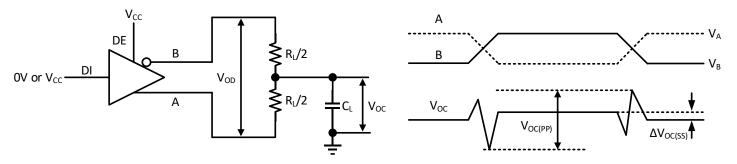

Figure 8-2 Measurement of Driver Differential and Common-Mode Output Voltage With RS-485 Load

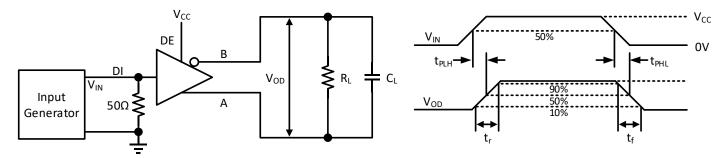

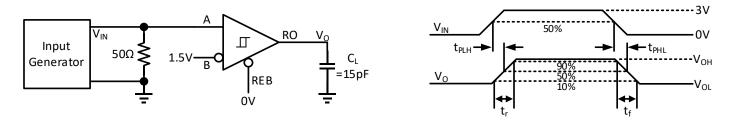

Figure 8-3 Measurement of Driver Output Rise and Fall Time and Propagation Delay

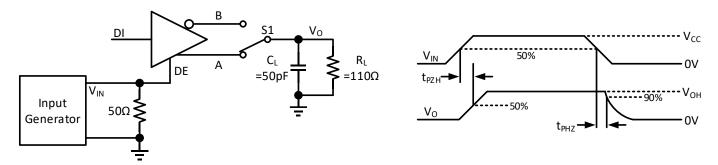

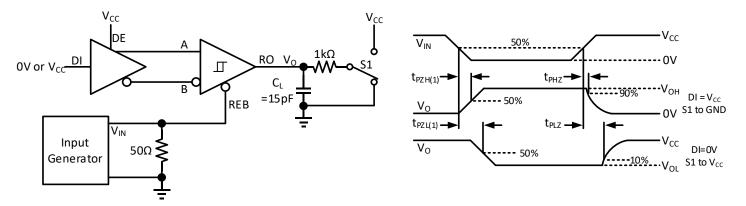

Figure 8-4 Measurement of Driver Enable and Disable Time With Active High Output and Pull-Down Load

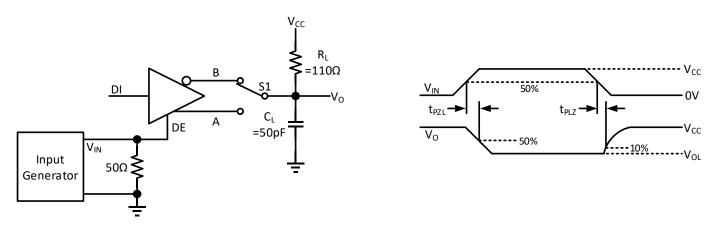

Figure 8-5 Measurement of Driver Enable and Disable Time With Active Low Output and Pull-Up Load

Figure 8-6 Measurement of Receiver Output Rise and Fall Time and Propagation Delay

Figure 8-7 Measurement of Receiver Enable/Disable Time With Driver Enabled

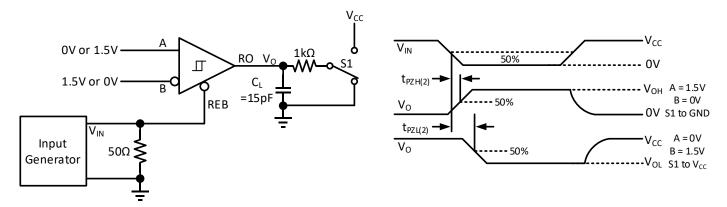

Figure 8-8 Measurement of Receiver Enable Time With Driver Disabled

# **CA-IF4888HS**

# Version 1.00

#### **Detailed Description** 9

#### **Overview** 9.1

The CA-IF4888HS device integrates hysteresis input thresholds to provide an internal bias for the receiver input threshold. When the bus is idle or short-circuited, the receiver output remains logic-high level without the need of an external fail-safe bias resistor. Device operation is specified over a wide ambient temperature range from -40°C to 125°C. The device integrates automatic bus polarity correction to detect crossover errors at initial power-up to exchange polarity definitions for buses A and B internally.

#### **Device Function Mode** 9.2

# 9.2.1 Driver

When the driver enabled pin DE is at logic high level, differential output A and B follow with the data input DI. Under normal mode, the logic high level of DI causes A to high level and B to low level. In this case, the differential output voltage of V<sub>OD</sub> = V<sub>A</sub>  $-V_{B}$  is defined to be positive. When DI is at low level, the output state is reversed: A becomes low level, B becomes high level, and V<sub>OD</sub> is negative.

When DE is at low level, both outputs of driver become high-impedance. In this case, the logic state at DI is irrelevant. The pin DE has an internal pull-down resistance to ground, so the driver is disabled when DE is open. The pin DI has an internal pull-up resistance to V<sub>CC</sub>, so the output A becomes high level and B becomes low level when DI is open as well as the driver is enabled under normal mode.

The truth table of driver is shown in Table 9-1. The detailed mechanism of polarity-correcting mode is shown in 9.3.

| INPUT                           | ENABLE                 | OUT    | PUT    | FUNCTION                   |  |  |

|---------------------------------|------------------------|--------|--------|----------------------------|--|--|

| DI <sup>2</sup> DE <sup>3</sup> |                        | A B    |        | FUNCTION                   |  |  |

| Normal Mode                     |                        |        |        |                            |  |  |

| Н                               | Н                      | Н      | L      | Actively drive bus high    |  |  |

| L                               | Н                      | L      | Н      | Actively drive bus low     |  |  |

| Х                               | L                      | High-Z | High-Z | Driver disabled            |  |  |

| Х                               | Open                   | High-Z | High-Z | Driver disabled by default |  |  |

| Open                            | Н                      | Н      | L      | Actively drive bus high    |  |  |

| POLARITY-CORREC                 | TING MODE <sup>4</sup> |        |        |                            |  |  |

| Н                               | Н                      | L      | Н      | Actively drive bus low     |  |  |

| L                               | Н                      | Н      | L      | Actively drive bus high    |  |  |

| Х                               | X L                    |        | High-Z | Driver disabled            |  |  |

| Х                               | X Open                 |        | High-Z | Driver disabled by default |  |  |

| Open H                          |                        | L H    |        | Actively drive bus low     |  |  |

# Table 9-1 Truth Table of Driver<sup>1</sup>

1. H = high level, L = low level, X = irrelevant, High-Z = high impedance.

DI is weakly pulled up to V<sub>cc</sub> internally. 2.

3. DE is weakly pulled down to GND internally.

The polarity-correcting mode is entered when  $V_{ID} < V_{TH-}$  and  $t > t_{FS-max}$  and DE = low. This state is latched when REB turns from low to high. 4.

# 9.2.2 Receiver

When the enable pin REB of receiver is logical low, receiver is enabled. The truth table of receiver is shown in Table 9-2. The detailed mechanism of polarity-correcting mode is shown in 9.3.

When CA-IF4888HS is under normal mode and the bus differential input voltage  $V_{ID}$  is greater than or equal to -20mV, receiver output RO is logical high. When V<sub>ID</sub> is less than or equal to -200mV, receiver output RO is logical low. When V<sub>ID</sub> is between -20mV and -200mV, receiver output RO is indeterminate.

When REB is logical high or open, the receiver output RO is high-impedance and is irrelevant to the magnitude and polarity of VID.

When the bus inputs are open, short or on idle state, a failsafe logic high output at RO pin is achieved, avoiding indeterminate state which may result in system communication errors.

| DIFFERENTIAL INPUT                   | DIFFERENTIAL INPUT ENABLE OUTPUT |                         |                                      |  |  |  |  |  |  |

|--------------------------------------|----------------------------------|-------------------------|--------------------------------------|--|--|--|--|--|--|

| $V_{ID} = V_A - V_B$                 | REB <sup>2</sup> RO              |                         | FUNCTION                             |  |  |  |  |  |  |

| ormal Mode                           |                                  |                         |                                      |  |  |  |  |  |  |

| $V_{ID} \ge -20mV$                   | L                                | Н                       | Output valid high                    |  |  |  |  |  |  |

| $-200 mV < V_{ID} < -20 mV$          | L                                | ?                       | Indeterminate bus state              |  |  |  |  |  |  |

| $V_{ID} \leq -200 mV$                | L                                | L                       | Output valid low                     |  |  |  |  |  |  |

| X                                    | н                                | High-Z                  | Receiver disabled                    |  |  |  |  |  |  |

| Х                                    | Open                             | High-Z                  | Receiver disabled by default         |  |  |  |  |  |  |

| Open-circuit bus                     | L                                | H after t <sub>FS</sub> | Failsafe output high                 |  |  |  |  |  |  |

| Short-circuit bus                    | L                                | H after t <sub>FS</sub> | Failsafe output high                 |  |  |  |  |  |  |

| Idle (terminated) bus                | L                                | H after t <sub>FS</sub> | Failsafe output high                 |  |  |  |  |  |  |

| OLARITY-CORRECTING MODE <sup>3</sup> | · · ·                            |                         | -                                    |  |  |  |  |  |  |

| $V_{ID} \ge -20mV$                   | L                                | L                       | Output valid low (polarity corrected |  |  |  |  |  |  |

| $-200 mV < V_{ID} < -20 mV$          | L                                | ?                       | Indeterminate bus state              |  |  |  |  |  |  |

| $V_{ID} \leq -200 mV$                | L                                | Н                       | Output valid high (polarity correcte |  |  |  |  |  |  |

| Х                                    | Н                                | High-Z                  | Receiver disabled                    |  |  |  |  |  |  |

| X                                    | Open                             | High-Z                  | Receiver disabled by default         |  |  |  |  |  |  |

| Open-circuit bus                     | L                                | H after t <sub>FS</sub> | Failsafe output high                 |  |  |  |  |  |  |

| Short-circuit bus                    | L                                | H after t <sub>FS</sub> | Failsafe output high                 |  |  |  |  |  |  |

| Idle (terminated) bus                | L                                | H after t <sub>FS</sub> | Failsafe output high                 |  |  |  |  |  |  |

# Table 9-2 Truth Table of Receiver<sup>1</sup>

H = high level, L = low level, X = irrelevant, High-Z = high impedance, Open = no connection, ? = indeterminate. 1.

2. REB is weakly pulled up to V<sub>CC</sub> internally.

The polarity-correcting mode is entered when  $V_{ID} < V_{TH-}$  and  $t > t_{FS-max}$  and DE = low. This state is latched when REB turns from low to high. 3.

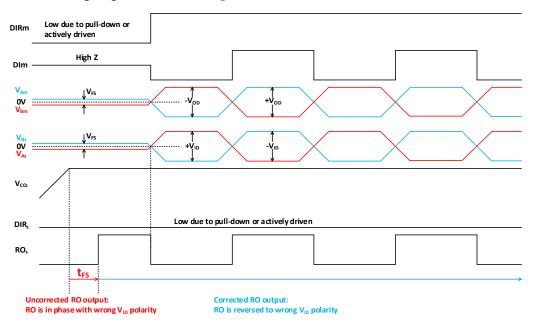

#### 9.3 **Bus Polarity Correction**

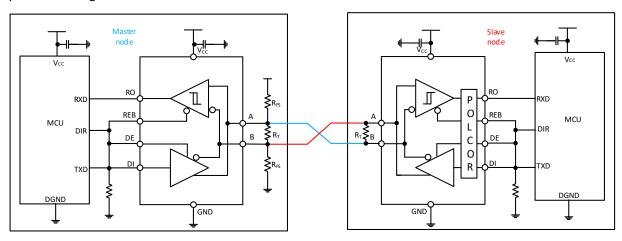

The CA-IF4888HS automatically corrects a wrong bus-signal polarity caused by cross-wire fault. The typical application is shown in Figure 9-1. In order to detect the bus polarity, all three of the following conditions must be met:

A failsafe-biasing network (commonly at the master node) must define the signal polarity of the bus; 1.

A slave node must enable the receiver and disable the driver (REB = DE = 0V); 2.

3. The bus must be idle for the failsafe time, t<sub>FS-max</sub>.

After the failsafe time has passed, the polarity correction completes and is applied to both the receiving and transmitting channels. The status of the bus polarity is latched within the transceiver and is maintained for subsequent data transmissions.

Prior to initiating data transmission, the master transceiver must be idle for a time span that exceeds the maximum failsafe time,  $t > t_{FS-max}$ , of a slave transceiver. This idle time is accomplished by driving the direction control line (DIR) low. After the time  $t > t_{FS-max}$ , of a slave transceiver. t<sub>FS-max</sub>, the master could begin transmitting data.

Because of the indicated cross-wire fault between master and slave, the slave node receives bus signals with reversed polarity. Assuming the slave node has just been connected to the bus, the direction-control pin is pulled-down during power-up and then

# CA-IF4888HS Version 1.00

# Shanghai Chipanalog Microelectronics Co., Ltd.

is actively driven low by the slave MCU. The polarity correction begins as soon as the slave supply is established and ends after the time span which ranges from 38ms to 114ms.

Figure 9-1 Bus Polarity Correction in Point-to-Point Application

Initially the slave receiver assumes that the correct bus polarity is applied to the inputs and performs no polarity reversal. Because of the reversed polarity of the bus-failsafe voltage, the output of the slave receiver turns low. After  $t_{FS}$  has passed and the receiver has detected the wrong bus polarity, the internal POLCOR logic reverses the input signal and output of receiver turns high. At this point all incoming bus data with reversed polarity are polarity corrected within the transceiver. Because polarity correction is also applied to the transmitting path, the data sent by the slave MCU are reversed by the POLCOR logic and then fed into the driver.

The reversed data from the slave MCU are reversed again by the cross-wire fault in the bus, and the correct bus polarity is reestablished at the master end. This process repeats each time when the device powers up and detects an incorrect bus polarity.

The bus polarity correction timing diagram is shown in Figure 9-2.

# **10** Application and Implementation

# 10.1 Power Supply Recommendation

To ensure reliable operation at all data rates and supply voltages, each supply should be decoupled with at least  $0.1\mu$ F ceramic capacitors located as close as possible to the supply pins. This helps to reduce supply voltage ripple present on the outputs of switched-mode power supplies and also helps to compensate for the resistance and inductance of the PCB power planes. At the same time, please keep the voltage in V<sub>CC</sub> pin with respect to GND pin is below 5.5V.

# 10.2 Cautions

Because of the bus correction feature in CA-IF4888HS, the data string durations of consecutive 0s or 1s exceeding  $t_{FS-min}$  (38ms) can accidently trigger a wrong polarity correction and must be avoided. The minimum recommended data rate of CA-IF4888HS is 300bps.

# CA-IF4888HS

Version 1.00

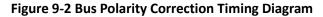

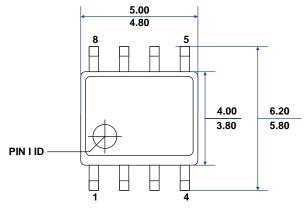

# 11 Package Information

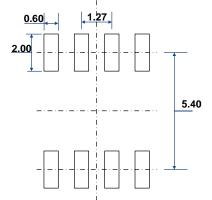

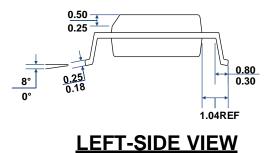

# 11.1 SOIC8 (S) Package

The values for the dimensions are shown in millimeters.

TOP VIEW

**FRONT VIEW**

Shanghai Chipanalog Microelectronics Co., Ltd.

# **RECOMMENDED LAND PATTERN**

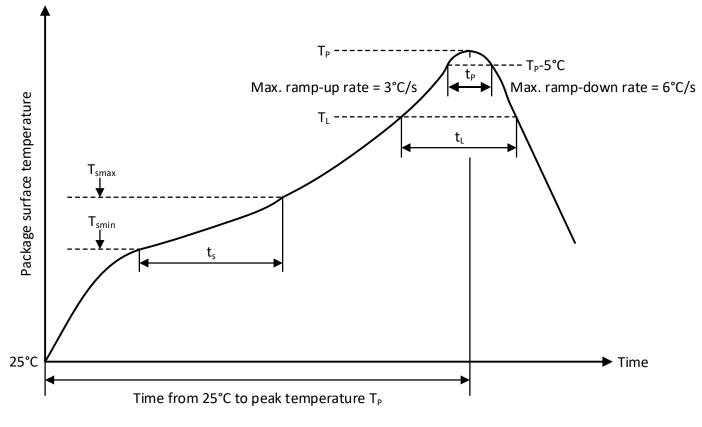

# **12** Soldering Information

# Figure 12-1 Soldering Temperature Curve

| Profile Feature                                                                              | Pb-Free Soldering |  |  |  |  |  |

|----------------------------------------------------------------------------------------------|-------------------|--|--|--|--|--|

| Ramp-up rate ( $T_L = 217^{\circ}C$ to peak $T_P$ )                                          | 3°C/s max         |  |  |  |  |  |

| Time t <sub>s</sub> of preheat temp (T <sub>smin</sub> = 150°C to T <sub>smax</sub> = 200°C) | 60~120 seconds    |  |  |  |  |  |

| Time t <sub>L</sub> to be maintained above 217°C                                             | 60~150 seconds    |  |  |  |  |  |

| Peak temperature T <sub>P</sub>                                                              | 260°C             |  |  |  |  |  |

| Time t <sub>P</sub> within 5°C of actual peak temp                                           | 30 seconds max    |  |  |  |  |  |

| Ramp-down rate (peak $T_P$ to $T_L = 217^{\circ}C$ )                                         | 6°C/s max         |  |  |  |  |  |

| Time from 25°C to peak temperature T <sub>P</sub>                                            | 8 minutes max     |  |  |  |  |  |

# **Table 12-1 Soldering Temperature Parameters**

Version 1.00

**CA-IF4888HS**

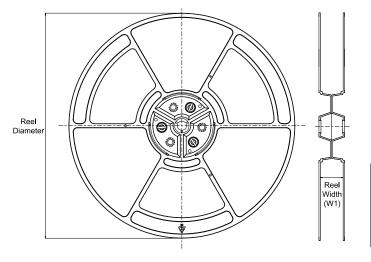

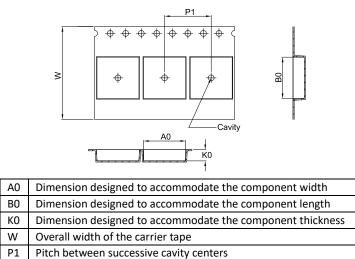

**13** Tape and Reel Information

### **REEL DIMENSIONS**

TAPE DIMENSIONS

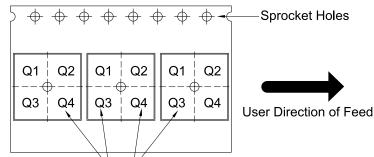

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

Pocket Quadrants

\*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| CA-IF4888HS | SOIC            | S                  | 8    | 2500 | 330                      | 12.4                     | 6.5        | 5.4        | 2.1        | 8.0        | 12.0      | Q1               |

# 14 Important Notice

The above information is for reference only and is used to assist Chipanalog customers in design and development. Chipanalog reserves the right to change the above information due to technological innovation without prior notice.

Chipanalog products are all factory tested. The customers shall be responsible for self-assessment and determine whether it is applicable for their specific application. Chipanalog's authorization to use the resources is limited to the development of related applications that the Chipanalog products involved in. In addition, the resources shall not be copied or displayed. And Chipanalog shall not be liable for any claim, cost, and loss arising from the use of the resources.

### **Trademark Information**

Chipanalog Inc. <sup>®</sup>, Chipanalog<sup>®</sup> are trademarks or registered trademarks of Chipanalog.

http://www.chipanalog.com