# 1.5W, 5kV<sub>RMS</sub> Complete Isolated DC-DC Converter

#### 1 Features

#### Complete Switch Mode Power Supply

- High integration with internal transformer

- Soft-start reduces input inrush current and output overshoot

- Hiccup current-limit protection

- Thermal shutdown

- 4.5 V to 5.5 V Input Voltage Range

- Selectable Output voltages

- 3.3V and 5V output options

- 3.7V and 5.4V output options provide headroom voltage to power LDO

- Delivers up to 1.5W(5V/300mA) Typical Output Power

- Excellent Load Transient Response

- Complies with CISPR32 Class B Radiated Emissions

- Up to ±3kV HBM and ±2kV CDM ESD protection

- Robust Galvanic Isolation Barrier

- High lifetime: > 40 years

- Up to 5kV<sub>RMS</sub> isolation rating

- ±150 kV/µs typical CMTI

- Wide Operating Temperature Range: -40°C to 125°C

- Low Profile SOIC16-WB (10.30mm×7.50mm) Package

- Safety-Related Certifications

- VDE certification according to DIN EN IEC 60747-17(VDE 0884-17):2021-10

- UL certification according to UL 1577

- CQC certification according to GB4943.1-2022

- TUV certification (Pending)

#### 2 Applications

- Instruments and Apparatuses

- Industrial automation

- Motor Control

- Medical Equipment

- Industrial Sensors

- Telecom Equipment

#### 3 General Description

The CA-IS3115AW is a family of complete isolated DC-DC converters with up to 5kV<sub>RMS</sub> isolation rating. These devices integrate most of the components needed for an isolated power supply —switching controller, power switches, transformer, soft-start, protection circuit etc. — into a single, compact SOIC package. The result is an efficient and compact fully integrated solution that is easy to comply with EMI requirements and makes power-supply isolation design as easy as possible. Operating over an input voltage range of 4.5V to 5.5V, the CA-IS3115AW devices provide a fixed output voltage of 3.3V, 3.7V, 5V or 5.4V set by pin SEL. 3.7V and 5.4V output options provide headroom voltage to power an LDO. Only output, input bypass capacitors, and a pull-up resistor for 3.7V or 5.4V outputs are needed to finish the design.

The CA-IS3115AW devices feature a unique control scheme, which can quickly respond to load transient and accurately regulate the output voltage. The devices are capable of delivering a load up to 1.5W output power and offering soft-start, current limit, short-circuit protection and thermal shutdown protection features to better enhance the reliability of the system. The CA-IS3115AW devices include an enable input pin (EN). Connect the EN pin to the VINP input voltage or force this pin high to turn on the DC-DC converter. Force this pin low to disable the device and enter shutdown mode. In shutdown mode, the device stops switching operation with microampere standby supply current.

The CA-IS3115AW devices are available in wide-body SOIC16 package with creepage and clearance > 8mm, and operate over -40°C to +125°C temperature range.

#### **Device Information**

| Part number | Package      | Package size<br>(NOM) |

|-------------|--------------|-----------------------|

| CA-IS3115AW | SOIC16-WB(W) | 10.30 mm × 7.50 mm    |

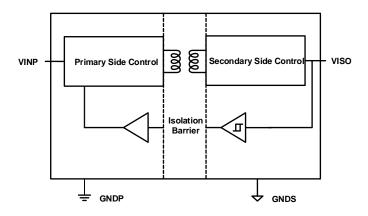

# **Simplified Block Diagram**

# 4 Ordering Information

**Table 4-1. Ordering Information**

| Part #      | Output Power (W) | Isolation Rating(kV <sub>RMs</sub> ) | Package   |

|-------------|------------------|--------------------------------------|-----------|

| CA-IS3115AW | 1.5              | 5.0                                  | SOIC16-WB |

# **Table of Contents**

| 1 | Feat | ures                                     | 1 |

|---|------|------------------------------------------|---|

| 2 | App  | lications                                | 1 |

| 3 |      | eral Description                         |   |

| 4 |      | ering Information                        |   |

| 5 |      | sion history                             |   |

| 6 |      | . Configuration and Description          |   |

| 7 |      | cifications                              |   |

|   | 7.1  | Absolute Maximum Ratings <sup>1, 2</sup> |   |

|   | 7.2  | ESD Ratings                              | 5 |

|   | 7.3  | Recommended Operating Conditions         | 5 |

|   | 7.4  | Thermal Information                      | 5 |

|   | 7.5  | Power Ratings                            | 5 |

|   | 7.6  | Insulation Specifications                | ε |

|   | 7.7  | Safety-Related Certifications            | 7 |

|   | 7.8  | Electrical Characteristics               | 8 |

|   | 7.9  | MSL                                      | 8 |

| 7.10  | Typ                                                                                            | pical Operating Characteristics                                                                                    |                      |

|-------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------|

| Deta  | iled I                                                                                         | Description                                                                                                        | 13                   |

| 8.1   | Ov                                                                                             | erview                                                                                                             | 13                   |

| 8.2   | Ou                                                                                             | tput Voltage Selection                                                                                             | 13                   |

| 8.3   | Pro                                                                                            | otection Functions                                                                                                 | 14                   |

| 8.    | 3.1                                                                                            | UVLO and Soft-Start                                                                                                | 14                   |

| 8.    | 3.2                                                                                            | Current-limit Protection                                                                                           | 14                   |

| 8.    | 3.3                                                                                            | Thermal Shutdown                                                                                                   | 14                   |

| Appli | icatio                                                                                         | ons Information                                                                                                    | 15                   |

| 9.1   | Тур                                                                                            | pical Application Circuit                                                                                          | 15                   |

| 9.2   | Inp                                                                                            | out and Output Capacitors                                                                                          | 15                   |

| 9.3   | PC                                                                                             | B Layout Guidelines                                                                                                | 15                   |

| Packa | age I                                                                                          | nformation                                                                                                         | 17                   |

|       | _                                                                                              |                                                                                                                    |                      |

| Tape  | and                                                                                            | Reel Information                                                                                                   | 19                   |

| •     |                                                                                                |                                                                                                                    |                      |

|       | Detai<br>8.1<br>8.2<br>8.3<br>8.<br>8.<br>Appli<br>9.1<br>9.2<br>9.3<br>Packa<br>Solde<br>Tape | Detailed I 8.1 Ov 8.2 Ou 8.3 Pro 8.3.1 8.3.2 8.3.3  Application 9.1 Ty 9.2 Inp 9.3 Po Package I Soldering Tape and | Detailed Description |

# 5 Revision history

| Revision Number     | Description                                                   | Revised Date | Page Changed |  |

|---------------------|---------------------------------------------------------------|--------------|--------------|--|

| Preliminary Version | N/A                                                           | 2023/10/17   | N/A          |  |

| Version 1.00        | Update isolation ratings                                      | 2023/12/01   | 6,7          |  |

| Version 1.01        | Adds output derating curves                                   | 2024/01/03   | 11,12        |  |

| Version 1.02        | Adds Short circuit protection function description            | 2024/01/09   | 14           |  |

| Version 1.03        | Update VDE, UL, CQC, TUV information                          | 2024/04/16   | 1,6,7        |  |

| VEISIOII 1.05       | Update the test conditions of V <sub>IOSM</sub>               | 2024/04/10   | 1,0,7        |  |

| Version 1.04        | Update the test conditions of V <sub>ISO(LOAD)</sub>          | 2024/05/14   | 8            |  |

|                     | Add Capacitor value range in VISO pin in table of section 7.3 |              |              |  |

| Version 1.05        | Update the Maximum Value of I <sub>VINP_SC</sub>              | 2024/06/19   | 5,8,16       |  |

|                     | Update Figure 9-2. Recommended Bypass Capacitors Placement    |              |              |  |

|                     | Update VDE information:                                       |              |              |  |

|                     | Add Maximum impulse voltage V <sub>IMP</sub>                  |              |              |  |

| Version 1.06        | 2. Update Maximum surge isolation voltage V <sub>IOSM</sub>   | 2024/09/05   | 1,6,7        |  |

|                     | Update CQC certification standards                            |              |              |  |

|                     | Add TUV certification information                             |              |              |  |

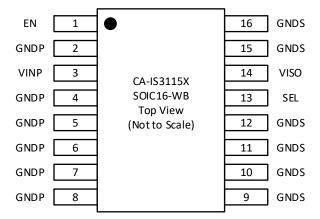

# 6 Pin Configuration and Description

Figure 6-1. CA-IS3115AW Top View

Table 6-1. CA-IS3115AW Pin Description

| Pin name | Pin number            | Туре                                            | Description                                                                        |

|----------|-----------------------|-------------------------------------------------|------------------------------------------------------------------------------------|

| EN       | 1                     | Input                                           | Enable input, active-high. Force this pin high to enable the device. Force this    |

| EIN      | EN 1                  |                                                 | pin low to disable the device and put the device into shutdown mode.               |

| VIND     | VINP 3                |                                                 | Primary side supply input. Connect VINP to GNDP with both $0.1\mu F$ and $10\mu F$ |

| VIINE    |                       |                                                 | capacitors as close to the device(pin 3 and pin 4) as possible.                    |

| GNDP     | 2, 4, 5, 6, 7, 8      | 2, 4, 5, 6, 7, 8 GND Primary side local ground. |                                                                                    |

| GNDS     | 9, 10, 11, 12, 15, 16 | GND                                             | Secondary side ground return connection for V <sub>ISO</sub> .                     |

|          |                       |                                                 | Output voltage V <sub>ISO</sub> select pin:                                        |

|          | 13                    |                                                 | V <sub>ISO</sub> = 5.0 V when SEL is shorted to VISO;                              |

| SEL      |                       | Innut                                           | $V_{ISO}$ = 5.4 V when SEL is connected to VISO through a 100k $\Omega$ resistor;  |

| SEL      | 15                    | Input                                           | V <sub>ISO</sub> = 3.3 V when SEL is shorted to GNDS;                              |

|          |                       |                                                 | $V_{ISO}$ = 3.7V when SEL is connected to GNDS through a 100k $\Omega$ resistor.   |

|          |                       |                                                 | Don't leave SEL pin open.                                                          |

| VISO     | 1.4                   | Power                                           | Isolated supply voltage pin. Connnect VISO to GNDS with both 0.1µF and             |

| VISO     | 14                    | Power                                           | 10μF capacitors as close to the device(pin 14 and pin 15) as possible.             |

# Shanghai Chipanalog Microelectronics Co., Ltd. 7 Specifications

# 7.1 Absolute Maximum Ratings<sup>1, 2</sup>

|                  | Parameters                | Minimum<br>value | Maximum<br>value                   | Unit |

|------------------|---------------------------|------------------|------------------------------------|------|

| V <sub>INP</sub> | Power supply voltage      | -0.5             | 6.0                                | V    |

| V <sub>ISO</sub> | Isolated supply voltage   | -0.5             | 6.0                                | V    |

| EN               | EN input voltage          | -0.5             | V <sub>INP</sub> +0.3 <sup>3</sup> | V    |

| SEL              | SEL input voltage         | -0.5             | V <sub>ISO</sub> +0.3 <sup>3</sup> | V    |

| T <sub>J</sub>   | Junction temperature      | -40              | 150                                | °C   |

| T <sub>STG</sub> | Storage temperature range | -65              | 150                                | °C   |

#### Notes:

- 1. The stresses listed under "Absolute Maximum Ratings" are stress ratings only, not for functional operation condition. Exposure to absolute maximum rating conditions for extended periods may cause permanent damage to the device.

- 2. All voltage values are with respect to the local ground (GNDP or GNDS) and are peak voltage values.

- 3. Maximum voltage must not be exceed 6 V.

#### 7.2 ESD Ratings

|                                          |                                                                                        | Value | Unit |

|------------------------------------------|----------------------------------------------------------------------------------------|-------|------|

| V Floring that a displacement            | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>1</sup>              | ±3000 | V    |

| V <sub>ESD</sub> Electrostatic discharge | Charged device model (CDM), per JEDEC Specification JESD22-C101, all pins <sup>2</sup> | ±2000 | V    |

#### Notes:

- 1. Per JEDEC document JEP155, 500V HBM allows safe manufacturing of standard ESD control process.

- 2. Per JEDEC document JEP157, 250V CDM allows safe manufacturing of standard ESD control process.

#### 7.3 Recommended Operating Conditions

|                   | Parameters                        | Minimum<br>value | Typical<br>value | Maximum<br>value | Unit |

|-------------------|-----------------------------------|------------------|------------------|------------------|------|

| V <sub>INP</sub>  | Power supply voltage              | 4.5              | 5                | 5.5              | V    |

| V <sub>EN</sub>   | EN input voltage                  | 0                |                  | 5.5              | V    |

| V <sub>ISO</sub>  | Isolated supply voltage           | 0                |                  | 5.7              | V    |

| V <sub>SEL</sub>  | SEL input voltage                 | 0                |                  | 5.7              | V    |

| C <sub>VISO</sub> | Capacitor value range in VISO pin | 4.7              | 10               | 1000             | μF   |

| T <sub>A</sub>    | Ambient Temperature               | -40              |                  | 125              | °C   |

| TJ                | Junction temperature              | -40              |                  | 150              | °C   |

#### 7.4 Thermal Information

|                  | Thousand Matria                        | CA-IS3115AW  | Unit |

|------------------|----------------------------------------|--------------|------|

| Thermal Metric   |                                        | SOIC16-WB(W) | Unit |

| $R_{\theta JA}$  | Junction-to-ambient thermal resistance | 68           | °C/W |

| R <sub>θJC</sub> | Junction-to-case thermal resistance    | 18           |      |

#### 7.5 Power Ratings

|         | Parameters        | Test Conditions                                          | Minimum<br>value | Typical<br>value | Maximum<br>value | Unit |

|---------|-------------------|----------------------------------------------------------|------------------|------------------|------------------|------|

| $P_{D}$ | Power dissipation | $V_{INP}$ = 5.5V, $V_{ISO}$ = 5.4V, 300mA output current |                  |                  | 3                | W    |

# CHIPANALOG

#### 7.6 Insulation Specifications

|                   | PARAMETR                                          | TEST CONDITIONS                                                                                                                                                                                                       | VALUE              | UNIT             |  |

|-------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------|--|

| CLR               | External clearance <sup>1</sup>                   | Shortest terminal-to-terminal distance through air                                                                                                                                                                    | 8                  | mm               |  |

| CPG               | External creepage <sup>1</sup>                    | Shortest terminal-to-terminal distance across the package surface                                                                                                                                                     | 8                  | mm               |  |

| DTI               | Distance through the insulation                   | Minimum internal gap (internal clearance)                                                                                                                                                                             | 28                 | μm               |  |

| CTI               | Comparative tracking index                        | DIN EN 60112 (VDE 0303-11); IEC 60112                                                                                                                                                                                 | > 600              | V                |  |

|                   | Material group                                    | According to IEC 60664-1                                                                                                                                                                                              | I                  |                  |  |

|                   |                                                   | Rated mains voltage ≤ 300V <sub>RMS</sub>                                                                                                                                                                             | I-IV               |                  |  |

|                   | Overvoltage category per IEC 60664-1              | Rated mains voltage ≤ 600V <sub>RMS</sub>                                                                                                                                                                             | I-IV               |                  |  |

|                   | 5 5 7.                                            | Rated mains voltage ≤ 1000V <sub>RMS</sub>                                                                                                                                                                            | I-III              |                  |  |

| DIN EN IE         | C 60747-17 (VDE 0884-17) <sup>2</sup>             | S AMO                                                                                                                                                                                                                 |                    |                  |  |

| V <sub>IORM</sub> | Maximum repetitive peak isolation voltage         | AC voltage (bipolar)                                                                                                                                                                                                  | 2121               | V <sub>PK</sub>  |  |

|                   |                                                   | AC voltage; Time dependent dielectric breakdown (TDDB)                                                                                                                                                                | 1500               | V <sub>RMS</sub> |  |

| $V_{IOWM}$        | Maximum working isolation voltage                 | Test                                                                                                                                                                                                                  |                    |                  |  |

|                   |                                                   | DC voltage                                                                                                                                                                                                            | 2121               | V <sub>DC</sub>  |  |

| $V_{IOTM}$        | Maximum transient isolation voltage               | V <sub>TEST</sub> = V <sub>IOTM</sub> ,<br>t = 60s (qualification);<br>V <sub>TEST</sub> = 1.2 × V <sub>IOTM</sub> ,<br>t= 1s (100% production)                                                                       | 7070               | V <sub>PK</sub>  |  |

| V <sub>IMP</sub>  | Maximum impulse voltage                           | 1.2/50-µs waveform per IEC 62368-1                                                                                                                                                                                    | 9846               | V <sub>PK</sub>  |  |

| V <sub>IOSM</sub> | Maximum surge isolation voltage <sup>3</sup>      | V <sub>IOSM</sub> ≥ 1.3 x V <sub>IMP</sub> ; Tested in oil (qualification test),<br>1.2/50-μs waveform per IEC 62368-1                                                                                                | 12800              | V <sub>PK</sub>  |  |

|                   |                                                   | Method a, After input/output safety test subgroup 2/3, $V_{ini} = V_{IOTM}$ , $t_{ini} = 60s$ ; $V_{pd(m)} = 1.2 \times V_{IORM}$ , $t_m = 10s$                                                                       | ≤5                 |                  |  |

| $q_{pd}$          | Apparent charge⁴                                  | Method a, After environmental tests subgroup 1, $V_{ini} = V_{IOTM}$ , $t_{ini} = 60s$ ; $V_{pd(m)} = 1.6 \times V_{IORM}$ , $t_m = 10s$                                                                              | ≤5                 | pC               |  |

|                   |                                                   | Method b1, At routine test (100% production) and preconditioning (type test) $V_{\text{ini}} = 1.2 \times V_{\text{IOTM}}, t_{\text{ini}} = 1s;$ $V_{\text{pd(m)}} = 1.875 \times V_{\text{IORM}}, t_{\text{m}} = 1s$ | ≤5                 |                  |  |

| C <sub>IO</sub>   | Barrier capacitance, input to output <sup>5</sup> | $V_{IO} = 0.4 \times \sin(2\pi ft), f = 1MHz$                                                                                                                                                                         | 3.5                | pF               |  |

| · · ·             |                                                   | V <sub>IO</sub> = 500V, T <sub>A</sub> = 25°C                                                                                                                                                                         | > 1012             | <u> </u>         |  |

| $R_{IO}$          | Isolation resistance <sup>5</sup>                 | $V_{1O} = 500V, 100^{\circ}C \le T_{A} \le 125^{\circ}C$                                                                                                                                                              | > 10 <sup>11</sup> | Ω                |  |

|                   |                                                   | V <sub>IO</sub> = 500V at T <sub>S</sub> = 150°C                                                                                                                                                                      | > 109              |                  |  |

|                   | Pollution degree                                  |                                                                                                                                                                                                                       | 2                  |                  |  |

| UL 1577           | <u> </u>                                          | <u> </u>                                                                                                                                                                                                              |                    | Ī                |  |

| V <sub>ISO</sub>  | Maximum withstanding isolation voltage            | $V_{TEST} = V_{ISO}$ , t = 60s (qualification),<br>$V_{TEST} = 1.2 \times V_{ISO}$ , t = 1s (100% production)                                                                                                         | 5000               | V <sub>RMS</sub> |  |

#### NOTE:

- 1. Creepage and clearance requirements should be applied according to the specific equipment isolation standards of an application. Care should be taken to maintain the creepage and clearance distance of a board design to ensure that the mounting pads of the isolator on the printed-circuit board do not reduce this distance. Creepage and clearance on a printed-circuit board become equal in certain cases. Techniques such as inserting grooves and/or ribs on a printed circuit board are used to help increase these specifications.

- 2. This coupler is suitable for safe electrical insulation only within the safety ratings. Compliance with the safety ratings shall be ensured by means of suitable protective circuits.

- 3. Testing is carried out in air or oil to determine the intrinsic surge immunity of the isolation barrier.

- 4. Apparent charge is electrical discharge caused by a partial discharge (pd).

- 5. All pins on each side of the barrier tied together creating a two-terminal device.

# Shanghai Chipanalog Microelectronics Co., Ltd.

# 7.7 Safety-Related Certifications

| VDE                               | UL                             | CQC                    | TUV (Pending)                     |  |  |

|-----------------------------------|--------------------------------|------------------------|-----------------------------------|--|--|

| Certified according to DIN EN IEC | Certified according to UL 1577 | Certified according to | Certified according to EN 61010-1 |  |  |

| 60747-17(VDE 0884-17):2021-10;    | Component Recognition          | GB4943.1-2022          | and EN 62368-1                    |  |  |

| EN IEC 60747-17:2020+AC:2021      | Program                        |                        |                                   |  |  |

| VIORM: 2121VPK                    | Single protection:             | Reinforced isolation   | EN 61010-1                        |  |  |

| VIОТМ: 7070VРК                    | 5000V <sub>RMS</sub>           | (Altitude ≤ 5000m)     | 5000V <sub>RMS</sub>              |  |  |

| VIOSM: 12800VPK                   |                                |                        |                                   |  |  |

|                                   |                                |                        | EN 62368-1                        |  |  |

|                                   |                                |                        | 5000V <sub>RMS</sub>              |  |  |

| Certification number:             | Certification number:          | Certification number:  | Certification number              |  |  |

| 40057278 (reinforced isolation)   | E511334                        | CQC23001406424         | EN 61010-1: pending               |  |  |

|                                   |                                |                        | EN 62368-1: pending               |  |  |

#### 7.8 Electrical Characteristics

Over operating temperature range  $T_A$  = -40 to 125°C,  $V_{INP}$  = 4.5V to 5.5V, SEL connected to  $V_{ISO}$ ,  $C_{VINP}$  =  $C_{VISO}$  = 10 $\mu$ F, unless otherwise specified. All typical specs are at  $T_A$  = 25°C and  $V_{INP}$  = 5V.

|                                       | Parameters                                              | Test Conditions                                                                                                | Minimum<br>value    | ТҮР   | Maximum<br>value    | Unit     |  |

|---------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------|-------|---------------------|----------|--|

| Power Sup                             | ply Input                                               |                                                                                                                |                     |       |                     |          |  |

| I <sub>VINP_SD</sub> V <sub>INP</sub> | shutdown current                                        | EN = LOW                                                                                                       |                     | 0.5   | 30                  | μΑ       |  |

|                                       |                                                         | EN = HIGH, SEL connected to V <sub>ISO</sub> (5V output)                                                       |                     | 4.9   | 20                  | mA       |  |

| I <sub>VINP_O</sub>                   | V <sub>INP</sub> quiescent current                      | EN = HIGH, SEL 100kΩ to VISO (5.4Voutput)                                                                      |                     | 5.2   | 20                  | mA       |  |

| _                                     | I <sub>OUT</sub> = 0% load                              | EN = HIGH, SEL connected to GNDS (3.3V output)                                                                 |                     | 4.1   | 20                  | mA       |  |

|                                       |                                                         | EN = HIGH, SEL 100kΩ to GNDS (3.7V output)                                                                     |                     | 4.3   | 20                  | mA       |  |

| I <sub>VINP_SC</sub> [                | DC current from VINP supply under short circuit on VISO | VISO short to GNDS                                                                                             |                     | 77    | 125                 | mA       |  |

| V <sub>UVLO+</sub>                    | Input undervoltage lockout rising threshold             |                                                                                                                |                     | 2.7   | 3                   | V        |  |

| V <sub>UVLO</sub> -                   | Input undervoltage lockout falling threshold            |                                                                                                                | 2.1                 | 2.3   |                     | V        |  |

| V <sub>HYS(UVLO)</sub>                | Input undervoltage lockout hysteresis                   |                                                                                                                |                     | 0.4   | 0.6                 | V        |  |

| EN, SEL pir                           | ns                                                      |                                                                                                                |                     |       |                     |          |  |

| V <sub>IH_EN</sub>                    | EN Input threshold, logic HIGH                          |                                                                                                                | 0.7V <sub>INP</sub> |       |                     | V        |  |

| V <sub>IL_EN</sub>                    | EN Input threshold, logic LOW                           |                                                                                                                |                     |       | 0.3V <sub>INP</sub> | V        |  |

| I <sub>EN</sub>                       | Input leakage current                                   | $V_{INP} = 5V$ , $V_{EN} = 5V$                                                                                 |                     | 10    | 20                  | μΑ       |  |

| Isolated D                            | C-DC Converter                                          |                                                                                                                | •                   |       |                     |          |  |

|                                       |                                                         | SEL connected to V <sub>ISO</sub> (5V output), I <sub>ISO</sub> = 150mA                                        | 4.75                | 5.0   | 5.25                |          |  |

| .,                                    | Isolated output voltage                                 | SEL 100KΩ to VISO (5.4V output), I <sub>ISO</sub> = 150mA                                                      | 5.13                | 5.4   | 5.67                | l        |  |

| $V_{ISO}$                             |                                                         | SEL connected to GNDS (3.3V output), I <sub>ISO</sub> = 200mA                                                  | 3.13                | 3.3   | 3.47                | V        |  |

|                                       |                                                         | SEL 100KΩ to GNDS (3.7V output), I <sub>ISO</sub> = 200mA                                                      | 3.51                | 3.7   | 3.89                | 1        |  |

|                                       |                                                         | SEL connected to V <sub>ISO</sub> (5V output)                                                                  | 240                 | 300   |                     |          |  |

|                                       |                                                         | SEL 100KΩ to VISO (5.4V output)                                                                                | 240                 | 300   |                     | 1 .      |  |

| ILOAD_MAX                             | Maximum load currrent                                   | SEL connected to GNDS (3.3V output)                                                                            | 320                 | 400   |                     | mA       |  |

|                                       |                                                         | SEL 100KΩ to GNDS (3.7V output)                                                                                | 320                 | 400   |                     |          |  |

|                                       |                                                         | 20MHz bandwidth, SEL short to VISO (5V input, 5V or                                                            |                     |       |                     |          |  |

| $VISO_{(RIP)}$                        | Voltage ripple on isolated supply output (pk-pk)        | 5.4V output),I <sub>ISO</sub> = 150mA                                                                          |                     | 65    |                     |          |  |

|                                       |                                                         | 20MHz bandwidth, SEL short to GNDS (5V input, 3.3V or                                                          |                     | 55    |                     | mV       |  |

|                                       |                                                         | 3.7V output), I <sub>ISO</sub> = 200mA                                                                         |                     | 33    |                     |          |  |

|                                       |                                                         | SEL short to VISO (5V or 5.4V output), I <sub>ISO</sub> = 150mA,                                               |                     | 4     | 20                  |          |  |

| VISO(LINE)                            | Line regulation                                         | V <sub>INP</sub> = 4.5V to 5.5 V                                                                               |                     |       | 20                  | mV/V     |  |

| · · · · · (LINE)                      |                                                         | SEL short to GNDS (3.3V or 3.7V output), I <sub>ISO</sub> = 200mA,                                             |                     | 4     | 20                  | ,        |  |

|                                       |                                                         | V <sub>INP</sub> = 4.5V to 5.5V                                                                                |                     |       |                     |          |  |

|                                       |                                                         | SEL short to VISO (5V input, 5V or 5.4V output), I <sub>ISO</sub> = 0 to                                       |                     | 0.5%  | 2%                  | 1        |  |

| VISO(LOAD)                            | Load regulation                                         | 240mA                                                                                                          |                     | 0.50/ | 20/                 | -        |  |

|                                       |                                                         | SEL short to GNDS (5V input, 3.3V or 3.7V output), I <sub>ISO</sub> = 0 to 320mA                               |                     | 0.5%  | 2%                  |          |  |

|                                       |                                                         | $I_{ISO} = 300 \text{ mA}, C_{LOAD} = 0.1 \mu\text{F} \mid 10 \mu\text{F}; V_{ISO} = 5 \text{V}, 5.4 \text{V}$ |                     | 60%   |                     | -        |  |

| EFF                                   | Efficiency@maximum load current                         | $I_{ISO} = 300$ mA, $C_{LOAD} = 0.1\mu$ F   $10\mu$ F, $V_{ISO} = 3.3V$ , $3.7V$                               |                     | 50%   |                     | 1        |  |

| CMTI Common mode transient immunities |                                                         | Slew Rate of GNDP versus GNDS, V <sub>CM</sub> =1200V <sub>RMS</sub>                                           | ±150                | JU/0  |                     | kV/μs    |  |

| CMTI Common-mode transient immunity   |                                                         | ·                                                                                                              | -130                | 1     |                     |          |  |

| t <sub>RISE</sub>                     | V <sub>ISO</sub> rise time                              | 10% to 90%, V <sub>ISO</sub> =3.3V, 3.7V, 5.0V, 5.4V                                                           |                     |       |                     | ms<br>mV |  |

|                                       | voltage (peak to peak)                                  | 10% to 90% load step with 10mA/µs slew-rate; VISO                                                              |                     | 100   |                     | mV       |  |

| v <sub>iso</sub> load tr              | ansient response                                        | ripple voltage difference at two loads                                                                         |                     | 5     |                     | μs       |  |

#### 7.9 MSL

| Parameters |     | Standard               | Level |  |  |

|------------|-----|------------------------|-------|--|--|

|            | MSL | IPC/JEDEC J-STD-020D.1 | MSL 3 |  |  |

#### Shanghai Chipanalog Microelectronics Co., Ltd.

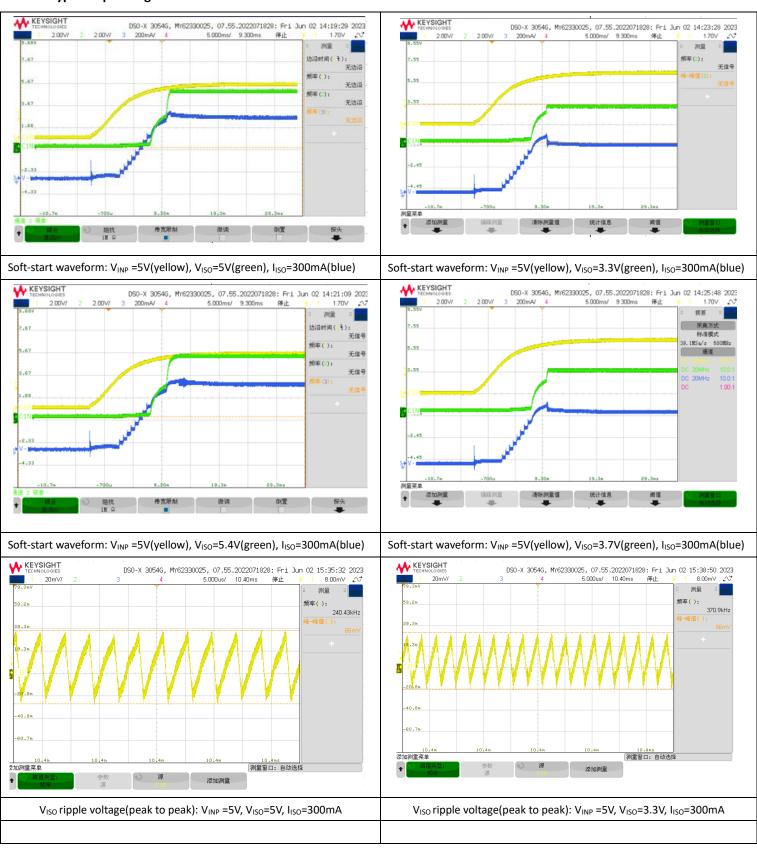

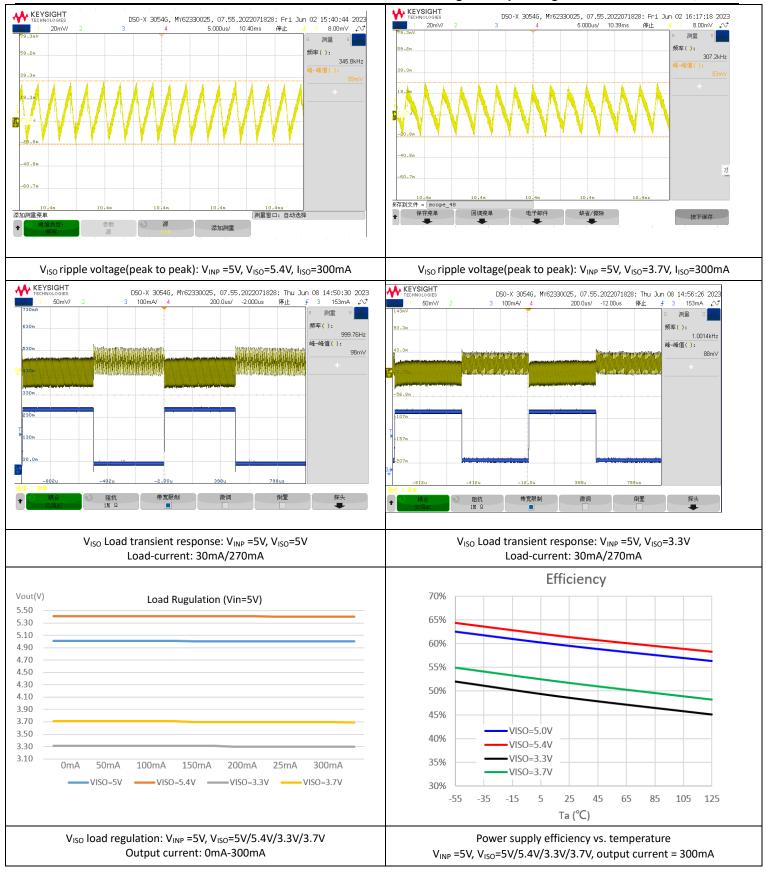

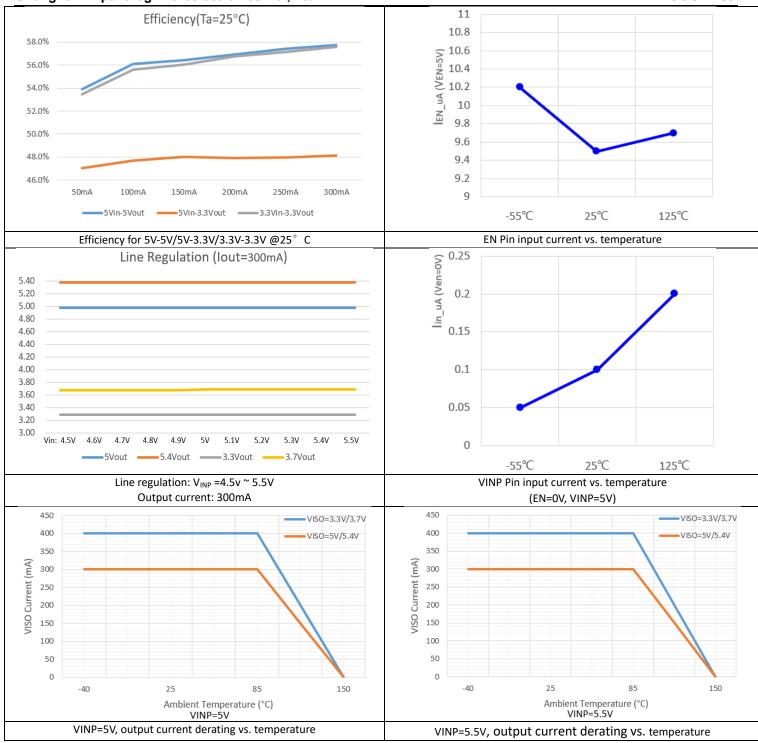

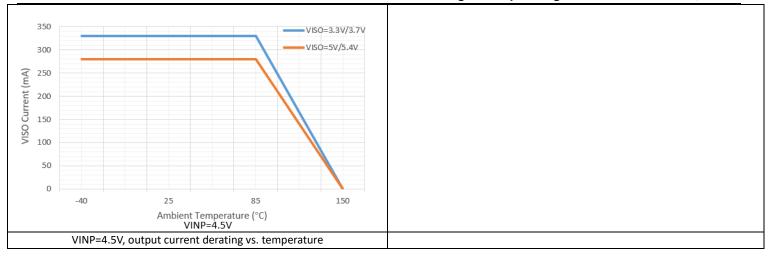

#### 7.10 Typical Operating Characteristics

#### **CA-IS3115AW**

# Version 1.06

# CHIPANALOG

#### Shanghai Chipanalog Microelectronics Co., Ltd.

### Shanghai Chipanalog Microelectronics Co., Ltd.

Version 1.06

### **CA-IS3115AW**

# Shanghai Chipanalog Microelectronics Co., Ltd.

#### 8 Detailed Description

#### 8.1 Overview

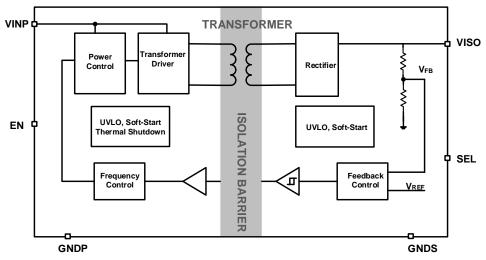

The CA-IS3115AW is a family of complete isolated DC-DC converters designed to provide isolated power with up to 1.5W output power across a 5kV<sub>RMS</sub> isolation barrier. The devices operate over 4.5V to 5.5V input voltage range and use a proprietary control mechanism. The input supply V<sub>INP</sub> is provided to the primary power controller that switches the power stage connected to the integrated transformer. Power is transferred to the secondary side and regulated to a fixed output voltage set by the SEL pin. The soft-start feature allows to reduce input inrush current and avoid output overshoot. These devices also incorporate an output enable (EN) control and undervoltage lockout(UVLO) function that allows the user to turn on the part at the desired input-voltage level. Figure 8-1 shows the CA-IS3115AW's functional block diagram. Connect the EN pin to VINP or force this pin high to turn on the DC-DC converter. Force this pin low to disable the device and enter low-current shutdown mode. These devices offer a ready-made, reliable, easy-to-use solution and allow users save PCB space and reduce design time for the popular 5V, 3.3V power supply systems.

These devices are provided with a robust overcurrent protection scheme that protects the devices under overload and output short-circuit conditions. A cycle-by-cycle peak current limit turns off the switching operation and triggers hiccup mode. Once the hiccup timeout period expires, soft-start is attempted again. Hiccup mode operation ensures low power dissipation under output short-circuit conditions.

Figure 8-1. Functional Block Diagrams

#### 8.2 Output Voltage Selection

At startup, the CA-IS3115AW monitors the state of pin SEL after applying  $V_{\text{INP}}$  supply voltage above the UVLO rising threshold or enabling via the EN pin, to build the desired regulation voltage level for the  $V_{\text{ISO}}$  output. See Table 8-1 for the output voltage selection.

| EN   | SEL             | VISO        |  |  |

|------|-----------------|-------------|--|--|

| High | Sorted to VISO  | 5V          |  |  |

| High | 100kΩ to VISO   | 5.4V        |  |  |

| High | Shorted to GNDS | 3.3V        |  |  |

| High | 100KΩ to GNDS   | 3.7V        |  |  |

| High | OPEN            | Unsupported |  |  |

| Low  | X               | 0V          |  |  |

Table 8-1. VISO Output Voltage Selection

Note: Don't leave SEL pin open.

#### 8.3 Protection Functions

#### 8.3.1 UVLO and Soft-Start

The CA-IS3115AW undervoltage lockout (UVLO) on both  $V_{INP}$  power supply and  $V_{ISO}$  isolated supply. Upon power-up, the primary side transformer driver is disabled while the  $V_{INP}$  voltage is below the threshold voltage  $V_{UVLO+}(2.7V, typ.)$ , and  $V_{ISO}$  output is off. The output powers up once the threshold is met. This allows the user to turn on the part at stable input-voltage level.

For many applications, it is necessary to minimize the inrush current at start-up. The CA-IS3115AW devices built-in soft-start circuit significantly reduces the start-up current spike and output voltage overshoot. Once input power supply is applied at VINP pin, the internal soft-start circuit will control the power delivered to the output gradually increase, allowing for a graceful turn-on ramp.

#### 8.3.2 Current-limit Protection

The CA-IS3115AW devices are provided with an over-current protection scheme that protects the device under overload and output short-circuit conditions. A cycle-by-cycle peak current limit turns off the switching operation and triggers a hiccup mode whenever the switch current exceeds the internal current limit. Once the hiccup timeout period expires, soft-start is attempted again. The hiccup condition is cleared when the over-current is removed.

#### 8.3.3 Thermal Shutdown

Thermal-shutdown protection limits total power dissipation in the device. When the junction temperature of the device exceeds  $175^{\circ}C(T_{SD})$ , an on-chip thermal sensor shuts down the device, allowing the device to cool. The thermal sensor turns the device on again after the junction temperature cools and junction temperature drops to normal operation temperature range (<  $150^{\circ}C$ ) of the device.

#### 9 Applications Information

#### 9.1 Typical Application Circuit

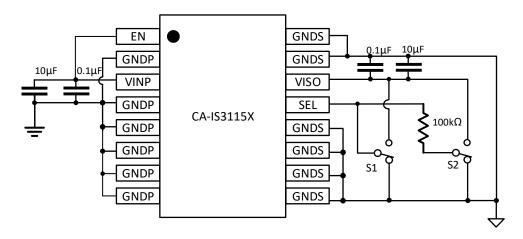

The CA-IS3115AW devices are high-integration isolated power supply solution. Included in the package are the switching controller, power switches, transformer, and all support components. Only output and input bypass capacitors are needed to finish the design. For the applications with LDO post regulator, it needs a single  $100k\Omega$  external resistor to set the output level to 3.7V or 5.4V, see Figure 9-1 typical application circuit.

Figure 9-1. CA-IS3115AW Typical Application Circuit

#### 9.2 Input and Output Capacitors

The input capacitors (between VINP and GNDP) are required to reduce the peak current drawn from input power source and reduce the switching noise, increase efficiency. For the input capacitors, choose the ceramic capacitor because they have the lowest equivalent series resistance (ESR), smallest size, and lowest cost. For most applications, we recommend to use at least  $0.1\mu\text{F}$  and  $10\mu\text{F}$  ceramic capacitors with X5R or X7R temperature characteristic.

The output capacitors between VISO and GNDS are required as well to keep the output voltage ripple small and to ensure loop stability. These bypass capacitors must have low impedance at the switching frequency. Ceramic capacitors are recommended due to their small size and low ESR. Make sure the capacitors do not degrade their capacitance significantly over temperature and DC bias. It is recommended to have at least  $10\mu F$  of effective capacitance at output.

#### 9.3 PCB Layout Guidelines

High switching frequencies and large peak currents make PCB layout a very important part of the isolated DC-DC converter design. Good PCB design minimizes excessive electromagnetic interference (EMI) and voltage gradients in the ground plane to avoid instability and regulation errors. Even with the high level of integration, like CA-IS3115AW, users may fail to achieve specified operation with a haphazard or poor layout. So careful PCB layout is critical to achieve clean and stable operation, and ensure that the grounding and heat sinking are acceptable.

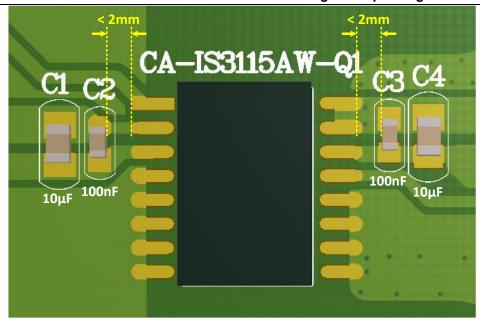

Place the input capacitors, output capacitors, and the CA-IS3115AW IC on the same PCB layer. Place decoupling capacitors as close as possible to the CA-IS3115AW device pins, see Figure 9-2 recommended components placement for the PCB layout. The paths must be wide and short to minimize inductance, also any via holes must be avoided on these paths. Connect all of the ground (GNDP, GNDS) connections to as large a plane area as possible for best heat-sinking. To ensure isolation performance between the primary side and secondary side, on the top layer and bottom layer keep the space under the CA-IS3115AW device free from traces, vias, and pads to maintain maximum creepage distance (≥ 8mm).

Figure 9-2. Recommended Bypass Capacitors Placement

9.30

#### 10 Package Information

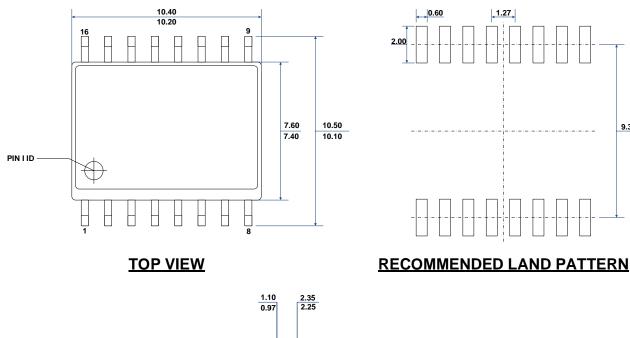

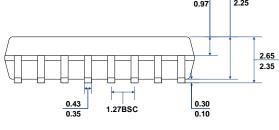

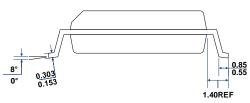

The following figure illustrates the size drawing and recommended pad size of SOIC16-WB wide-body package for the CA-IS3115AW isolated DC-DC converter. All dimensions are in millimeters.

FRONT VIEW

**LEFT-SIDE VIEW**

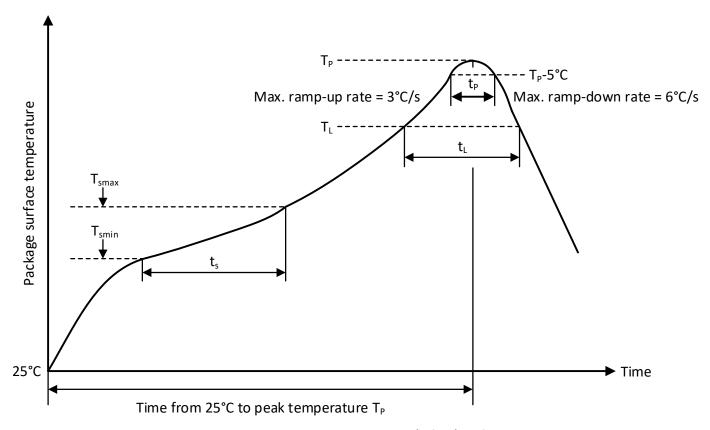

# 11 Soldering Temperature (reflow) Profile

Figure 11-1. Soldering Temperature (reflow) Profile

**Table 11-1. Soldering Temperature Parameter**

| Profile Feature                                                          | Pb-Free Soldering |

|--------------------------------------------------------------------------|-------------------|

| Ramp-up rate ( $T_L = 217^{\circ}C$ to peak $T_P$ )                      | 3°C/s max         |

| Time $t_s$ of preheat temp ( $T_{smin} = 150$ °C to $T_{smax} = 200$ °C) | 60~120 seconds    |

| Time t <sub>L</sub> to be maintained above 217°C                         | 60~150 seconds    |

| Peak temperature T <sub>P</sub>                                          | 260°C             |

| Time t <sub>P</sub> within 5°C of actual peak temp                       | 30 seconds max    |

| Ramp-down rate (peak $T_P$ to $T_L = 217$ °C)                            | 6°C/s max         |

| Time from 25°C to peak temperature T <sub>P</sub>                        | 8 minutes max     |

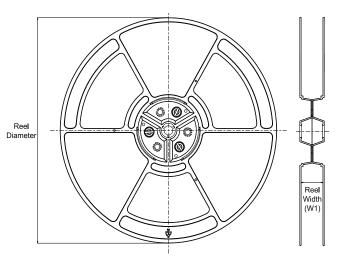

# 12 Tape and Reel Information

#### **REEL DIMENSIONS**

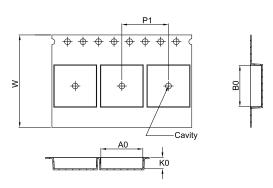

#### **TAPE DIMENSIONS**

| A0 | Dimension designed to accommodate the component width     |  |  |  |  |  |  |

|----|-----------------------------------------------------------|--|--|--|--|--|--|

| В0 | Dimension designed to accommodate the component length    |  |  |  |  |  |  |

| K0 | Dimension designed to accommodate the component thickness |  |  |  |  |  |  |

| W  | Overall width of the carrier tape                         |  |  |  |  |  |  |

| P1 | Pitch between successive cavity centers                   |  |  |  |  |  |  |

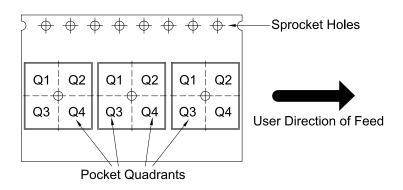

#### **QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

#### \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|------|------|--------------------------|-----------------------|------------|------------|------------|------------|-----------|------------------|

| CA-IS3115AW | SOIC            | W                  | 16   | 1000 | 330                      | 16.4                  | 10.8       | 10.7       | 2.9        | 12.0       | 24.0      | Q1               |

#### 13 Important statement

The above information is for reference only and used for helping Chipanalog customers with design, research and development. Chipanalog reserves the rights to change the above information due to technological innovation without advance notice.

All Chipanalog products pass ex-factory test. As for specific practical applications, customers need to be responsible for evaluating and determining whether the products are applicable or not by themselves. Chipanalog's authorization for customers to use the resources are only limited to development of the related applications of the Chipanalog products. In addition to this, the resources cannot be copied or shown, and Chipanalog is not responsible for any claims, compensations, costs, losses, liabilities and the like arising from the use of the resources.

#### **Trademark information**

Chipanalog Inc.® and Chipanalog® are registered trademarks of Chipanalog.

http://www.chipanalog.com