# CA-IF1169 High-speed CAN System Basis Chip with LDO and Watchdog

#### 1. Features

- Meets the requirements of ISO 11898-2:2016 and SAE J2284-1 to SAE J2284-5 physical layer standards

- ASIL-B compliant: designed with complete functional safety development process, supporting customer to achieve ASIL-B certification

- CAN FD Support: enables CAN FD data transmission up to 5 Mbit/s

- Support selective wake to wake-up specific partial networking nodes

- CAN bus pins short-circuit protection to ±42 V, ideal for 12V battery systems

- Autonomous bus biasing

- Integrated dual low-drop voltage regulators (LDO):

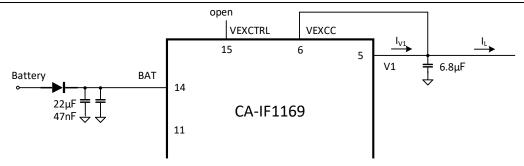

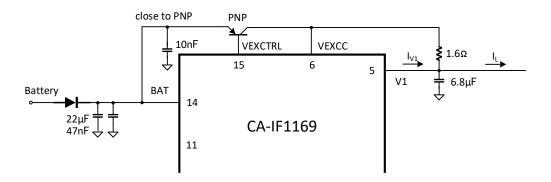

- LDO 1 (V1): 3.3V and 5V output voltage option with up to 250mA output current capability. Supports current extension via an external PNP transistor for increased output capacity, to provide power supply for system microcontroller or other loads

- LDO 2 (V2): 5V output voltage with up to 100mA output current capability, provide power supply for internal CAN transceiver and other loads.

- Advanced ECU power management

- Ultra-low power consumption in sleep mode:

12.8μA (typical)

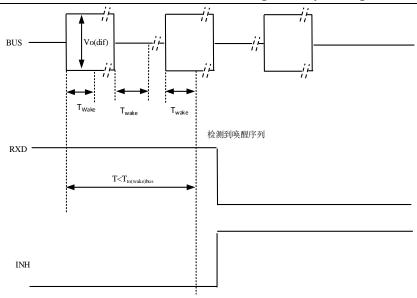

- Remote wake-up via standard CAN wake-up pattern(WUP) or selective wake-up frame (WUF) according to ISO 11898-2:2016

- Selective wake supports 50kbit/s, 100kbit/s, 125kbit/s, 250kbit/s, 500kbit/s and 1Mbit/s CAN hit-rate

- Local wake-up via WAKE terminal, also local wake-up can be disabled to reduce power consumption

- Wake-up sources identification

- Integrated protection and diagnosis increase system robustness

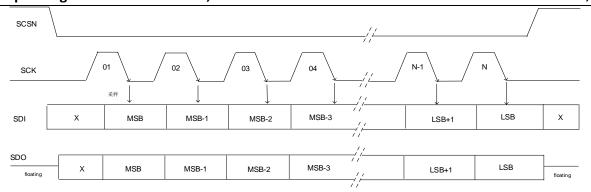

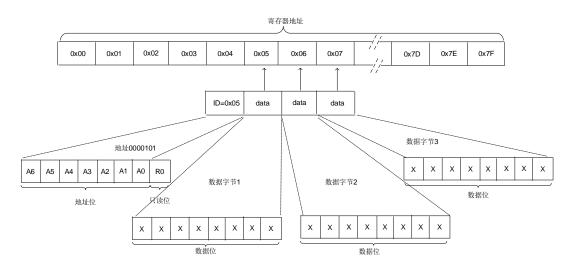

- 16/24/32 bit SPI-compatible interface for device configuration, control and events diagnosis

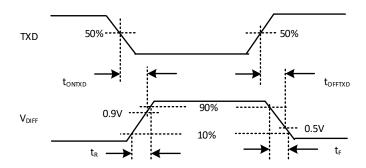

- o Transmitter dominant timeout prevents lockup

- Configurable watchdog timer

- Cyclic wake-up in watchdog timeout mode

- Overtemperature shutdown and alarm

- Undervoltage protection on BAT supply terminal

- LDO V1/LDO V2 overvoltage and undervoltage detection and protection

- Cold start-up detection (PO and NMS bits)

- Battery, WAKE and CAN bus pins protected against transients according to ISO 7637-3, test pulses 1, 2a, 3a and 3b

- Advanced system and transceiver interrupt process

- Integrated analog circuit initiate self-test (ABIST) and stuck monitoring on critical interfaces.

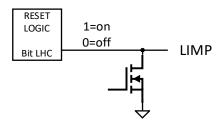

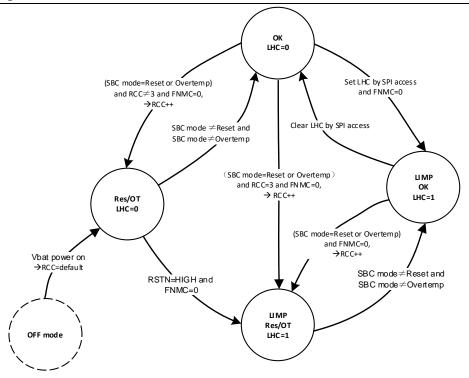

- Dedicated LIMP output to indicate system failure and guide the system into limp-home mode

- Multiple time programmable(MTP) non-Volatile(NV) memory:

- Support multiple online debugging configuration and two-times programmability

- Configurable power-up and reset behaviors and the system basis chip operating modes for different applications

- -40°C to 150°C junction temperature range

- Complies with the AEC-Q100 Grade 1 standard for automotive applications

- Available in DFN20 package (wettable flank)

### 2. Applications

- Body electronics

- Automotive lighting systems

- Advanced driver assistance systems (ADAS)

- Thermal management systems for new energy vehicles

- Automotive sensors

- In-car entertainment systems

- Automotive power train systems

### 3. General Description

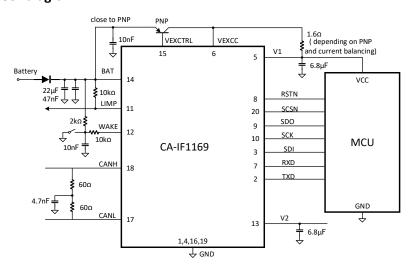

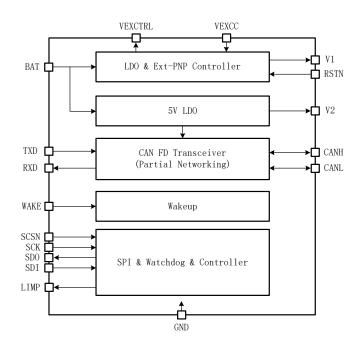

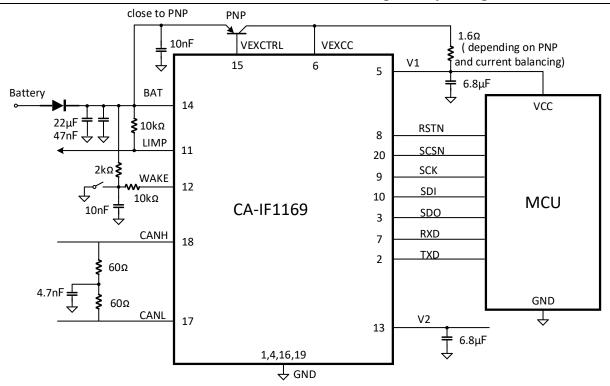

The CA-IF1169 is a system basis chip(SBC) with integrated high-speed CAN(controller area network) transceiver and dual LDOs. The CAN transceiver complies with ISO 11898-2:2016 and SAE J2284-1 to SAE J2284-5 standards for high-

speed CAN physical layer specifications, supporting up to 5 Mbit/s CAN FD communication. These devices feature up to ±42V extended fault protection on the data transmission lines in all operation modes. Also, the dominant timeout detection can prevent bus lockup caused by controller error or by a fault on the TXD input.

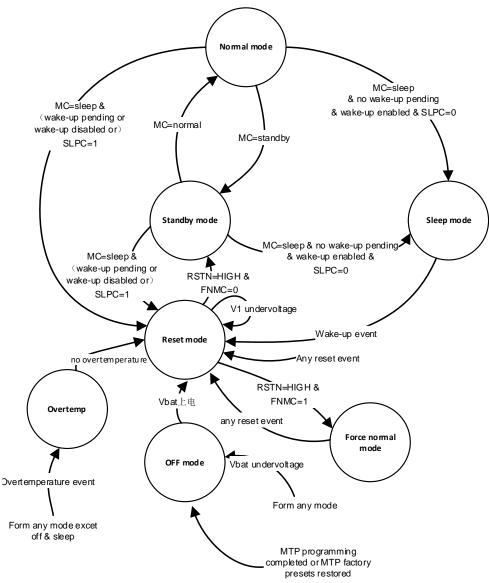

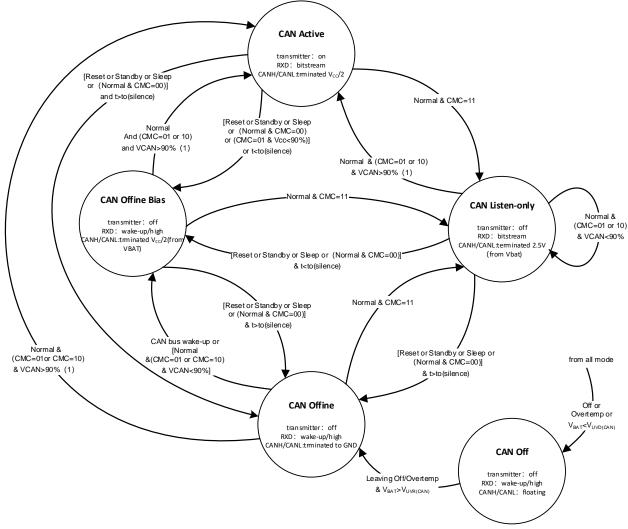

The CA-IF1169 SBC can operate in different modes: normal operation, reset mode, overtemperature protection mode, and standby/sleep modes for low current consumption. In the low-power standby and sleep modes, the CA-IF1169 supports remote wake-up (WUP) or selective wake-up frame(WUF) as defined by ISO 11898-2:2016, and local wake-up through the WAKE pin.

The CA-IF1169 integrates two low-drop voltage regulators (LDO V1 and LDO V2). LDO V1 provides 3.3V or 5V output voltage option with up to 250mA output current capability, see Table 5-1. Ordering Information. Also, its current capacity can be extended via an external PNP transistor, enabling it to power the system microcontroller or other

on-board loads. LDO V2 provides 5V output voltage with up to 100mA output current to support the internal CAN transceiver and other loads supply. Internal LDO output option simplifies the interface with 3.3V or 5.0V CAN controllers. SPI-compatible interface is available for transceiver operation control and status information reading.

The CA-IF1169 follows a comprehensive functional safety development process with integrated analog circuit initiate self-test (ABIST), critical interface monitoring. The dedicated LIMP output pin for failure indication can be used to guide the system into limp-home mode. These devices comply with ISO 26262 ASIL-B standard and support customer to achieve ASIL-B certification for their end products.

The CA-IF1169 family of devices is available in 20-pin DFN package, operates over the -55°C to +150°C junction temperature range.

### **Device Information**

| Part number      | Output voltage of V1 | Watchdog                      | Package | Package size(NOM)     |

|------------------|----------------------|-------------------------------|---------|-----------------------|

| CA-IF1169WDT-Q1  | 5V                   | Autonomous / Timeout / Window |         |                       |

| CA-IF1169VWDT-Q1 | 3.3V                 | Autonomous / Timeout / Window | DFN20   | 3.5mm x 5.5mm         |

| CA-IF1169FDT-Q1  | 5V                   | Autonomous / Timeout          | DFINZU  | 3.3111111 X 3.3111111 |

| CA-IF1169VFDT-Q1 | 3.3V                 | Autonomous / Timeout          |         |                       |

#### 4. Typical application block diagram

# 5. Ordering Information

**Table 5-1. Ordering Information**

| Part Number      | Features                      | Package size      |               |

|------------------|-------------------------------|-------------------|---------------|

| Part Number      | Recommended power supply      | Partial awakening | DFN20         |

| CA-IF1169FDT-Q1  | 5V V1 to MCU & 5V V2 to CAN   | YES               | 3.5mm x 5.5mm |

| CA-IF1169VFDT-Q1 | 3.3V V1 to MCU & 5V V2 to CAN | YES               | 3.5mm x 5.5mm |

| CA-IF1169WDT-Q1  | 5V V1 to MCU & 5V V2 to CAN   | YES               | 3.5mm x 5.5mm |

| CA-IF1169VWDT-Q1 | 3.3V V1 to MCU & 5V V2 to CAN | YES               | 3.5mm x 5.5mm |

# **Contents**

| 1.       | Features  | •••••                                  | 1  |

|----------|-----------|----------------------------------------|----|

| 2.       | Applicati | ons                                    | 1  |

| 3.       |           | Description                            |    |

| 4.       |           | pplication block diagram               |    |

| 5.       |           | Information                            |    |

| 5.<br>6. |           | History                                |    |

|          |           | -                                      |    |

| 7.       |           | guration and Functions                 |    |

| 8.       | •         | tions                                  |    |

|          | 8.1.      | Absolute Maximum Ratings <sup>1</sup>  |    |

|          | 8.2.      | ESD Ratings                            |    |

|          | 8.3.      | Recommended Operating Conditions       |    |

|          | 8.4.      | Thermal Information                    | 7  |

|          | 8.5.      | Electrical Characteristics             | 7  |

|          | 8.6.      | Dynamic Characteristics                | 11 |

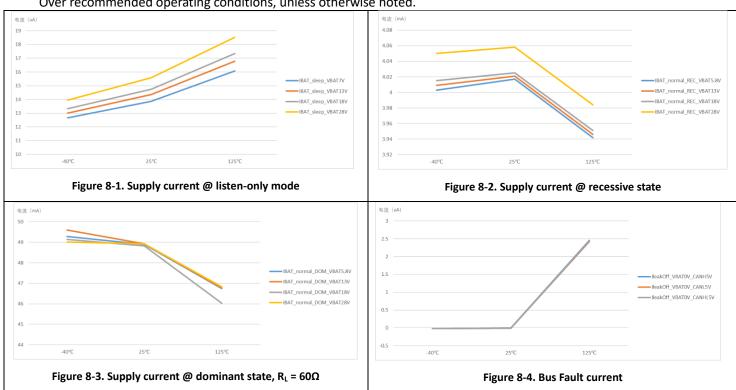

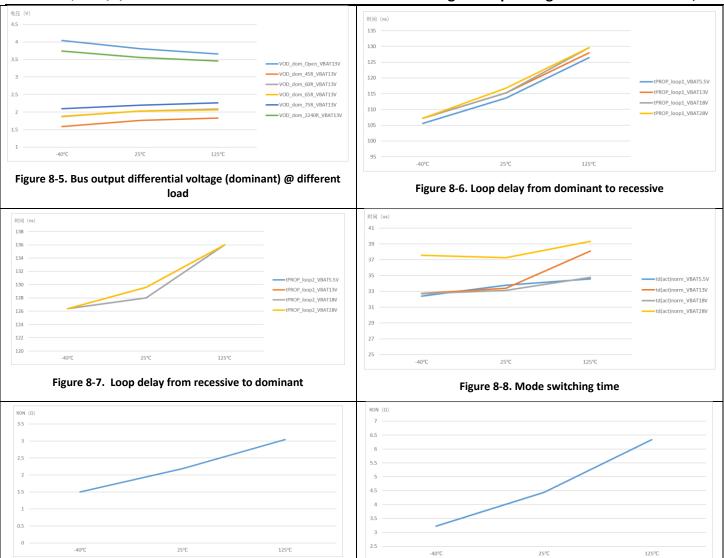

|          | 8.7.      | Typical Characteristics                | 13 |

| 9.       | Paramet   | er Measurement Information             | 15 |

| 10.      | Detailed  | Description                            | 18 |

|          | 10.1.     | Overview                               | 18 |

|          | 10.2.     | SBC Operating Modes and Control        |    |

|          | 10.2.1.   |                                        |    |

|          | 10.2.2.   | Standby Mode                           | 19 |

|          | 10.2.3.   | Sleep Mode and Protection              | 20 |

|          | 10.2.4.   | Off Mode                               | 20 |

|          | 10.2.5.   |                                        |    |

|          | 10.2.6.   | <b>-</b>                               |    |

|          | 10.2.7.   |                                        |    |

|          | 10.2.8.   | ·                                      |    |

|          | 10.2.9.   | - 7                                    |    |

|          | 10.3.     | Watchdog                               |    |

|          | 10.3.1.   | 8 1                                    |    |

|          | 10.3.2.   |                                        |    |

|          | 10.3.3.   | 8 5                                    |    |

|          | 10.3.4.   |                                        |    |

|          | 10.4.     | System Reset                           |    |

|          | 10.4.1.   |                                        |    |

|          | 10.4.2.   |                                        |    |

|          | 10.4.3.   |                                        |    |

|          | 10.5.     | Fail-safe and Functional Safety Design |    |

|          | 10.5.1.   | LIMP Output                            | 2/ |

|     | 10.5.2    |       | Transmitter-Dominant Timeout              | 29   |

|-----|-----------|-------|-------------------------------------------|------|

|     | 10.5.3    |       | Overvoltage Fault Protection              | 29   |

|     | 10.5.4    |       | Current-Limit                             | 29   |

|     | 10.5.5    |       | Floating Terminals                        |      |

|     | 10.5.6    |       | Undervoltage Lockout                      | 29   |

|     | 10.5.7    |       | Functional Safety Design                  | 30   |

|     | 10.6.     | Inter | nal Voltage Regulator                     | . 32 |

|     | 10.6.1    |       | LDO V1                                    | 32   |

|     | 10.6.2    |       | LDO V2                                    |      |

|     | 10.7.     | High  | -speed CAN Transceiver                    | . 34 |

|     | 10.7.1    |       | Receiver                                  | 34   |

|     | 10.7.2    |       | Transmitter                               |      |

|     | 10.7.3    |       | CAN Operating Modes                       |      |

|     | 10.7.4    |       | CAN Transceiver Control Register and Stat | us   |

|     | Registe   |       | 37                                        |      |

|     | 10.8.     |       | e-up Events                               |      |

|     | 10.8.1    |       | Regular Wake-up Events                    |      |

|     | 10.8.2    |       | Selective Wake-up                         | 39   |

|     | 10.9.     | CAN   | Partial Networking (CA-IF1169FDT-         |      |

|     | Q1/CA-IF1 | 169V  | FDT-Q1 only)                              | . 42 |

|     | 10.9.1    |       | CAN FD Frame Tolerance                    | 42   |

|     | 10.9.2    |       | CAN Partial Networking Configuration      |      |

|     | Registe   |       | 43                                        |      |

|     | 10.10.    | Inter | rupt and Wake-up Event Diagnosis          |      |

|     | 10.10.    | 1.    | Interrupt Sources Detection               |      |

|     | 10.10.    |       | Interrupt and Wake-up Delay               |      |

|     | 10.10.    |       | Event Status Register                     |      |

|     | 10.11.    |       | nterface                                  |      |

|     | 10.12.    | Regi  | ster Map and Configuration                |      |

|     | 10.12.    |       | Device ID                                 |      |

|     | 10.12.    |       | Lock Control Register                     |      |

|     | 10.12.    |       | Register Map                              |      |

|     | 10.12.    |       | Non volatile Memory Programming.          |      |

|     | 10.12.    |       | Register Configuration                    |      |

| 11. |           |       | nformation                                |      |

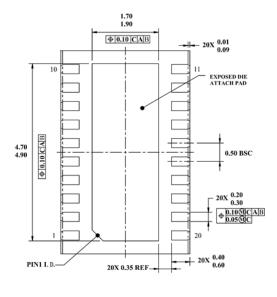

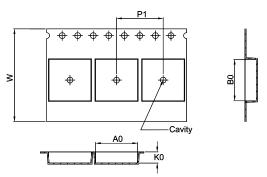

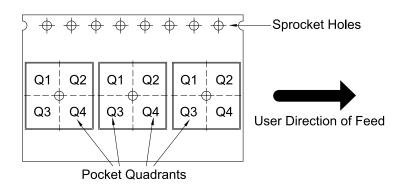

| 12. | Package   | Info  | mation                                    | .58  |

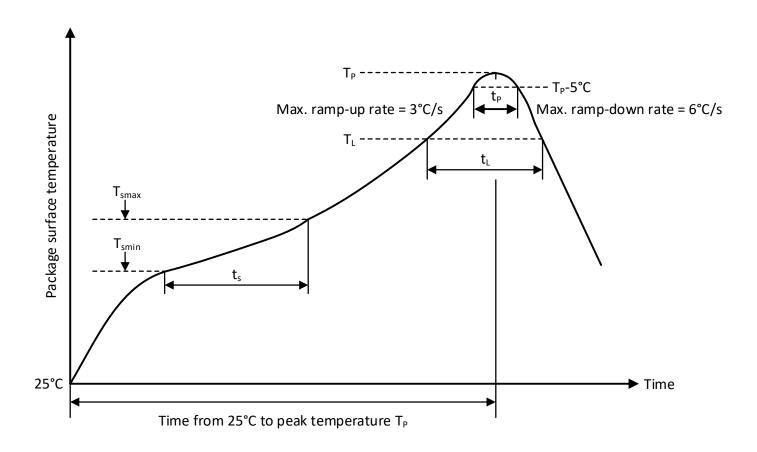

| 13. | Solderin  | g Ten | nperature (reflow) Profile                | .59  |

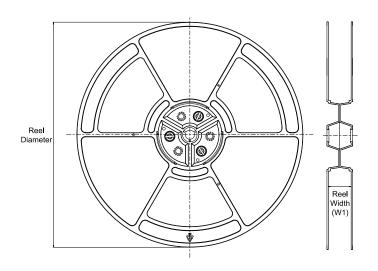

| 14. | Tape an   | d Re  | el Information                            | .60  |

| 15. | -         |       | atement                                   |      |

|     |           |       |                                           |      |

# 6. Revision History

| Revision Number | Description | Page Changed |

|-----------------|-------------|--------------|

| Ver.1.0         | NA          | 2025.7.2     |

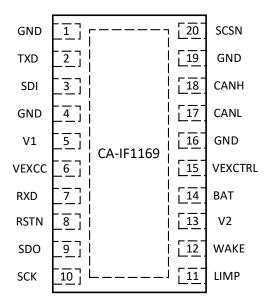

# 7. Pin Configuration and Functions

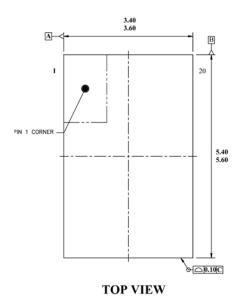

Figure 7-1. CA-IF1169 pin configuration

Table 7-1. CA-IF1169 pin configuration and description

| Pin Name | Pin#         | Туре                     | Description                                                                                                                                                                                                                                        |

|----------|--------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND      | 1, 4, 16, 19 | GND                      | Ground.                                                                                                                                                                                                                                            |

| TXD      | 2            | Digital input            | Transmit Data Input. In normal operation, drive TXD high to set the driver in the recessive state; drive TXD low to set the driver in the dominant state. TXD is a CMOS/TTL compatible input from a CAN controller with an internal pull-up to V1. |

| SDI      | 3            | Digital input            | SPI Serial Data Input. Data is clocked into SDI on the rising edge of SCK.                                                                                                                                                                         |

| V1       | 5            | Power                    | 5V or 3.3V power supply output.                                                                                                                                                                                                                    |

| VEXCC    | 6            | Analog input             | Current sense for external PNP transistor, connect VEXCC to the collector of the external PNP transistor.                                                                                                                                          |

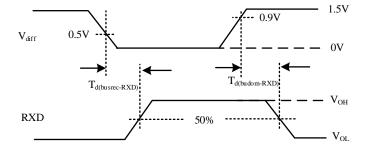

| RXD      | 7            | Digital output           | Receive Data Output. In normal operation, RXD is low for dominant bus state and high for recessive bus state. RXD is a CMOS/TTL compatible output from the bus lines CANH and CANL.                                                                |

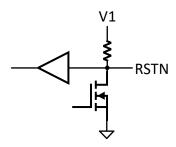

| RSTN     | 8            | Digital input<br>/output | Reset input/output, active low.                                                                                                                                                                                                                    |

| SDO      | 9            | Digital output           | SPI Serial Data Output. Data is updated on the falling edge of SCK. When SCSN is high, SDO is high-impedance.                                                                                                                                      |

| SCK      | 10           | Digital input            | SPI Serial Clock Input. SCK has internal pull-down.                                                                                                                                                                                                |

| LIMP     | 11           | Analog output            | Limp home output, active-low, open-drain output.                                                                                                                                                                                                   |

| WAKE     | 12           | High-voltage input       | Local Wake-up Input. If enabled, either a low-to-high (rising edge) or a high-to-low (falling edge) transition will generate a local wake-up event. Pull WAKE to ground to avoid unwanted wake-up events if not used.                              |

| V2       | 13           | Power                    | 5V power supply output.                                                                                                                                                                                                                            |

| BAT      | 14           | Power                    | Battery Supply Input. A bulk capacitance, typically 10µF, should be placed BAT supply with a 100nF capacitor place near the BAT terminal.                                                                                                          |

| VEXCTRL  | 15           | Analog output            | Control pin of external PNP transistor, connect VEXCTRL to the base of the external PNP transistor.                                                                                                                                                |

| CANL     | 17           | Bus I/O                  | CAN bus line low.                                                                                                                                                                                                                                  |

| CANH     | 18           | Bus I/O                  | CAN bus line high.                                                                                                                                                                                                                                 |

| SCSN     | 20           | Digital input            | SPI Chip-Select Input. Assert low to latch input states and enable the SPI interface.                                                                                                                                                              |

## 8. Specifications

# 8.1. Absolute Maximum Ratings<sup>1</sup>

|                              | PARAMETER                                                      | MIN  | MAX                  | UNIT |

|------------------------------|----------------------------------------------------------------|------|----------------------|------|

| V <sub>BAT</sub>             | Battery supply voltage range                                   | -0.3 | 42                   | V    |

| V <sub>(V1, V2)</sub>        | LDO output voltage                                             | -0.3 | 6                    | V    |

| V <sub>(VEXCC)</sub>         | Collector of the external PNP transistor connection            | -0.3 | 6                    | V    |

| V <sub>(LIMP, VEXCTRL)</sub> | LIMP, VEXCTRL voltage                                          | -0.3 | 42                   | V    |

| V <sub>BUS</sub>             | CAN bus I/O voltage range (CANH,CANL)                          | -42  | 42                   | V    |

| V <sub>(DIFF)</sub>          | Max differential voltage between CANH and CANL                 | -42  | 42                   | V    |

| V <sub>(Logic_Input)</sub>   | Logic input terminal voltage range (TXD, SDI, SCK, SCSN, RSTN) | -0.3 | V <sub>V1</sub> +0.3 | V    |

| V <sub>(Logic_Output)</sub>  | Logic output terminal voltage range (RXD, SDO )                | -0.3 | V <sub>V1</sub> +0.3 | V    |

| V <sub>(wake)</sub>          | WAKE input voltage range                                       | -0.3 | 42                   | V    |

| lo (LOGIC)                   | Logic output current (RXD)                                     |      | 4                    | mA   |

| I <sub>O (WAKE)</sub>        | WAKE output current                                            |      | 3                    | mA   |

| I <sub>I (LIMP)</sub>        | Limp mode current                                              |      | 20                   | mA   |

| T <sub>J</sub>               | Virtual junction temperature range                             | -40  | 150                  | °C   |

#### Note:

## 8.2. ESD Ratings

| Parameters                          | TES                                                                             | T CONDITIONS                                                      | VALUE | UNIT |

|-------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------|-------|------|

| CA-IF1169-Q1                        | ·                                                                               |                                                                   | •     |      |

| LIDMATCD                            | CAN bus terminals (CANH, CANL)                                                  | to GND                                                            | ±8000 | V    |

| HBM ESD                             | Other pins                                                                      |                                                                   | ±2000 |      |

| CDM ESD                             | All pins                                                                        |                                                                   | ±1500 | V    |

|                                     | CAN bus terminals (CANH,<br>CANL) to GND                                        | IEC 61000-4-2: unpowered contact discharge.                       | ±6000 | V    |

| System Level ESD                    | BAT (with 100nF capacitor ), WAKE (with 10nF capacitor and 10k resistor) to GND | IEC 61000-4-2: unpowered contact discharge.                       | ±8000 | V    |

|                                     | CAN have to week a let (CANIII                                                  | Pulse 1                                                           | -100  | V    |

| ISO7637 transient according to      | CAN bus terminals (CANH,                                                        | Pulse 2                                                           | +75   | V    |

| GIFT-ICT CAN EMC test               | CANL) to GND VBAT, WAKE terminals to GND                                        | Pulse 3a                                                          | -150  | V    |

|                                     | VBAI, WARE terrimals to GND                                                     | Pulse 3b                                                          | +100  | V    |

| ISO7637-3 transient                 | CAN bus terminals (CANH,<br>CANL) to GND<br>VBAT, WAKE terminals to GND         | Direct coupling 100nF capacitor "slow transient pulse" – powered. | ±85   | V    |

| Note: 1. Per JEDEC document JEP155. | 500V HBM allows safe manufacturing                                              | of standard FSD control process.                                  | •     | •    |

# 8.3. Recommended Operating Conditions

|                       | PARAMETER                              | MIN | MAX | UNIT |

|-----------------------|----------------------------------------|-----|-----|------|

| V <sub>BAT</sub>      | Battery supply voltage range           | 4.5 | 28  | V    |

| I <sub>OH</sub> (RXD) | RXD terminal high level output current | -2  |     | mA   |

| I <sub>OL</sub> (RXD) | RXD terminal low level output current  |     | 2   | mA   |

| T <sub>A</sub>        | Ambient temperature                    | -40 | 125 | °C   |

<sup>1.</sup> The stresses listed under "Absolute Maximum Ratings" are stress ratings only, not for functional operation condition. Exposure to absolute maximum rating conditions for extended periods may cause permanent damage to the device.

## 8.4. Thermal Information

|                 | Thermal Metric         | CA-IF1169 | UNIT |

|-----------------|------------------------|-----------|------|

|                 | Thermal Wethic         | DFN20     | UNII |

| $R_{\theta JA}$ | IC junction to ambient | 33.5      | °C/W |

### 8.5. Electrical Characteristics

Over recommended operating conditions, unless otherwise noted.

|                                 | PARAMETER                              | TEST CONDITIONS                                                                                                                  | MIN   | TYP  | MAX   | UNIT |

|---------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| Battery pov                     | ver supply                             |                                                                                                                                  |       |      |       |      |

|                                 |                                        | Normal operation: MC=111, V <sub>TXD</sub> = V <sub>V1</sub> , CAN recessive                                                     |       | 4    | 7.5   | mA   |

|                                 |                                        | Normal operation: MC=111, V <sub>TXD</sub> = 0V, CAN dominant                                                                    |       | 46   | 67    | mA   |

|                                 |                                        | Sleep mode, MC=001, CWE=1; CAN bus offline mode                                                                                  |       | 12.8 | 28    | μΑ   |

|                                 |                                        | Standby mode, MC=100, CWE=1; CAN bus offline mode                                                                                |       | 56   | 91    | μΑ   |

| I <sub>BAT</sub>                | Battery Supply Current                 | V2 turn-on                                                                                                                       |       | 8    | 32    | μΑ   |

|                                 |                                        | CAN bus offline bias mode                                                                                                        |       | 460  |       | μΑ   |

|                                 |                                        | CAN offline bias mode with active partial networking                                                                             |       | 0.0  |       | 0    |

|                                 |                                        | decoder                                                                                                                          |       | 0.9  |       | mA   |

|                                 |                                        | WAKE input current, WPRE = WPFE = 1                                                                                              |       | 1.4  | 2.5   | μΑ   |

| V <sub>th(det)pon</sub>         | BAT power-on detection                 | Rising                                                                                                                           | 4     |      | 4.9   | V    |

| V <sub>th(det)poff</sub>        | BAT power-off detection                | Falling                                                                                                                          | 2.8   |      | 3     | V    |

| V                               | BAT over-voltage (OV)                  | Dicing                                                                                                                           | 31    | 33   | 35    | V    |

| $V_{BAT(OVR)}$                  | threshold                              | Rising                                                                                                                           | 31    | 33   | 33    | _ v  |

| V <sub>BAT(OVF)</sub>           | BAT OVLO recovery                      | Falling                                                                                                                          | 29    | 31   | 33    | V    |

| V BAT(OVF)                      | voltage                                | railing                                                                                                                          | 29    | 31   | 33    | V    |

| Power supp                      | ly output (V1)                         |                                                                                                                                  |       |      |       |      |

|                                 | Output voltage                         | Vo <sub>(V1)nom</sub> =5V, VBAT =5.5V to 28V, I <sub>V1</sub> =-200mA to 0mA                                                     | 4.9   | 5    | 5.1   | V    |

|                                 |                                        | Vo <sub>(V1)nom</sub> =5V, VBAT =5.65V to 28V, I <sub>V1</sub> =-250mA to 0mA                                                    | 4.9   | 5    | 5.1   | V    |

| Vo                              |                                        | $Vo_{(V1)nom}$ =5V, VBAT < $V_{th(det)poff}$ and rising, $t \le t_{startup}$ , $Tvj \le t_{startup}$                             |       |      | 5.5   | V    |

| VO                              |                                        | 125°C                                                                                                                            |       |      | 3.3   | V    |

|                                 |                                        | Vo <sub>(V1)nom</sub> =3.3V, VBAT =3.834V to 28V, I <sub>V1</sub> =-200mA to 0mA                                                 | 3.234 | 3.3  | 3.366 | V    |

|                                 |                                        | Vo <sub>(V1)nom</sub> =3.3V, VBAT =3.984V to 28V, I <sub>V1</sub> =-250mA to 0mA                                                 | 3.234 | 3.3  | 3.366 | V    |

| ۸٧/                             | RAM retention voltage                  | VBAT = 2 V ~ 3 V; IV1 = −2 mA                                                                                                    |       |      | 100   | mV   |

| $\triangle V_{\text{ret(RAM)}}$ | difference                             | VBAT = 2 V ~ 3 V; IV1 = -200 μA                                                                                                  |       |      | 10    | mV   |

|                                 | 0                                      | 5V output version, VBAT = $2.8$ V $^{\sim}$ $5.65$ V; IV1 = $-250$ mA                                                            |       |      | 3.2   | Ω    |

| R <sub>ON(BAT-V1)</sub>         | On-resistance between                  | 3.3V output version, VBAT = 2.8 V ~ 3.90 V; IV1 = -250                                                                           |       |      | 2.2   |      |

|                                 | pin BAT and pin V1                     | mA                                                                                                                               |       |      | 3.2   | Ω    |

|                                 |                                        | 5V output version, Vuvd(nom) = 90 %                                                                                              | 4.5   |      | 4.75  | V    |

|                                 | Manual and the sec                     | 5V output version, Vuvd(nom) = 80 %                                                                                              | 4     |      | 4.25  | V    |

| $V_{uvd}$                       | V1 undervoltage<br>detection threshold | 5V output version, Vuvd(nom) = 70 %                                                                                              | 3.5   |      | 3.75  | V    |

|                                 | detection threshold                    | 5V output version, Vuvd(nom) = 60 %                                                                                              | 3     |      | 3.25  | V    |

|                                 |                                        | 3.3V output version, Vuvd(nom) = 90 %                                                                                            | 2.97  |      | 3.135 | V    |

|                                 | Under-voltage recovery                 | 5V output version                                                                                                                | 4.5   |      | 4.75  | V    |

| $V_{uvr}$                       | threshold                              | 3.3V output version                                                                                                              | 2.97  |      | 3.135 | V    |

| V                               | Over-voltage detection                 | 5V output version                                                                                                                | 5.4   |      | 5.8   |      |

| $V_{th(OVP)}$                   | and recovery threshold                 | 3.3V output version                                                                                                              | 3.45  |      | 3.7   | V    |

| I <sub>sink</sub>               | Sink current                           | VBAT = 5.65 V ~ 18 V                                                                                                             | 214   |      |       | mA   |

| I <sub>O(sc)</sub>              | Short-circuit output current           |                                                                                                                                  | -500  |      | -250  | mA   |

| I <sub>DD(CAN)intV1</sub>       | V1 supports CAN supply                 | Normal operation: MC=111, CAN active, dominant,                                                                                  |       |      | 95    | mA   |

|                                 | current <sup>1</sup>                   | $V_{TXD}$ =0V, bus shorted, $-3V < (VCANH = VCANL) < +18 V$<br>all do not support powering the CAN module through V1. This param |       |      |       |      |

Note1: CA-IF1169VFDT/FDT/WDT/VWDF-Q1 all do not support powering the CAN module through V1. This parameter is only reserved for future versions of the part number that will support CAN power supply with V1.;

# **Electrical Characteristics (continued)**

|                           | PARAMETER                                | TEST CONDITIONS                                                                                  | MIN                  | TYP | MAX                                                                                                                                          | UNIT |

|---------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------|------|

| PNP base, pir             | ı VEXCTRL                                |                                                                                                  | •                    |     |                                                                                                                                              |      |

| I <sub>O(sc)</sub>        | Short-circuit output current             | VVEXCTRL ≥ 4.5 V; VBAT = 6 V to 28 V                                                             | 4.2                  | 6.2 | 7.5                                                                                                                                          | mA   |

|                           |                                          | PDC=0                                                                                            |                      |     | 130                                                                                                                                          | mA   |

|                           | PNP turn-on threshold                    | PDC=0; Tvj = 150 °C                                                                              | 60                   | 83  | 100                                                                                                                                          | mA   |

| th(act)PNP                | current                                  | PDC =1                                                                                           |                      |     | 2 7.5 130 8 100 8 80 0 59 70 4 59 18 1 17 7.5 450 5.1 4.75 5.5 8.7 -100 95 0.4 5 0.75xV <sub>V1</sub> 0 80 0 80 0 80 0 80 0 80 0 80 0 80 0 8 | mA   |

|                           |                                          | PDC =1; Tvj = 150 °C                                                                             | 36                   | 50  |                                                                                                                                              | mA   |

|                           |                                          | PDC =0                                                                                           |                      |     | 70                                                                                                                                           | mA   |

|                           | PNP turn-off threshold                   | PDC =0; Tvj = 150 °C                                                                             | 26                   | 44  | 59                                                                                                                                           | mA   |

| th(deact)PNP              | current                                  | PDC =1                                                                                           |                      |     | 18                                                                                                                                           | mA   |

|                           |                                          | PDC =1; Tvj = 150 °C                                                                             | 6                    | 11  | 17                                                                                                                                           | mA   |

| V <sub>th(Ictrl)PNP</sub> | PNP current control threshold voltage    | Pin BAT rising edge                                                                              | 5.9                  |     | 7.5                                                                                                                                          | V    |

| PNP collector             |                                          |                                                                                                  |                      |     |                                                                                                                                              | I    |

|                           | Current-limit enable                     | Measure the voltage on the resistor between pin                                                  |                      |     |                                                                                                                                              |      |

| $V_{th(act)Ilim}$         | threshold voltage                        | VEXCC and pin V1; $2V \le V_{V1} \le 5.5 \text{ V}$ ; $6V < V_{BAT} < 28 \text{ V}$              | 300                  |     | 450                                                                                                                                          | mV   |

| V2                        |                                          |                                                                                                  | 1                    |     |                                                                                                                                              |      |

| Vo                        | Output voltage                           | VBAT = 5.8 V ~ 28 V; IV2 = −100 mA ~ 0 mA                                                        | 4.9                  | 5   | 5.1                                                                                                                                          | V    |

| $V_{\text{th(uvp)}}$      | Under-voltage protection threshold       | detection and recovery threshold                                                                 | 4.5                  |     | 4.75                                                                                                                                         | V    |

| $V_{\text{th(ovp)}}$      | Over-voltage protection threshold        | detection and recovery threshold                                                                 | 5.2                  |     | 5.5                                                                                                                                          | V    |

| R <sub>ON(BAT-V2)</sub>   | On-resistance between pin BAT and pin V2 | VBAT = 4.5 V ~ 5.8 V; IV2 = -100 mA ~ -5 mA                                                      |                      |     | 8.7                                                                                                                                          | Ω    |

| I <sub>O(sc)</sub>        | Short-circuit output current             |                                                                                                  | -250                 |     | -100                                                                                                                                         | mA   |

|                           | V2 supports CAN supply                   | Normal operation: MC=111, CAN active, dominant,                                                  |                      |     | 0.5                                                                                                                                          | 1    |

| DD(CAN)intV2              | current                                  | $V_{TXD}$ =0V, bus shorted, -3V < (VCANH = VCANL) < +18 V                                        |                      |     | 95                                                                                                                                           | mA   |

| Limp-home o               | utput: LIMP                              |                                                                                                  |                      |     |                                                                                                                                              |      |

| Vo                        | Output voltage                           | ILIMP = 0.8 mA; LHC = 1; Tvj = $-40  ^{\circ}\text{C}  ^{\sim}\text{T}_{\text{th(act)otp(max)}}$ |                      |     | 0.4                                                                                                                                          | V    |

| I <sub>LO</sub>           | Output leakage current                   | VLIMP = 0 V ~ 28 V; LHC = 0                                                                      | -5                   |     | 5                                                                                                                                            | μΑ   |

| Logic interfac            | e (SDI, SCK, SCSN inputs)                |                                                                                                  |                      |     |                                                                                                                                              |      |

| V <sub>th (sw)</sub>      | Switching threshold voltage              |                                                                                                  | 0.25xV <sub>V1</sub> |     | 0.75xV <sub>V1</sub>                                                                                                                         | V    |

| Vth(sw)hys                | Switching threshold voltage hysteresis   |                                                                                                  | 0.05xV <sub>V1</sub> |     |                                                                                                                                              | V    |

| R <sub>pd(SCK)</sub>      | SCK pull-down resistance                 |                                                                                                  | 40                   | 60  | 80                                                                                                                                           | kΩ   |

| R <sub>pd(SCSN)</sub>     | SCSN pull-up resistance                  |                                                                                                  | 40                   | 60  | 80                                                                                                                                           | kΩ   |

| R <sub>pd(SDI)</sub>      | SDI pull-down resistance                 | $V_{SDI} < V_{th(sw)}$                                                                           | 40                   | 60  | 80                                                                                                                                           | kΩ   |

| R <sub>pu(SDI)</sub>      | SDI pull-up resistance                   | V <sub>SDI</sub> >V <sub>th(sw)</sub>                                                            | 40                   | 60  | 80                                                                                                                                           | kΩ   |

| C <sub>i</sub>            | Input capacitance <sup>1</sup>           | $V_i = V_{v1}$                                                                                   |                      | 3   | 6                                                                                                                                            | pF   |

| Logic output              | (SDO output)                             |                                                                                                  |                      |     |                                                                                                                                              | •    |

| V <sub>OH</sub>           | High-level output voltage                | I <sub>oH</sub> =-4mA,                                                                           | V <sub>V1</sub> -0.4 |     |                                                                                                                                              | V    |

| V <sub>OL</sub>           | Low-level output voltage                 | I <sub>oL</sub> =+4mA,                                                                           |                      | •   | 0.4                                                                                                                                          | V    |

| I <sub>LO(off)</sub>      | Output leakage current @                 | V <sub>SCSN</sub> =V <sub>V1</sub> , Vo=0V to V <sub>V1</sub>                                    | -5                   |     | Е                                                                                                                                            | ι, Λ |

|                           | off mode                                 |                                                                                                  | -5                   |     | <u> </u>                                                                                                                                     | μΑ   |

| Co                        | Output capacitance <sup>2</sup>          | SCSN = V <sub>V1</sub>                                                                           |                      | 3   | 6                                                                                                                                            | pF   |

|                           | ested in production; guaranteed          | by design.                                                                                       |                      |     |                                                                                                                                              |      |

| Logic interfac            | e (TXD input)                            |                                                                                                  |                      |     |                                                                                                                                              |      |

| $V_{th (SW)}$             | Switching threshold voltage              |                                                                                                  | 0.25xV <sub>V1</sub> |     | 0.75x V <sub>V1</sub>                                                                                                                        | V    |

| Vth(sw)hys                | Switching threshold voltage hysteresis   |                                                                                                  | 0.05xV <sub>V1</sub> |     |                                                                                                                                              | V    |

| R <sub>pu(TXD)</sub>      | TXD pull-up resistance                   |                                                                                                  | 40                   | 60  | 80                                                                                                                                           | kΩ   |

# **Electrical Characteristics (continued)**

|                         | PARAMETER                                  | TEST CONDITIONS                                                                                             | MIN                  | ТҮР                  | MAX                  | UNI<br>T |

|-------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|----------|

| Logic inter             | face (RXD output)                          |                                                                                                             |                      |                      |                      |          |

| V <sub>OH</sub>         | High-level output voltage                  | Io = -4mA                                                                                                   | V <sub>V1</sub> -0.4 |                      |                      | V        |

| V <sub>OL</sub>         | Low-level output voltage                   | Io = +4mA                                                                                                   |                      |                      | 0.4                  | V        |

| R <sub>pu(RXD)</sub>    | RXD pull-up resistance                     | CAN offline mode                                                                                            | 40                   | 60                   | 80                   | kΩ       |

|                         | rface (WAKE input)                         | I .                                                                                                         |                      |                      |                      |          |

| V <sub>th(sw)r</sub>    | High-level input voltage                   |                                                                                                             | 2.8                  | 3.5                  | 4.1                  | V        |

| V <sub>th(sw)f</sub>    | Low-level input voltage                    |                                                                                                             | 2.4                  | 3.1                  | 3.75                 | V        |

| V <sub>hys(i)</sub>     | Input threshold hysteresis                 |                                                                                                             | 250                  | 400                  | 800                  | mV       |

| l <sub>i</sub>          | Low-level input leakage current            | Tvj = -40 °C to +85 °C                                                                                      |                      |                      | 1.5                  | μА       |

| CAN bus di              | river                                      |                                                                                                             |                      |                      |                      | -        |

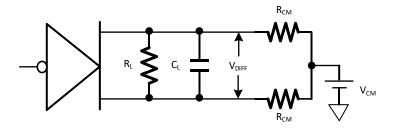

|                         | Bus output voltage                         | TXD=Low, RL=50 -65Ohm, CANH, see Figure 9-1                                                                 | 2.75                 | 3.5                  | 4.5                  | V        |

| $V_{O(DOM)}$            | (dominant)                                 | TXD=Low, RL=50 -650hm, CANL, see Figure 9-1                                                                 | 0.5                  | 1.5                  | 2.25                 | V        |

|                         |                                            | TXD=Low, RL=45-70 Ohm, RCM open, see Figure                                                                 | 4.5                  |                      | 2                    | T.,      |

|                         | Bus output differential                    | 9-1                                                                                                         | 1.5                  |                      | 3                    | V        |

| V <sub>O(DOM)</sub>     | voltage (dominant)                         | TXD=Low, RL=2240 Ohm, RCM open, see Figure                                                                  | 4.5                  |                      | F                    |          |

|                         |                                            | 9-1                                                                                                         | 1.5                  |                      | 5                    | V        |

|                         |                                            | CAN active, TXD=High, no load, CANH/CANL, see                                                               | 2                    | 0.5.4                | 2                    | V        |

|                         |                                            | Figure 9-1                                                                                                  | 2                    | 0.5xV <sub>CAN</sub> | 3                    | \ \      |

| V <sub>O(REC)</sub>     | Bus output voltage                         | CAN offline bias/listen-only mode, TXD=High, no                                                             | 2                    | 2.5                  | 3                    | V        |

| V O(REC)                | (recessive)                                | load, CANH/CANL, see Figure 9-1                                                                             | 2                    | 2.5                  | 3                    | V        |

|                         |                                            | CAN offline mode, TXD=High, no load, CANH/CANL,                                                             | -0.1                 |                      | 0.1                  | V        |

|                         |                                            | see Figure 9-1                                                                                              | -0.1                 |                      | 0.1                  | V        |

|                         |                                            | CAN active/offline bias/listen-only mode,                                                                   | -50                  |                      | 50                   | mV       |

| V <sub>OD(REC)</sub>    | Bus output differential                    | TXD=High, no load, CANH/CANL, see Figure 9-1                                                                | 30                   |                      | 30                   | 111.0    |

| V OD(REC)               | voltage (recessive)                        | CAN offline mode, TXD=High, no load, CANH/CANL,                                                             | -200                 |                      | 200                  | mV       |

|                         |                                            | see Figure 9-1                                                                                              | 200                  | <del> </del>         | 200                  |          |

|                         | Short-circuit current                      | TXD=Low, CANL open, CANH from -15V to 27V, see 错误!未找到引用源。                                                   | -90                  |                      | 6                    | mA       |

| los(ss_dom)             | (dominant)                                 | TXD=Low, C ANH open, CANL from -15V to 27V, see                                                             | -6                   |                      | 90                   | mA       |

|                         |                                            | 错误!未找到引用源。                                                                                                  | Ĭ                    |                      |                      |          |

| I <sub>OS(SS_REC)</sub> | Short-circuit current (recessive)          | TXD=High, VBUS from -27V to 32V, see 错误!未找到引用源。                                                             | -3                   |                      | 3                    | mA       |

| V <sub>sym</sub>        | Transient symmetry                         | RL=60 Ohm, C <sub>split</sub> =4.7nF, RCM open, TXD=250kHz,                                                 | 0.9xV <sub>CAN</sub> |                      | 1.1xV <sub>CAN</sub> | V        |

| ▼ sym                   | (dominant or recessive)                    | 1MHz, 2.5MHz, V <sub>sym</sub> =V <sub>CANH</sub> +V <sub>CANL</sub>                                        | O.3X V CAN           |                      | 1.1 V CAN            | , v      |

| $V_{\text{sym\_dc}}$    | DC Output symmetry (dominant or recessive) | RL=60 Ohm, R <sub>CM</sub> open, V <sub>sym_dc</sub> =V <sub>CC</sub> -V <sub>CANH</sub> -V <sub>CANL</sub> | -0.4                 |                      | 0.4                  | V        |

# **Electrical Characteristics (continued)**

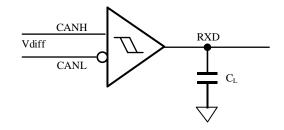

| CAN receiver (TXD = High, CANH/CANL drive externally)           V <sub>CM</sub> Common-mode input range         Normal mode/standby mode, RXD output vaild, see Figure 9-2         -12         +12         V           V <sub>IT</sub> Input threshold voltage at active/listen-only modes         Vcm from -12V to 12V, see Figure 9-2         500         900         mV           V <sub>ITSIB</sub> Input threshold voltage at offline mode         Vcm from -12V to 12V, see Figure 9-2         400         1150         mV           V <sub>ITSIB</sub> Input differential threshold voltage at normal/listen-only modes (recessive)         Vcm from -12V to 12V, see Figure 9-2         0.9         9         V           V <sub>CHF_DSTB</sub> Input differential threshold voltage at a offline mode (avoitage at a offline mode (avoitage at offline mode (avoitage at offline mode (recessive)         Vcm from -12V to 12V, see Figure 9-2         1.15         9         V           V <sub>CHF_DSTB</sub> (NSTB)         Differential prior threshold hysteresis         Normal mode         Vcm from -12V to 12V, see Figure 9-2         -4         0.4         V           V <sub>CHF_DSTB</sub> (NSTB)         Differential input threshold hysteresis         Normal mode (recessive)         Vcm from -12V to 12V, see Figure 9-2         -4         0.4         V           V <sub>CHF_DSTB</sub> (NSTB)         Input differential threshold hysteresis         Normal mode (recessive)         Normal mode (recessive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Overree                  | commended operating condition                   |                                          |      |     |                     | UNI |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------|------------------------------------------|------|-----|---------------------|-----|

| Volume         Common-mode input range         Normal mode/standby mode, RXD output         -12         ±12         V           V <sub>T1</sub> Input threshold voltage at active/listen-only modes         Vcm from -12V to 12V, see Figure 9-2         500         900         mV           V <sub>T(XTR)</sub> Input threshold voltage at offline mode         Vcm from -12V to 12V, see Figure 9-2         400         1150         mV           V <sub>PR1,D</sub> woltage at normal/listen-only modes (dominant) input differential threshold voltage at normal/listen-only modes (recessive) input differential threshold voltage at offline mode (dominant) input differential threshold voltage at offline mode (dominant) input differential threshold voltage at offline mode (freessive) input differential threshold voltage at offline mode (freessive) input differential threshold voltage at offline mode (freessive) input differential threshold hysteresis         Vcm from -12V to 12V, see Figure 9-2         1.15         9         V           Vorz_JINSTIN         Input differential threshold voltage at offline mode (freessive) input differential threshold hysteresis         Vcm from -12V to 12V, see Figure 9-2         -4         0.4         V           Vorz_JINSTIN         Input differential threshold hysteresis         Normal mode         100         mW           Vorz_JINSTIN         Input differential threshold hysteresis         Normal mode         100         mW         W           Vorz_JINSTIN         Input capacital threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          | PARAMETER                                       | TEST CONDITIONS                          | MIN  | TYP | MAX                 | Т   |

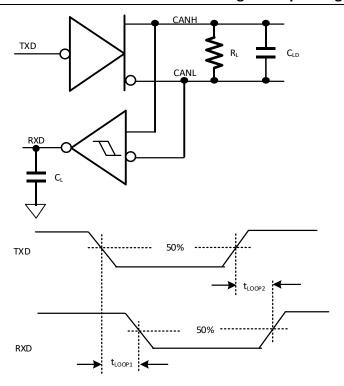

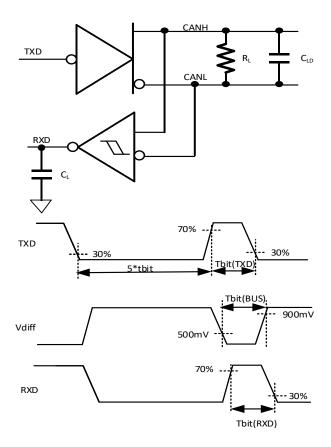

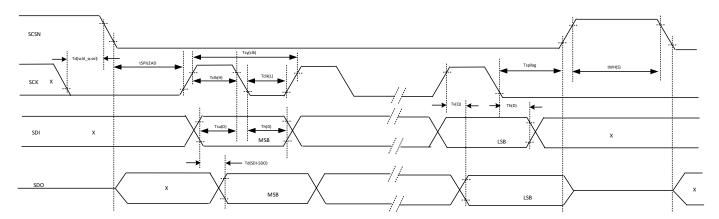

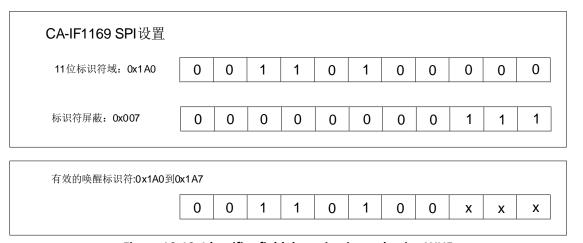

| Var   Input threshold voltage at active/[inser-nohy modes   Vcm from -12V to 12V, see Figure 9-2   500   900   mV   mode   Mcm from -12V to 12V, see Figure 9-2   400   1150   mV   mode   Mcm from -12V to 12V, see Figure 9-2   400   1150   mV   mode   Mcm from -12V to 12V, see Figure 9-2   400   1150   mV   Mcm from -12V to 12V, see Figure 9-2   400   90   V   Mcm from -12V to 12V, see Figure 9-2   400   90   V   Mcm from -12V to 12V, see Figure 9-2   400   90   V   Mcm from -12V to 12V, see Figure 9-2   400   90   V   Mcm from -12V to 12V, see Figure 9-2   400   90   V   Mcm from -12V to 12V, see Figure 9-2   400   400   400   Mcm from -12V to 12V, see Figure 9-2   400   400   400   Mcm from -12V to 12V, see Figure 9-2   400   400   400   Mcm from -12V to 12V, see Figure 9-2   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   400   4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CAN receive              | r (TXD = High, CANH/CANL drive exte             | ernally)                                 |      |     |                     |     |